文章目录

- 同步和异步

- 同步复位、异步复位、同步释放

- 同步复位

- 异步复位

- 同步释放(异步信号和CLK信号存在时序检查、Recover time&Removel time)

- 典型的异步复位同步释放的verilog电路设计

同步和异步

-

数字电路根据逻辑功能的不同特点,可以分成两大类:一类叫做组合逻辑电路,简称组合电路或组合逻辑;另一类叫做时序逻辑电路,简称时序电路或时序逻辑。

- 如果数字电路满足任意时刻的输出仅仅取决于该时刻的输入,那么该数字电路为组合逻辑电路。

- 相反,如果数字电路任意时刻的输出不仅取决于当前时刻的输入,而且还取决于数字电路原来的状态,那么该数字电路为时序逻辑电路

-

这里和状态机分类有点像,Moore型的输出只与当前状态有关,而Mealy型的输出还与输入相关

数电从电路的功能把电路分为两类,组合电路和时序电路(同步时序电路、异步时序电路)

- 组合逻辑容易产生竞争冒险

- 同步时序电路:

Verilog中根据是否受同一个时钟控制把电路分为两类:同步时序电路和异步时序电路

-

同步电路:

- 电路中所有信号都受同一个时钟控制的

- 电路中有多个时钟,但是其相位差是恒定的,也认为是同步电路

- 所有触发器都在同一个时钟控制下完成、所有触发器的触发方式(沿触发/电平触发)和种类完全一致

-

异步电路

- 电路中有不受时钟控制的信号

- 电路中有多个时钟,但是其相位差不是恒定的,是异步电路

-

同步动作:所有的信号都在一个时钟下控制

-

异步动作:敏感信号列表中有不受时钟控制的其他信号,要遍历clock信号和(reset)异步信号,并且(reset)异步信号级别比clock信号高

同步复位、异步复位、同步释放

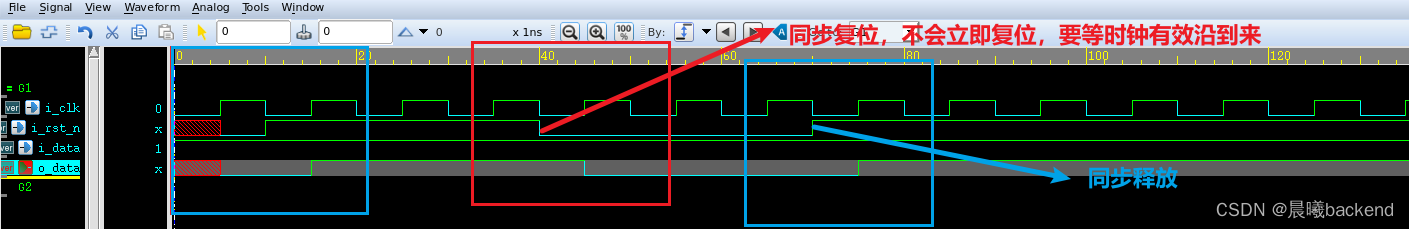

同步复位

- 复位信号只在时钟上升沿到来时才有效;

- 能够有效滤除高于时钟频率的毛刺;

- 同步复位的优点在于它只在时钟信号clk的上升沿触发进行系统是否复位的判断,这降低了亚稳态出现的概率

- 复位信号的有效时间必须大于时钟周期才可以检测到复位

- 与异步复位相比,电路多使用一个

选择器,需要消耗更多的器件资源

module sync_reset(

input i_clk,

input i_rst_n,

input i_data,

output reg o_data

);

always @(posedge i_clk)

if(!i_rst_n)

o_data <= 1'b0;

else

o_data <= i_data;

endmodule

异步复位

- 无论时钟有效沿是否有效,只要复位信号到来,立即执行复位操作

- 复位信号释放时,如果不满足时序要求,可能由复位引入亚稳态

- 采用异步复位的端口无需额外增加器件资源的消耗,直接利用触发器的异步复位端,节省资源

module async_reset(

input i_clk,

input i_rst_n,

input i_data,

output reg o_data

);

always @(posedge i_clk or negedge i_rst_n)

if(!i_rst_n)

o_data <= 1'b0;

else

o_data <= i_data;

endmodule

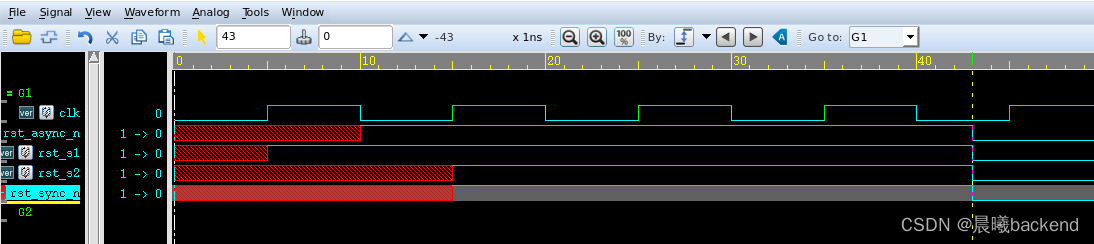

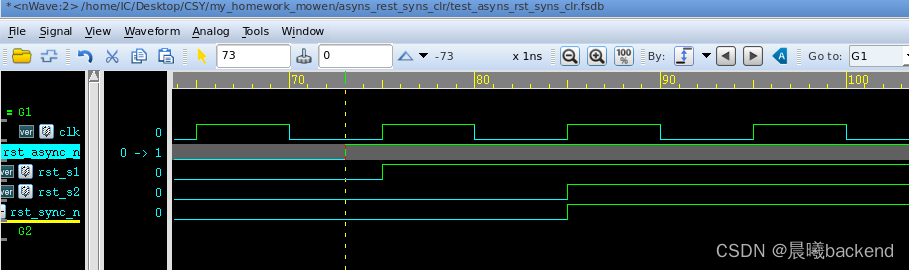

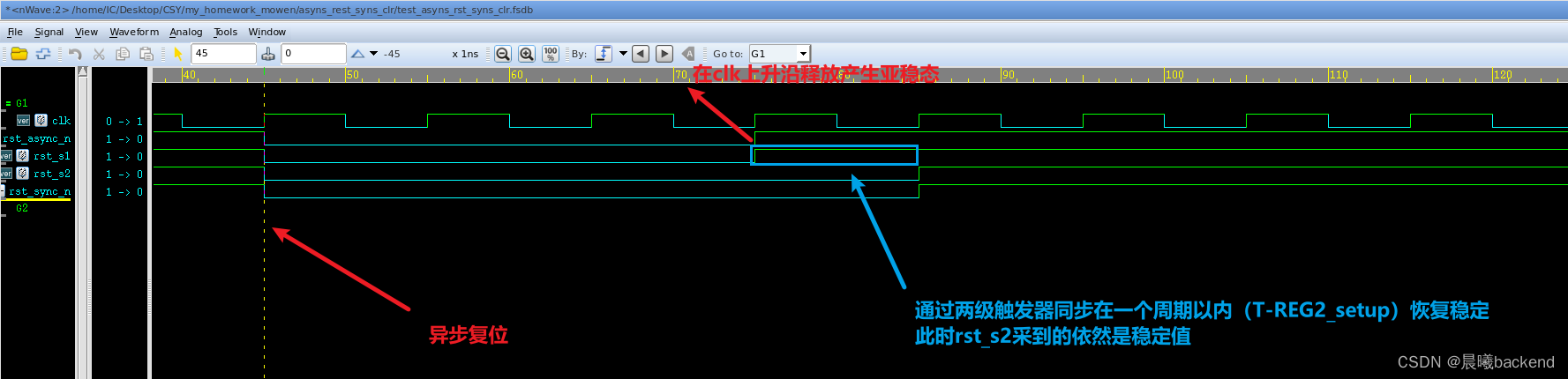

同步释放(异步信号和CLK信号存在时序检查、Recover time&Removel time)

- 如果复位信号正好在时钟信号的有效沿撤销,这时候的输出就是亚稳态

- 使用两级触发器同步释放(留一个周期的裕量),大大减小亚稳态出现的概率,万一出现亚稳态只要在(周期T-Tsetup)这个时间恢复稳定即可

- 两级触发器同步后,第二级触发器的输出基本上是稳定值。后续逻辑根据稳定值,会有稳定的行为。这就是追求的系统稳定性。

- 异步复位、同步释放其最显著特征是既保留了异步复位的功能,又避免了异步复位释放时所面临的recovery或者removal违例问题

module reset_gen (

output rst_sync_n,

input clk, rst_async_n);

reg rst_s1, rst_s2;

always @(posedge clk, negedge rst_async_n)

if (!rst_async_n) begin

rst_s1 <= 1'b0;

rst_s2 <= 1'b0;

end

else begin

rst_s1 <= 1'b1;

rst_s2 <= rst_s1;

end

assign rst_sync_n = rst_s2;

endmodule

- 如上图所示,低电平有效的异步复位信号

rst_async_n变为低电平时,将导致触发器清零,使得连接至rst_sync_n的系统触发器清零

- 然后,当

rst_async_n解除复位(变为高电平)时,第一个触发器对输入的VCC信号进行同步输出rst_s1为VCC,再经过第二个触发器同步后移除复位信号rst_sync_n

-

我们在Gvim中更改了代码,VCS编译后,Verdi中还是旧的代码,这时候在Verdi中进行刷新

(shift+L),新的代码以及波形图都会在Veridi中更新 -

假设

rst_async_n在clk的上升沿时撤除,那么第一级触发器处于亚稳态,但是由于两级触发器的缓冲作用,第二级触发器的输入为clk到来前第一级触发器的输出,即为低电平。因此,此时第二级触发器的输出一定是稳定的低电平,方框左中触发器仍然处于复位状态。在下一个clk到来时,第一级触发器的输出已经是稳定的高电平了,故rst_sync_n已经是稳定的高电平,此时复位释放,也就是同步释放。

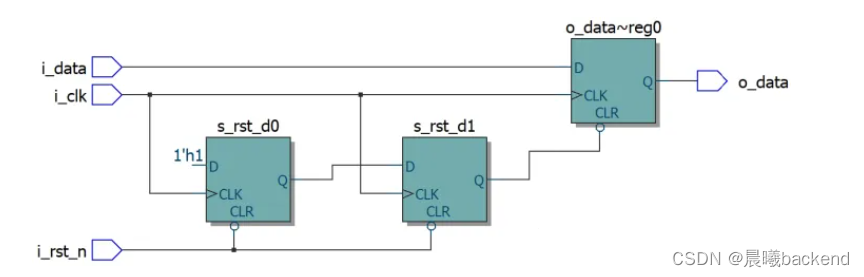

典型的异步复位同步释放的verilog电路设计

- 保证输出

s_rst_d1时稳定的

module async_reset_sync_done(

input i_clk,

input i_rst_n,

input i_data,

output reg o_data

);

reg s_rst_d0;

reg s_rst_d1;

always @(posedge i_clk or negedge i_rst_n)

if(!i_rst_n)

begin

s_rst_d0 <= 1'b0;

s_rst_d1 <= 1'b0;

end

else

begin

s_rst_d0 <= 1'b1;

s_rst_d1 <= s_rst_d0;

end

always @(posedge i_clk or negedge s_rst_d1)

if(!s_rst_d1)

o_data <= 1'b0;

else

o_data <= i_data;

endmodule

![[Windows] ImageGlass Kobe v8.9便携版](https://img-blog.csdnimg.cn/img_convert/4125322071497e5a2bb7a2f59afec0d5.jpeg)