目录

概要

整体架构流程

技术名词解释

技术细节

1.环路滤波器采用有源滤波器还是无源滤波器?、

2.如何设计 VCO 输出功率分配器?、

3.如何设置电荷泵的极性?

4.锁定指示电路如何设计?

小结

概要

提示:这里可以添加技术概要

锁相环是一种反馈系统,其中电压控制振荡器(VCO) 和相位比较器相互连接,使得振荡器 可以相对于参考信号维持恒定的相位角度。锁相环可用来从固定的低频信号生成稳定的 输出高频信号等

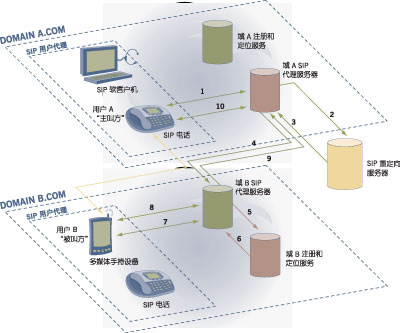

整体架构流程

提示:这里可以添加技术整体架构

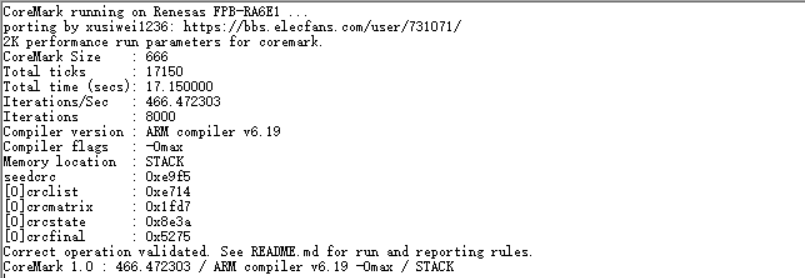

PLL 的基本模块为误差检波器(由鉴频鉴相器和电荷泵组成)、环路滤波器、VCO 和反馈分 频器。负反馈强制误差信号 e(s) 在反馈分频器输出和基准频率处于锁相和锁频状态且 FO=NFREF 的点处接近 0。 根据图 ,当系统使用 PLL 来生成高于输入的频率时,VCO 会以角频率ωO 振荡。该信 号的一部分会通过分频器以 1/N 的比率回馈到误差检波器。这种经过分频的频率会馈入误差检 波器的其中一个输入端。本例中,另一路输入为固定参考信号。误差检波器会比较两个输入端 的信号。这两个信号输入的相位和频率相等时,误差为常数,环路则处于“锁定”条件下。

技术名词解释

提示:这里可以添加技术名词解释

技术细节

提示:这里可以添加技术细节

1.环路滤波器采用有源滤波器还是无源滤波器?、

有源滤波器因为采用放大器而引入噪声,所以采用有源滤波器的 PLL 产生的频率的相 位噪声性能会比采用无源滤波器的 PLL 输出差。因此在设计中我们尽量选用无源滤波器。 其中三阶无源滤波器是最常用的一种结构。PLL 频率合成器的电荷泵电压 Vp 一般取 5V 或 者稍高,电荷泵电流通过环路滤波器积分后的最大控制电压低于 Vp 或者接近 Vp。如果 VCO/VCXO 的控制电压在此范围之内,无源滤波器完全能够胜任。

当 VCO/VCXO 的控制电压超出了 Vp,或者非常接近 Vp 的时候,就需要用有源滤波 器。在对环路误差信号进行滤波的同时,也提供一定的增益,从而调整VCO/VCXO 控制电 压到合适的范围

低失调电压(Low Offset Voltage) [通常小于 500uV]

低偏流(Low Bias Current) [通常小于 50pA]

如果是单电源供电,需要考虑使用轨到轨(Rail-to-Rail)输出型放大器。

2.如何设计 VCO 输出功率分配器?、

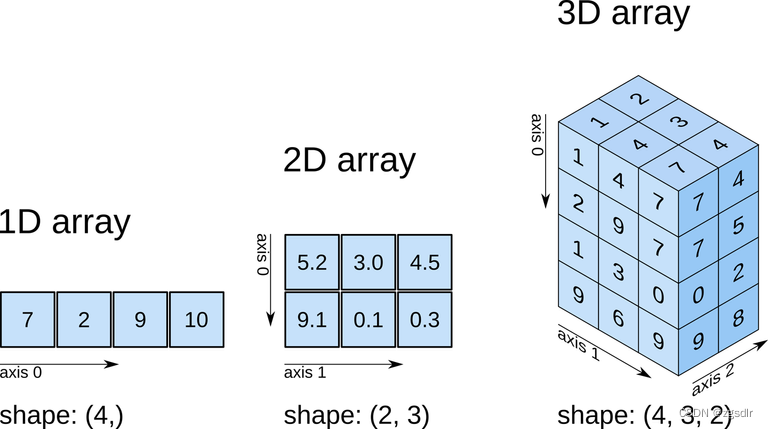

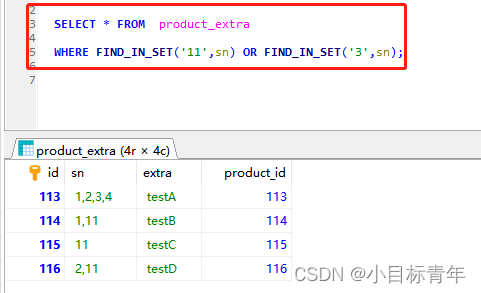

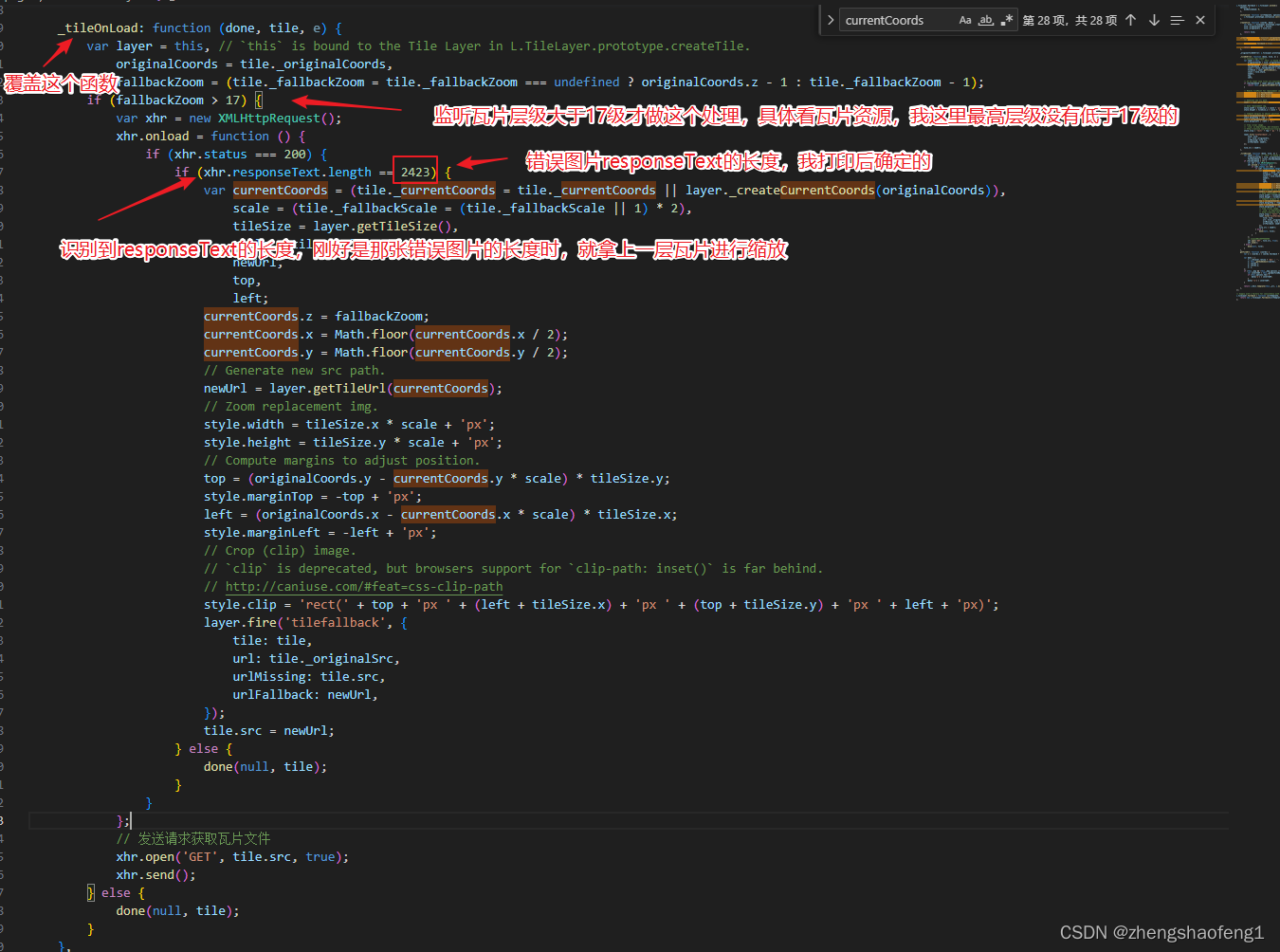

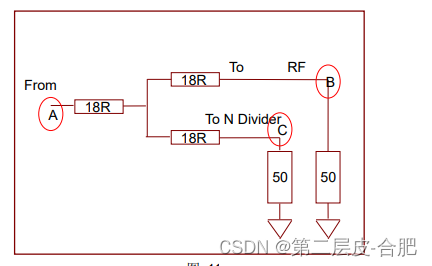

选择 VCO 时,尽量选择 VCO 的输出频率对应的控制电压在可用调谐电压范围的中点。 选用低控制电压的 VCO 可以简化 PLL 设计。 VCO 的输出通过一个简单的电阻分配网络来完成功率分配。从 VCO 的输出看到电阻网络的阻 抗为 18+(18+50)//(18+50)=52ohm。形成与 VCO 的输出阻抗匹配。下图中 ABC 三点功率关系。 B,C 点的功率比 A 点小 6dB。

3.如何设置电荷泵的极性?

在下列情况下,电荷泵的极性为正。

环路滤波器为无源滤波器,VCO 的控制灵敏度为正(即,随着控制电压的升高,输出频率增 大)。

在下列情况下,电荷泵的极性为负。

环路滤波器为有源滤波器,并且放大环节为反相放大;VCO 的控制灵敏度为正。

环路滤波器为无源滤波器,VCO 的控制灵敏度为负。

PLL 分频应用,滤波器为无源型。即参考信号直接 RF 反馈分频输入端,VCO 反馈到参考输 入的情况

4.锁定指示电路如何设计?

PLL 锁定指示分为模拟锁定指示和数字锁定指示两种

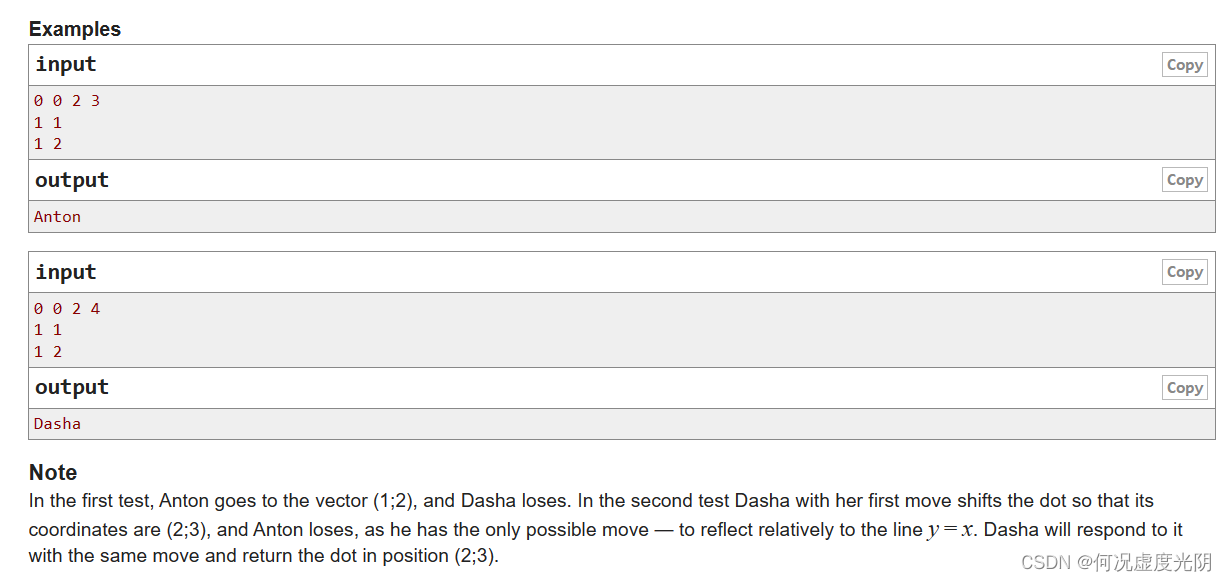

数字锁定指示: 当 PFD 的输入端连续检测到相位误差小于 15ns 的次数为 3(5)次,那么 PLL 就会给出数字锁定

数字锁定指示的工作频率范围:通常为 5kHz~50MHz。在更低的 PFD 频率上,漏电流会触发锁 定指示电路;在更高的频率上,15ns 的时间裕度不再适合。在数字锁定指示的工作频段范围之 外,推荐使用模拟锁定指示。

模拟锁定指示: 对电荷泵输入端的 Up 脉冲和 Down 脉冲进行异或处理后得出的脉冲串。所以当锁定时,锁定指 示电路的输出为带窄负脉冲串的高电平信号。图为一个典型的模拟锁定指示输出(MUXOUT 输 出端单独加上拉电阻的情况)。

模拟锁定指示的输出级为 N 沟道开漏结构,需要外接上拉电阻,通常为 10KOhm~160kohm。我 们可以通过一个积分电路(低通滤波器)得到一个平坦的高电平输出,如图所是的蓝色框电路。

小结

提示:这里可以添加总结

误锁定的一个条件: 参考信号 REFIN 信号丢失。当 REFIN 信号与 PLL频合器断开连接时,PLL显然会失锁;然而, ADF41xx 系列的 PLL,其数字锁定指示用 REFIN 时钟来检查是否锁定,如果 PLL 先前已经锁 定,REFIN 时钟突然丢失,PLL 会继续显示锁定状态。解决方法是使用模拟锁定指示。