目录

第一章 计算机系统概论

1.1 冯诺依曼型计算机

1.2 计算机的硬件组成

第二章 运算方法和运算器

2.1 ieee754标准、32位浮点数

2.2 补码运算

2.3 运算器的基本结构形式

第三章 存储系统

3.1 主存与cache的地址映射

3.1.1 全相联映射方式

3.1.2 直接映射方式

3.1.3 组相联映射方式

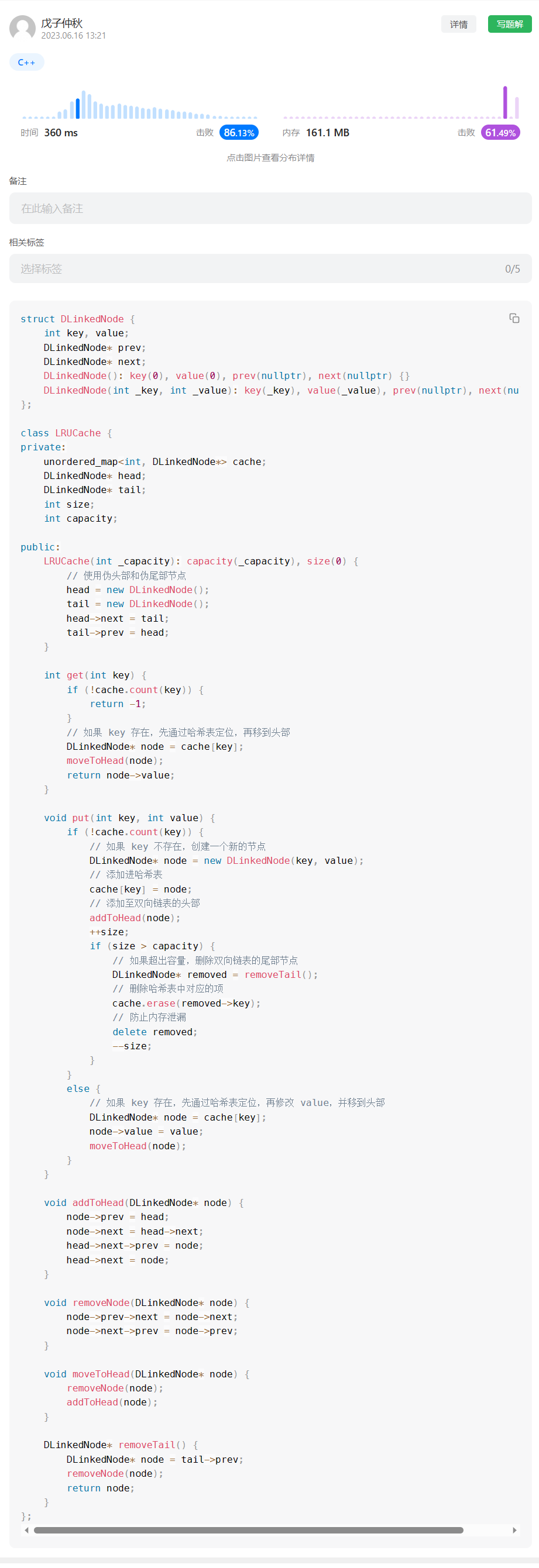

3.2 cache替换策略

第四章 指令系统

4.1 基本寻址方式

4.2 精简指令系统RISC

第五章 中央处理器

5.1 cpu中的主要寄存器

5.2 流水cpu

第六章 总线系统

6.1 当代总线内部结构

第七章 外围设备

第八章 输入输出系统

8.1 程序中断

本复习大纲基于白中英主编第六版计算机组成原理教材。

题型划分:简答题:7*6'=42';计算题:8+10=18;分析设计:10+15=25;论述题:15,共100分

第一章 计算机系统概论

1.1 冯诺依曼型计算机

- 存储程序

- 按地址自动执行

- 五大部件:控制器、运算器、存储器、io设备

- 以运算器为中心

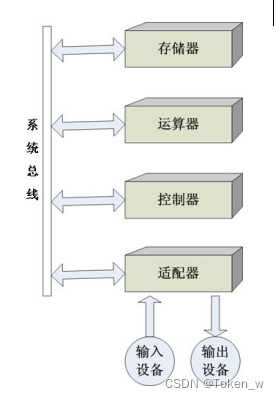

1.2 计算机的硬件组成

各部件作用分析:

- 运算器:算术运算和逻辑运算,在计算机中参与运算的数是二进制的,运算器的长度一般是8、16、32或64位的

- 存储器:存储数据和程序(指令)

- 控制器:自动控制整个计算的过程,按照一定的顺序一条接着一条取指令、指令译码、执行指令。

- 适配器:使得被连接的外围设备通过系统总线与主机进行联系

- io设备:原始数据输入设备,计算机运算结果显示设备

- 总线:构成计算机系统的骨架,多个系统部件之间进行数据传送的公共通路

第二章 运算方法和运算器

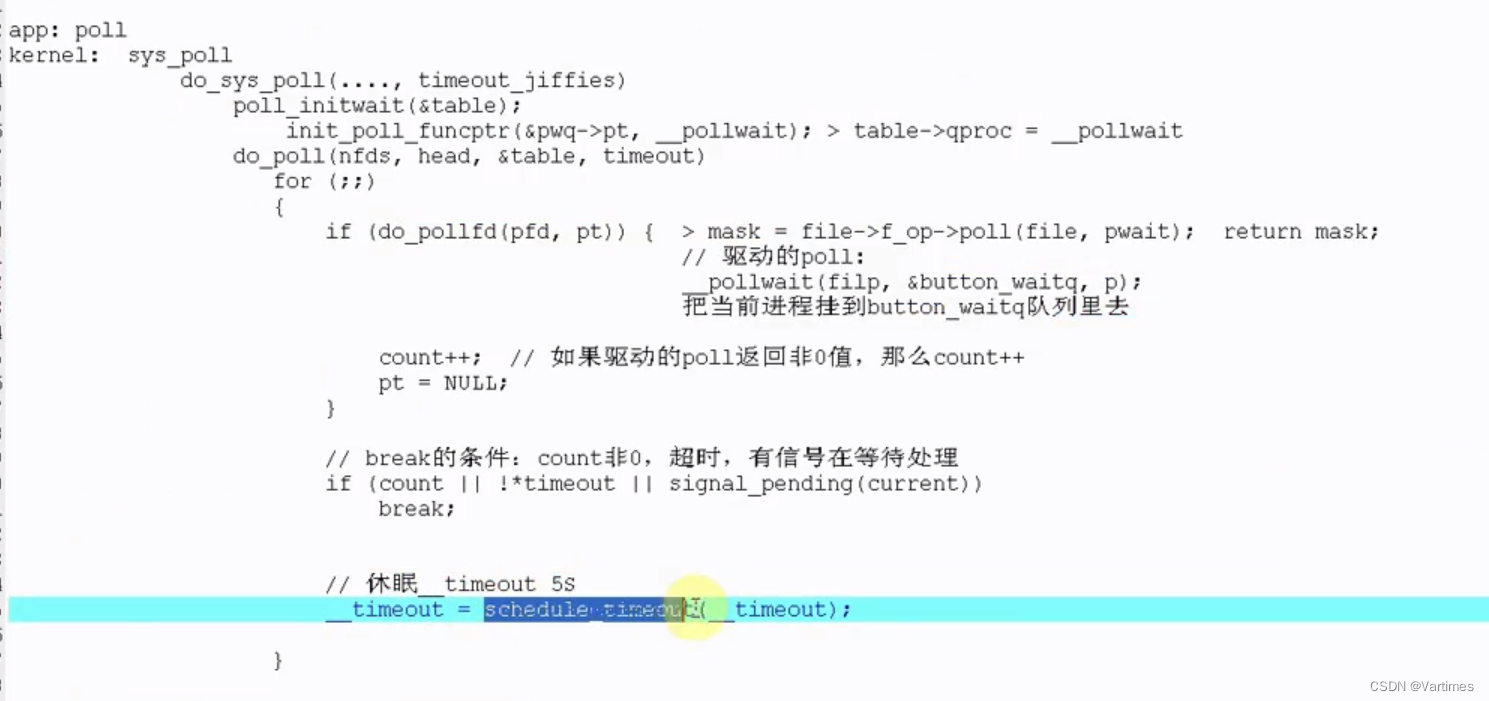

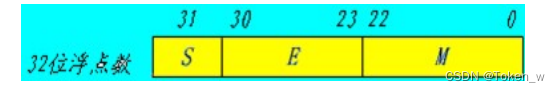

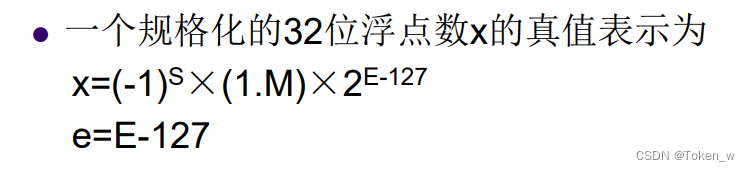

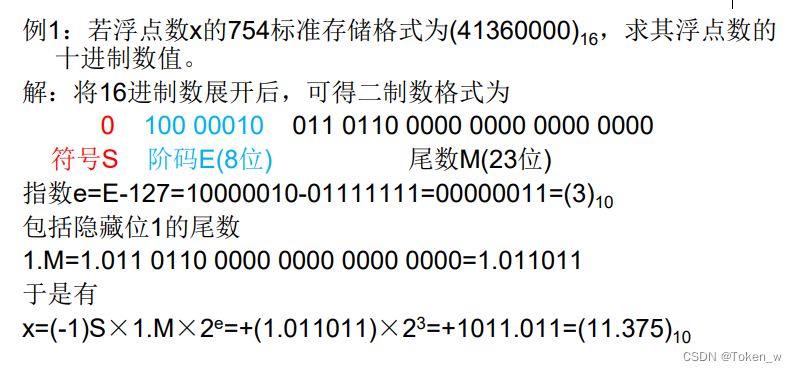

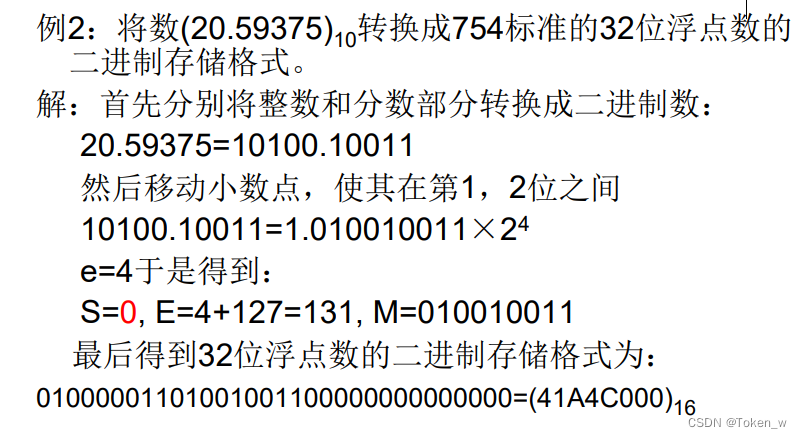

2.1 ieee754标准、32位浮点数

- S数的符号位,占1位,在最高位,“0”表示正数,“1”表示负 数。

- M是尾数, 占23位,在低位部分,采用纯小数表示

- E是阶码,占8位,采用移码表示。移码比较大小方便。

- 规格化: 若不对浮点数的表示作出明确规定,同一个浮点数 的表示就不是惟一的。

规格化32位浮点数真值表示:

例题:

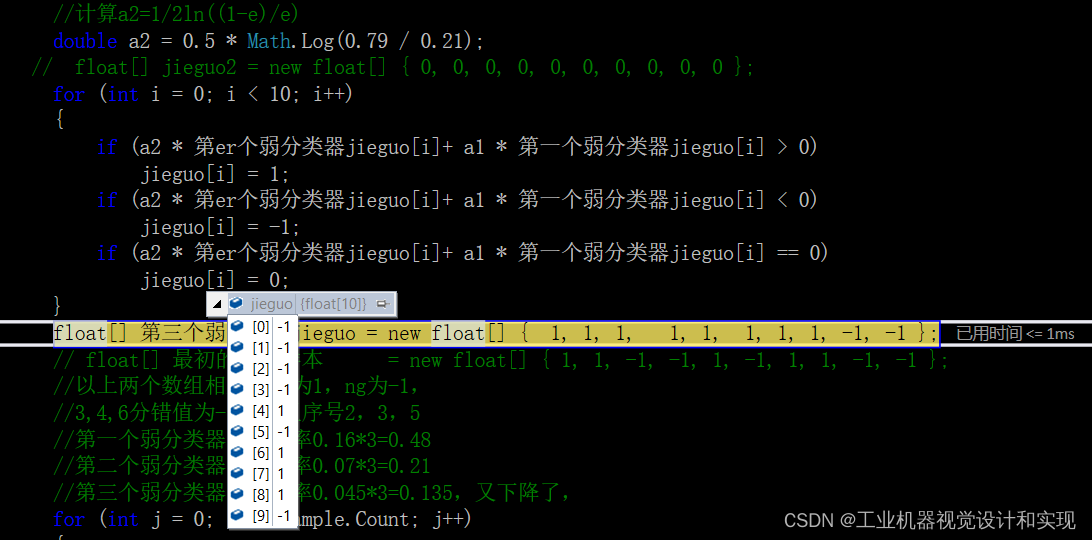

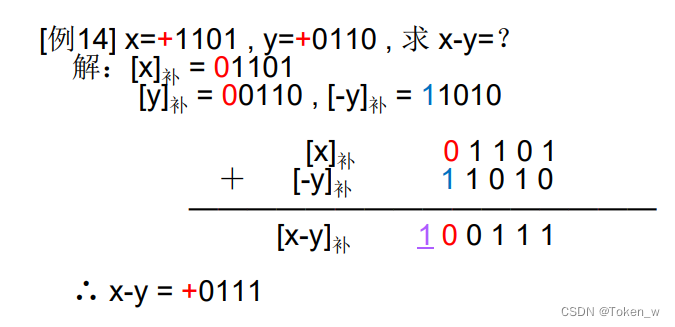

2.2 补码运算

主要考查补码的加减法运算,溢出

正数的反码是其本身(等于原码),负数的反码是符号位保持不变,其余位取反。

正数的补码是其本身,负数的补码等于其反码 +1。

例题:

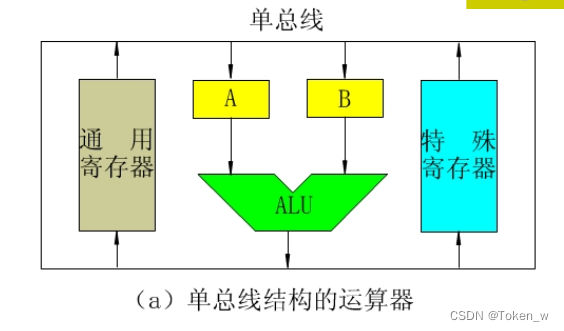

2.3 运算器的基本结构形式

- 单总线

单总线,所有部件都连接到同一总线上,数据可以寄存在任何两个寄存器之间,或者任一个寄存器和ALU之间传送。

同一时间内,只能用一个操作数放在但总线上,缺点是操作速度比较慢,但不会对每种指令增加很多执行时间,控制电路比较简单。

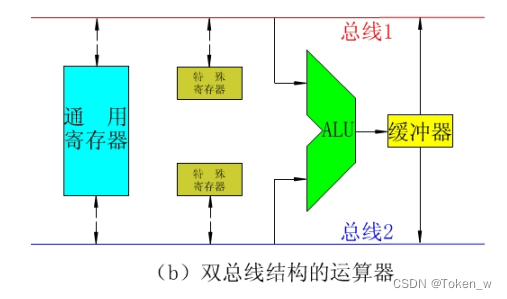

2.双总线

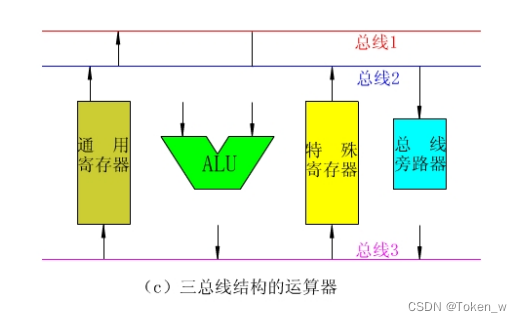

3.三总线

第三章 存储系统

3.1 主存与cache的地址映射

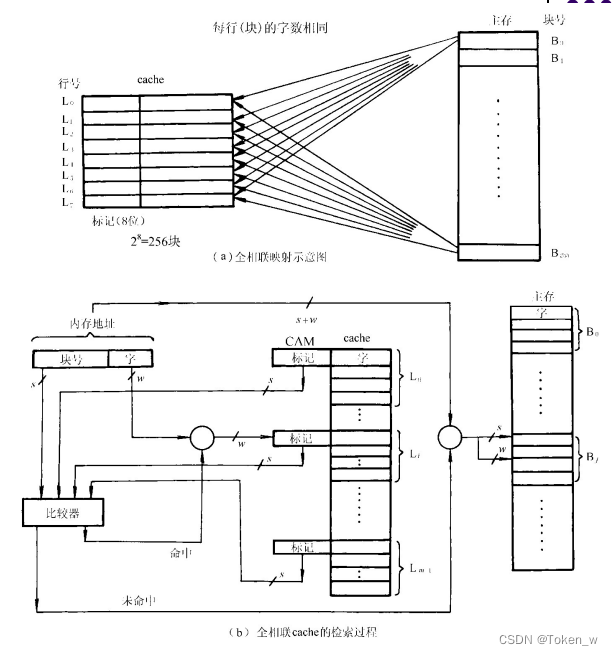

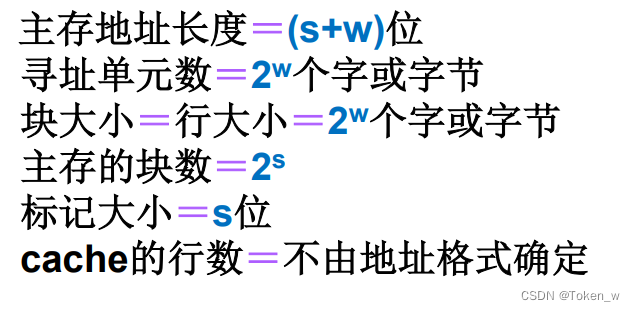

3.1.1 全相联映射方式

(1)将地址分为两部分(块号和字),在内存 块写入Cache时,同时写入块号标记;

(2)CPU给出访问地址后,也将地址分为两部 分(块号和字),比较电路块号与Cache 表 中的标记进行比较,相同表示命中,访问相应 单元;如果没有命中访问内存,CPU 直接访 问内存,并将被访问内存的相对应块写入 Cache。

特点:

优点:冲突概率小,Cache的利用高。

缺点:比较器难实现,需要一个访问速度很快代价 高的相联存储器

应用场合:

适用于小容量的Cache

转换公式:

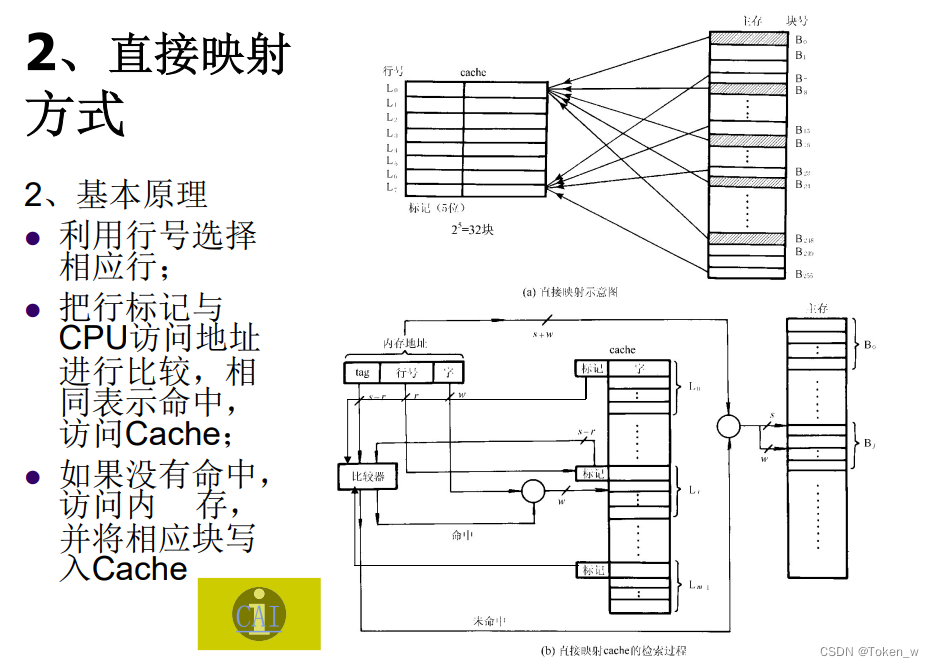

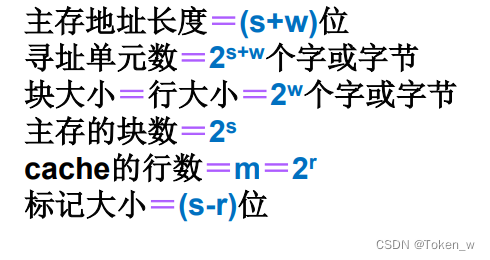

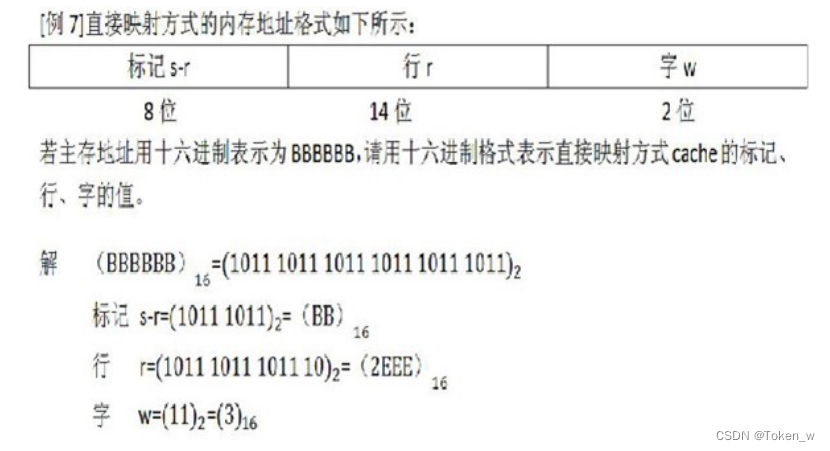

3.1.2 直接映射方式

映射方法(一对多)如:

i= j mod m

主存第j块内容拷贝到Cache的i行

一般I和m都是2N级

特点

优点:比较电路少m倍线路,所以硬件实现简单,Cache地址为主 存地址的低几位,不需变换。

缺点:冲突概率高(抖动)

应用场合

适合大容量Cach

转换公式:

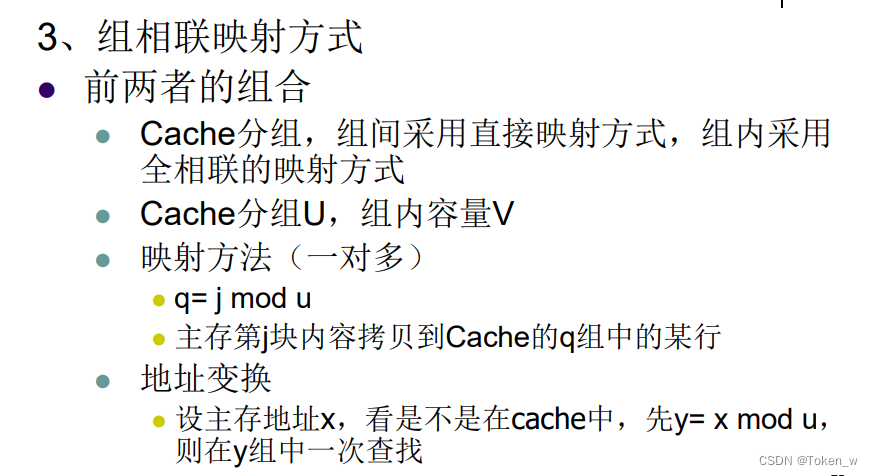

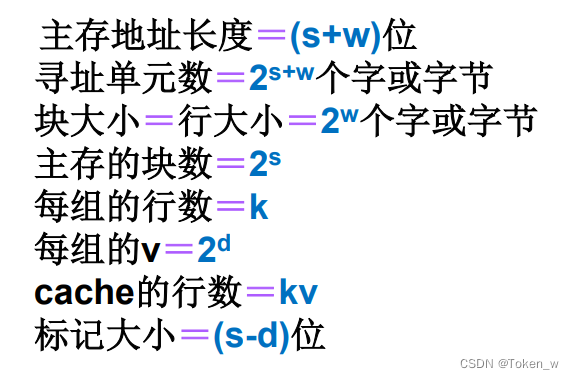

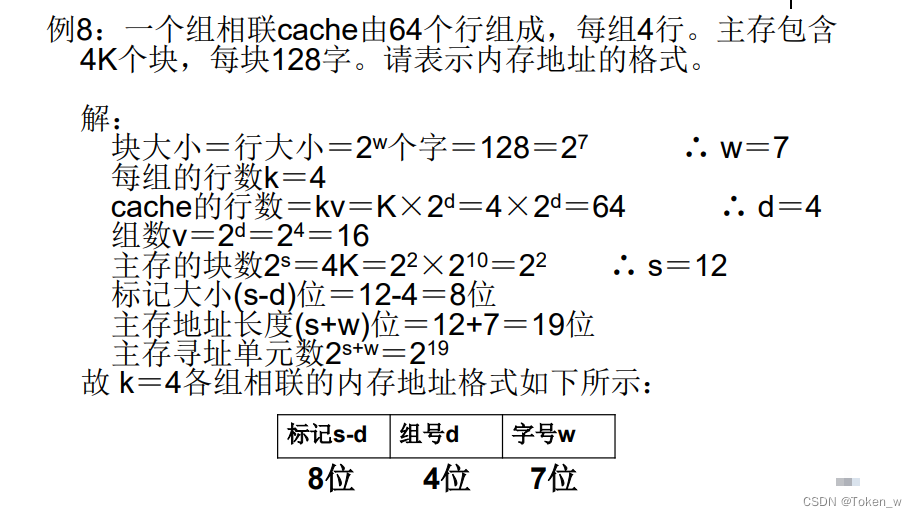

3.1.3 组相联映射方式

分析:比全相联容易实现,冲突低

v=1,则为直接相联映射方式

u=1,则为全相联映射方式

v的取值一般比较小, 一般是2的幂,称之为v路组相联cache.

转换公式:

例题:

这个例题最好是结合课本,看例题3.6和3.7

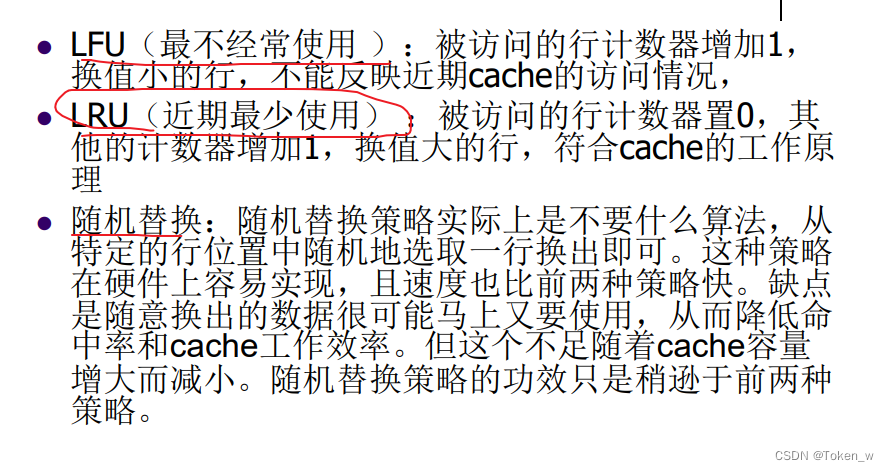

3.2 cache替换策略

第四章 指令系统

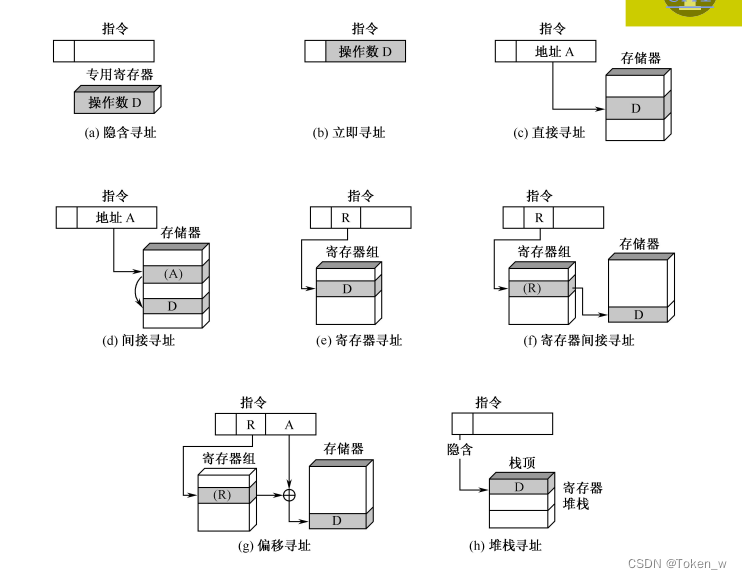

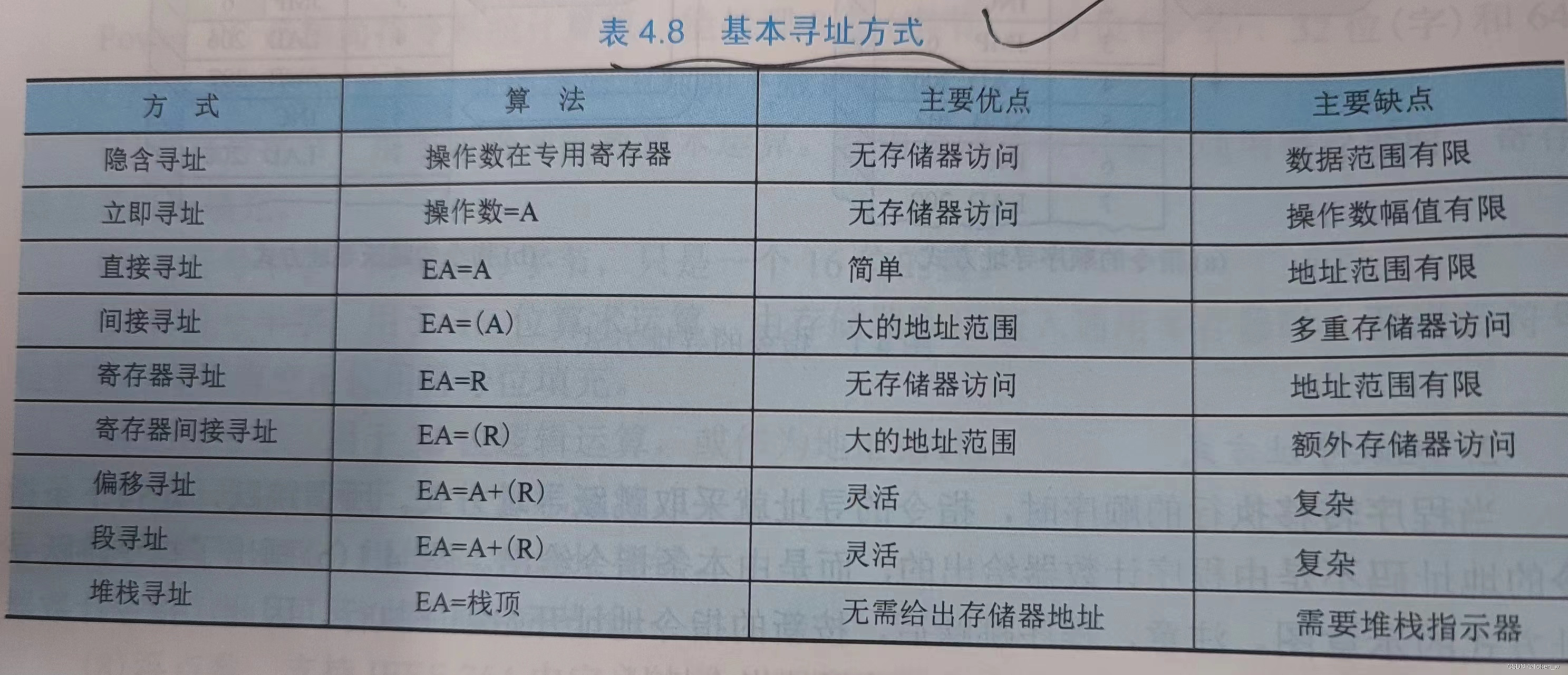

4.1 基本寻址方式

4.2 精简指令系统RISC

特点(采用流水线技术)

简单而统一格式的指令译码;

大部分指令可以单周期执行

只有LOAD/STORE可以访问存储器

简单的寻址方式

采用延迟转移技术

采用LOAD延迟技术

三地址指令格式

较多的寄存器

对称的指令格式

最大特点:1.选取使用频率最高的一些简单指令,指令条数少,2.指令长度固定,指令格式种类少,寻址方式少,3.只有取数/存数指令访问存储器,其余指令的操作都在寄存器之间进行。

第五章 中央处理器

5.1 cpu中的主要寄存器

- 数据缓冲寄存器(DR):1.中转站;2.补偿速度差别

- 指令寄存器(IR):存储当前正在执行的指令

- 程序计数器(PC):存储下一条要执行的指令的地址

- 数据地址寄存器(AR):保存当前cpu所访问的数据存储器单元的地址

- 通用寄存器:存储临时数据和计算结果

- 程序状态寄存器(PSWR):保存由算术运算指令和逻辑运算指令运算或测试结果建立的各种条件代码

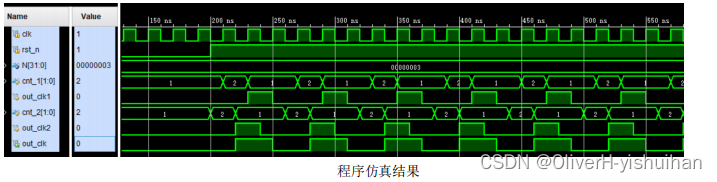

5.2 流水cpu

主要问题:三种相关冲突(资源相关、数据相关、控制相关)

资源相关:多条指令进入流水线后在同一时钟周期 内争用同一功能部件。

解决办法:延迟法。后边指令拖一拍再推进;增设一个功能部件

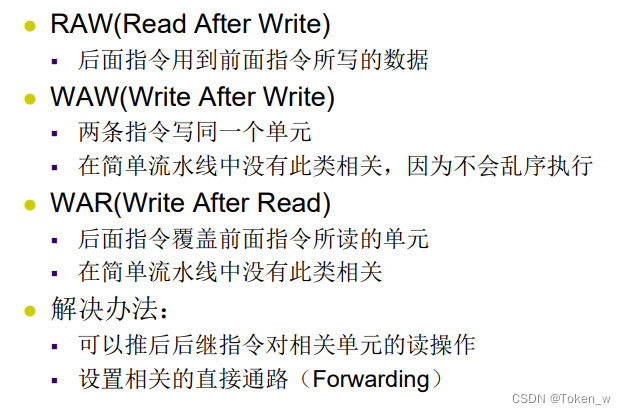

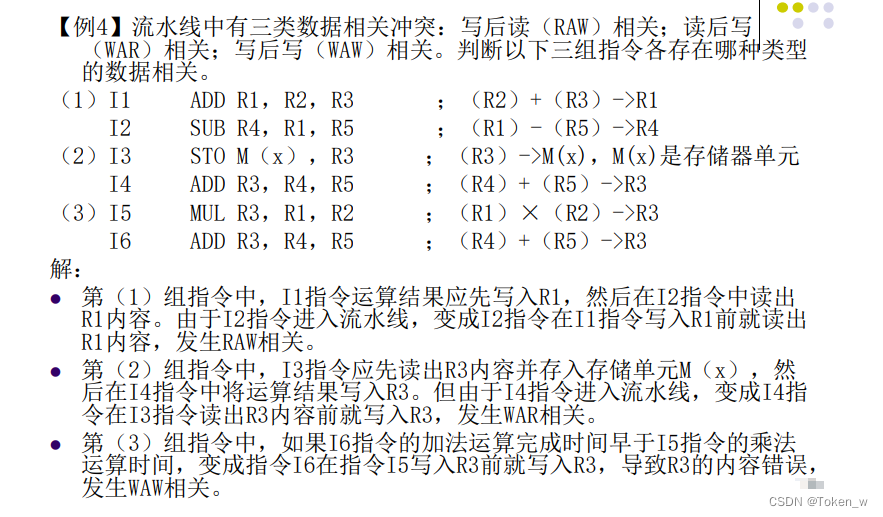

数据相关:

例题:

第六章 总线系统

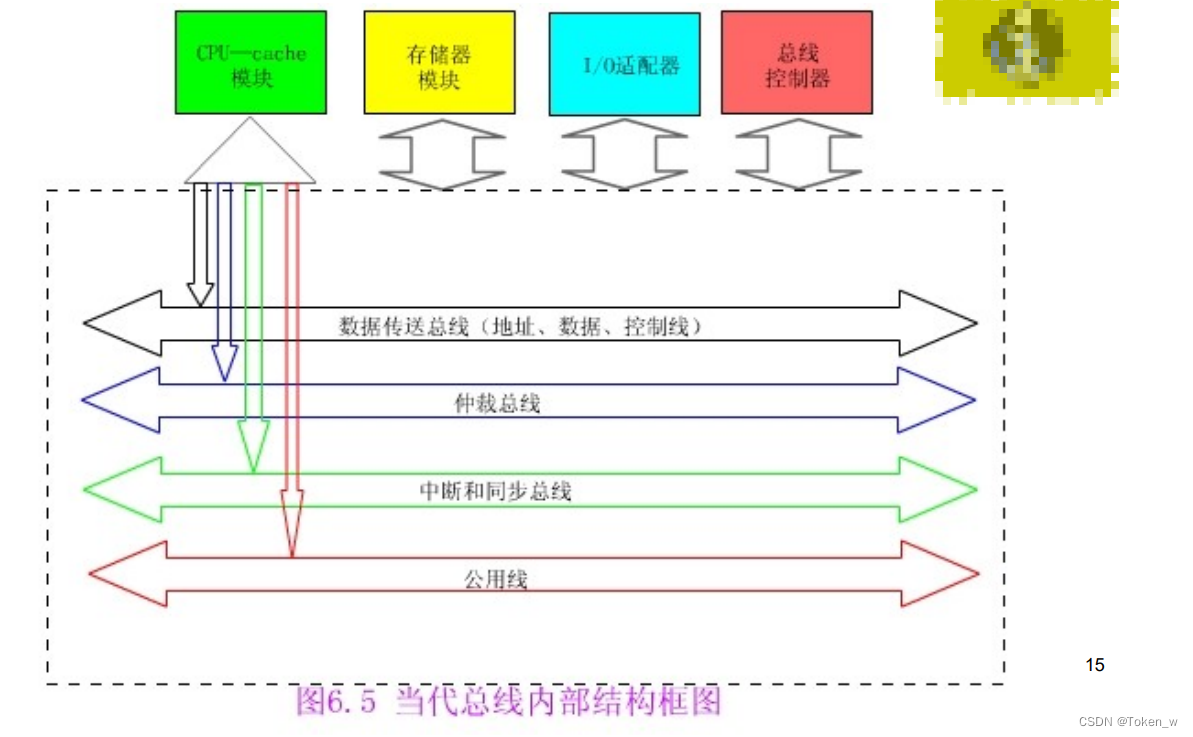

6.1 当代总线内部结构

cpu和他私有的cache一起作为一个模块与总线相连

- 数据总线:地址线、数据线、控制线组成

- 仲裁总线:包括总线请求线和总线授权线

- 中断和同步总线:用于处理带优先级的中断操作,包括中断请求线和中断认可线

- 共用线:包括时钟信号线、电源线、地线、系统复位线以及加点或断电的时序信号线等

第七章 外围设备

磁盘存储器的技术指标

第八章 输入输出系统

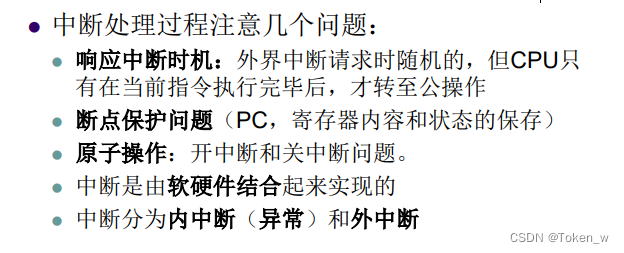

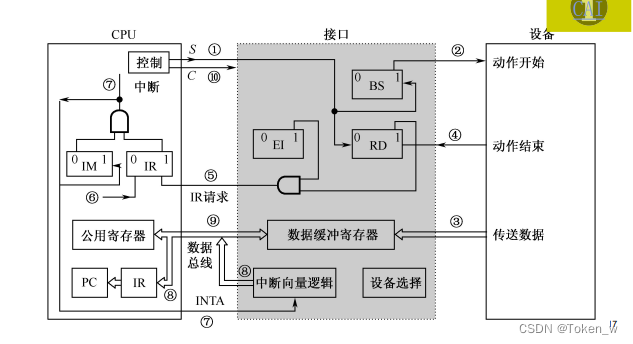

8.1 程序中断