目录

任意分频器电路设计

1、任意偶数分频器电路设计

1.2、实验任务

1.3、程序设计

1.3.1、代码如下:

1.3.2、编写仿真 TB 文件

2、任意奇数分频器电路设计

2.1、实验任务

2.2、程序设计

2.2.1、奇数分频电路代码

2.2.2、编写仿真 TB 文件

2.2.3、仿真验证

任意分频器电路设计

1、任意偶数分频器电路设计

偶数分频实现比较简单,假设为 N(偶数)分频,只需计数到 N/2-1,然后时钟翻转、计数器清零,如此循环就可以得到 N(偶)分频。举个例子,比如晶振时钟是 100Mhz 时钟,想得到一个 25Mhz 的时钟, 那么这个是一个 100/25=4 的四分频设计,那么按照我们刚说的计数到 4/2-1=1,然后时钟翻转、计数器清零, 就可以得到一个 24Mhz 的时钟。

1.2、实验任务

使用 Verilog 语言设计一个任意偶数分频电路,默认进行 4 分频。

1.3、程序设计

根据简介介绍的分频电路设计思路,假设为 N(偶数)分频,只需计数到 N/2-1,然后时钟翻转、计数清零,如此循环就可以得到 N(偶)分频,可以通过改变参量 N 的值和计数变量 cnt 的位宽实现任意偶分频,由于默认为 4 分频,因此 N 初始值为 4。我们由此可以写出如下代码。

1.3.1、代码如下:

//********************************************

module divide_2

(

input clk , // system clock 50Mhz on board

input rst_n, // system rst, low active

output reg out_clk // output signal

);

parameter N = 4 ;

reg [N/2-1:0] cnt ;

//===============================================================

// ------------------------- MAIN CODE -------------------------

//===============================================================

always @ (posedge clk or negedge rst_n) begin

if(!rst_n) begin

cnt <= 0;

out_clk <= 0;

end

else begin

if(cnt==N/2-1) begin

out_clk <= ~out_clk;

cnt <= 0;

end

else

cnt <= cnt + 1;

end

end

endmodule

1.3.2、编写仿真 TB 文件

只需要对时钟以及复位信号进行激励,代码编写如下:

//*************TB****************

`timescale 1ns / 1ps

module TB();

reg sys_clk ;

reg sys_rst_n;

wire out_clk ;

initial begin

sys_clk = 1'b0;

sys_rst_n = 1'b0;

#200

sys_rst_n = 1'b1;

end

always #10 sys_clk = ~sys_clk;

divide_2 u_divide_2(

.clk (sys_clk ),

.rst_n (sys_rst_n ),

.out_clk (out_clk )

);

endmodule

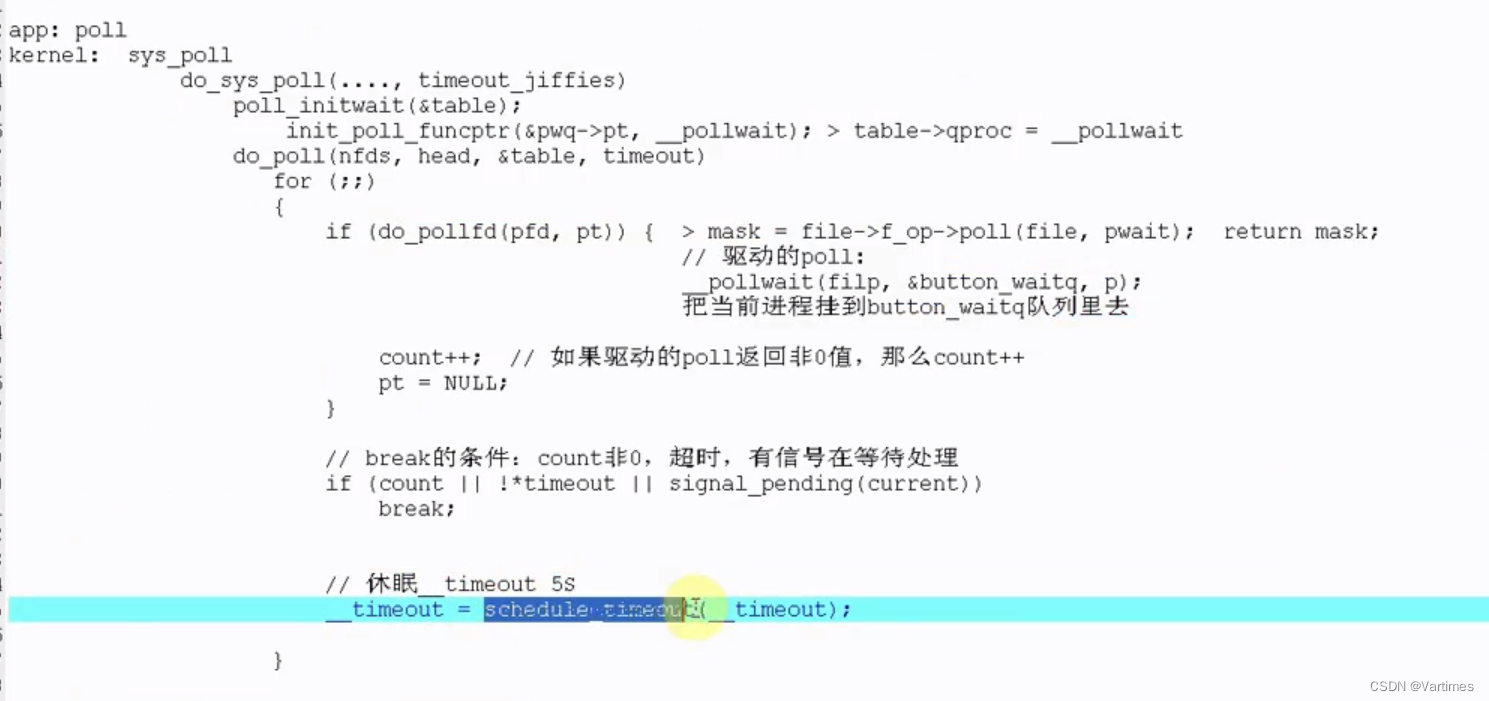

运行后的波形如下显示:

可以看出,N 初始为 4,当复位撤销(复位信号低有效)之后,cnt 即开始计数,在计数器计到 1 的时候,out_clk 进行取反操作,即得到一个四分频时钟,大家可以改变 N 参数看下,看下 N 参数不一样,最终分频的时钟是多少。

2、任意奇数分频器电路设计

有偶数分频就有奇数分频,仅实现分频功能来讲其中的差别和实现方式还是很大的,奇数分频相对于偶数分频要复杂一些,并不是简单的用计数器计数就可以实现的。

奇数分频,顾名思义,是说分频后的频率和分频前的频率比例是奇数,比如 100Mhz 时钟,进行三分频后,就是 33.33Mhz。

实现奇数分频原理是分别用上升沿计数到 N/2+1,分频后输出时钟进行翻转,再计数到 N/2 输出 out_clk1,再用下降沿计数到 N/2+1,分频后输出时钟再进行翻转,再计数到 N/2 输出out_clk2,将 out_clk1 和 out_clk2 相或即可。我们可以通过修改 N 的值和计数器的位宽来实现其他奇数分频。 其实 out_clk1 和 out_clk2 都已经是奇数分频的时钟,只不过占空比不是 50%。

下面在进行奇数分频设计之前,我们先来了解下占空比的概念。占空比指的是时钟信号在一个周期内高电平和低电平的比例。如下是一个 50%占空比的一个时钟波形。

如下是一个 30%占空比的一个时钟波形。

一般高质量的时钟信号都是要求有 50%占空比的,50%占空比的时钟信号对时序分析是非常有好处的。

2.1、实验任务

使用 Verilog 语言设计一个任意奇数分频电路,默认进行 3 分频,要求输出时钟的占空比是50%。

2.2、程序设计

根据简介介绍的奇数分频电路设计思路,我们需要新增两个计数器,cnt_1 和 cnt_2。初始化 cnt_1 和 cnt_2 为 1,out_clk1 为 0,out_clk2 为 0。

当 out_clk1 为 0 时,cnt_1 在 clk 时钟上升沿进行计数,当计数到 N/2+1 时 out_clk1 进行翻转,同时 cnt_1 赋值为初始值 1,当 out_clk1 为 1 时,cnt_1 在 clk 时钟上升沿进行计数,当计数到 N/2 时 out_clk1 进行翻转,同时 cnt_1 赋值为初始值 1。

当 out_clk2 为 0 时,cnt_2 在 clk 时钟下降沿进行计数,当计数到 N/2+1 时 out_clk2 进行翻转,同时 cnt_2 赋值为初始值 1,当 out_clk2 为 1 时,cnt_2 在 clk 时钟下降沿进行计数,当计数到 N/2 时 out_clk2 进行翻转,同时 cnt_2 赋值为初始值 1。

这样 N(奇数)分频就可以通过改变参量 N 的值和计数变量 cnt 的位宽实现任意奇数分频,由于默认为 3 分频,因此 N 初始值为 3。3 分频的 cnt_1 和 cnt_2 计数到 N/2+1 是计数到 2,小数舍弃掉, cnt_1 和 cnt_2 计数到 N/2 是计数到 1。

我们由此可以写出如下代码。

2.2.1、奇数分频电路代码

//**********任意奇数分频*******START***************************

module divide_3

(

input clk, // system clock 50Mhz on board

input rst_n, // system rst, low active

output out_clk // output signal

);

parameter N = 3 ;

reg [N/2 :0] cnt_1;

reg [N/2 :0] cnt_2;

reg out_clk1;

reg out_clk2;

//=====================================================================

// ------------------------- MAIN CODE -------------------------------

//=====================================================================

always @(posedge clk or negedge rst_n) begin //上升沿输出 out_clk1

if(!rst_n) begin

out_clk1 <= 0;

cnt_1 <= 1; //这里计数器从 1 开始

end

else begin

if(out_clk1 == 0) begin

if(cnt_1 == N/2+1) begin

out_clk1 <= ~out_clk1;

cnt_1 <= 1;

end

else

cnt_1 <= cnt_1+1;

end

else if(cnt_1 == N/2) begin

out_clk1 <= ~out_clk1;

cnt_1 <= 1;

end

else

cnt_1 <= cnt_1+1;

end

end

always @(negedge clk or negedge rst_n) begin //下降沿输出 out_clk2

if(!rst_n) begin

out_clk2 <= 0;

cnt_2 <= 1; //这里计数器从 1 开始

end

else begin

if(out_clk2 == 0) begin

if(cnt_2 == N/2+1) begin

out_clk2 <= ~out_clk2;

cnt_2 <= 1;

end

else

cnt_2 <= cnt_2+1;

end

else if(cnt_2 == N/2) begin

out_clk2 <= ~out_clk2;

cnt_2 <= 1;

end

else

cnt_2 <= cnt_2+1;

end

end

assign out_clk = out_clk1 | out_clk2;

endmodule

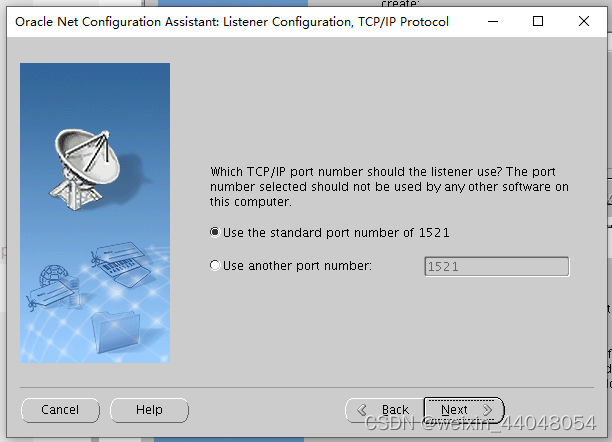

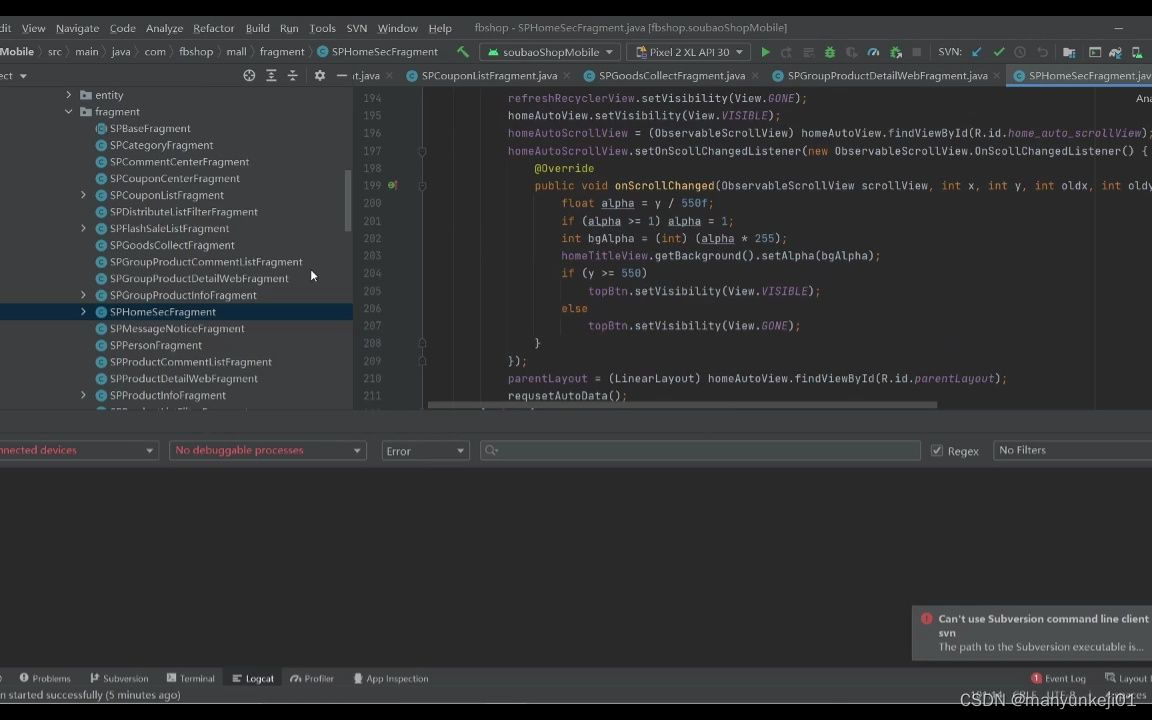

使用 Vivado 综合后也可以看到电路结构,在 RTL ANALYSIS 的 Schematic 中来看下综合的电路结构。

可以看出,cnt_1 和 cnt_2 是一个 3bit 的计数器,out_clk1 和 out_clk2 的电路结构基本是完全相同的,只是 cnt_1 和 cnt_2 计数器变化的时钟沿不一样,大家可以看出 cnt_2 的寄存器的 clk 前面有一个取反的标记,表示 cnt_2 是在时钟下降沿进行变化,然后 out_clk1 和 out_clk2 进行或操作,即得到一个 50%占空比的奇数 3 分频时钟。

2.2.2、编写仿真 TB 文件

只需要对时钟以及复位信号进行激励,代码编写如下:

`timescale 1ns / 1ps

//

module tb_divider_3(); //仿真模块

//输入 reg 定义

reg sys_clk;

reg sys_rst_n;

//输出 wire 定义

wire out_clk;

//设置初始化条件

initial begin

sys_clk = 1'b0; //初始化时钟为0

sys_rst_n <= 1'b0; //初始复位

#200 //200个时间单位后

sys_rst_n <= 1'b1; //拉高复位

end

always #10 sys_clk = ~sys_clk;

//例化被测试模块

divider_3 u_divider_3

(

.sys_clk (sys_clk ),

.sys_rst_n (sys_rst_n ),

.out_clk (out_clk )

);

endmodule

2.2.3、仿真验证

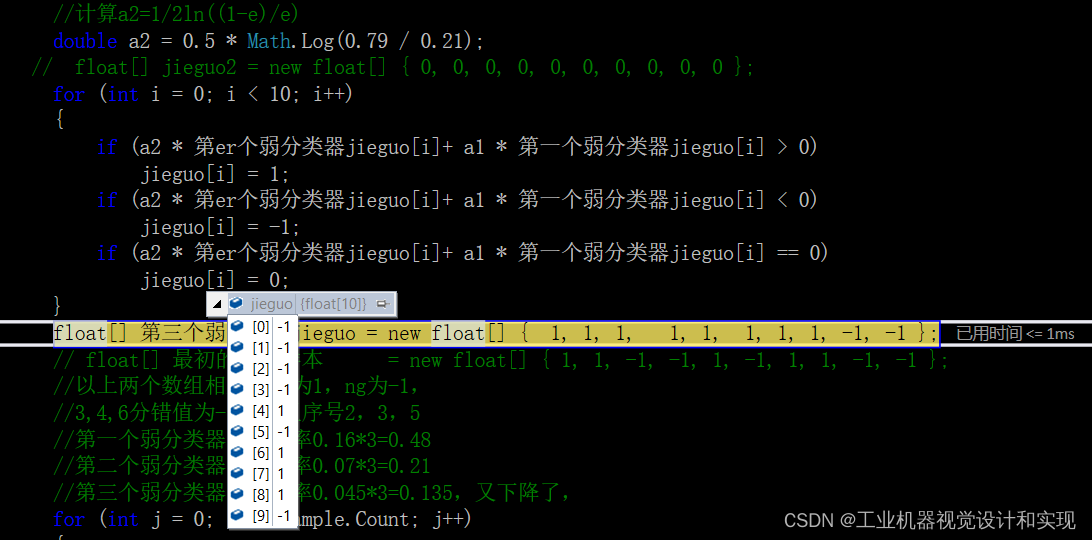

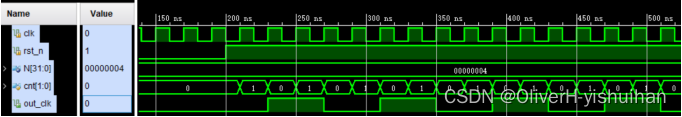

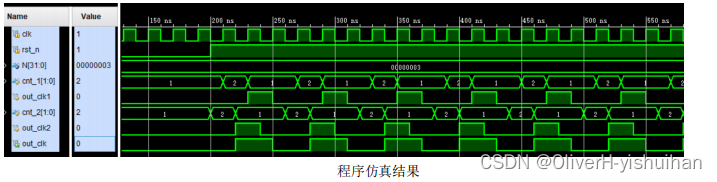

测试程序在 Xilinx 的 Vivado 软件 或者其他仿真工具运行后的波形如下显示:

可以看出,N 初始为 3,当复位撤销(复位信号低有效)之后,cnt_1 和 cnt_2 即开始计数, 当 out_clk1 为 0 时,在 cnt_1 计数器计到 2 的时候,out_clk1 进行取反操作,当 out_clk1 为 1 时,在 cnt_1 计数器计到 1 的时候,out_clk1 进行取反操作。

当 out_clk2 为 0 时,在 cnt_2 计数器计到 2 的时候,out_clk2 进行取反操作,当 out_clk2 为 1 时,在 cnt_2 计数器计到 1 的时候,out_clk2 进行取反操作。

我们可以看出 out_clk1 和 out_clk2 都不是 50%占空比的时钟,大概是 30%占空比。然后 out_clk1 和 out_clk2 进行或操作,即得到一个 50%占空比的奇数 3 分频时钟。

大家可以改变 N 参数看下,看下 N 参数不一样,最终分频的时钟是多少。