前言

- ddr3引脚分配基础知识

- ddr3引脚分配过程中遇到的问题

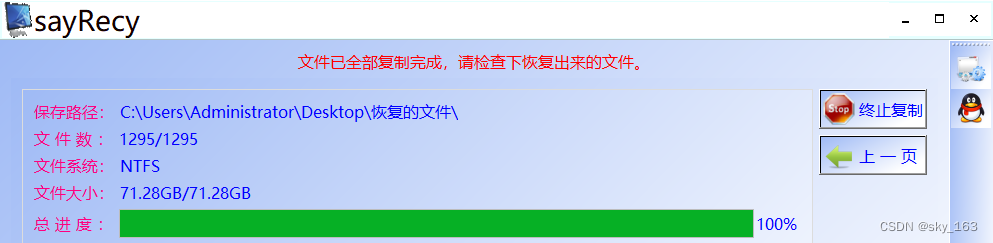

一次作者在某项目设计时,应硬件同事要求,验证设计管脚摆放位置。出现的问题记录一下,以便以后避坑。

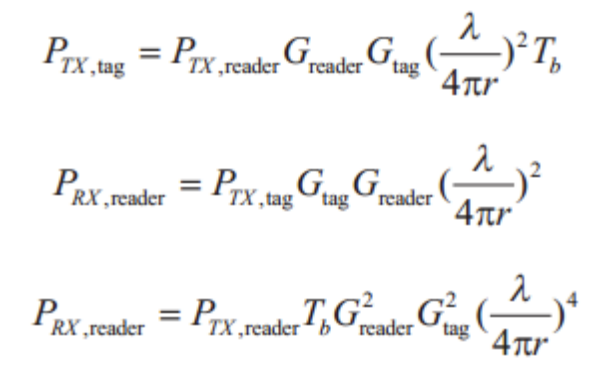

ddr3引脚分配基础知识

1.ddr3一个bank可以放置4个group。

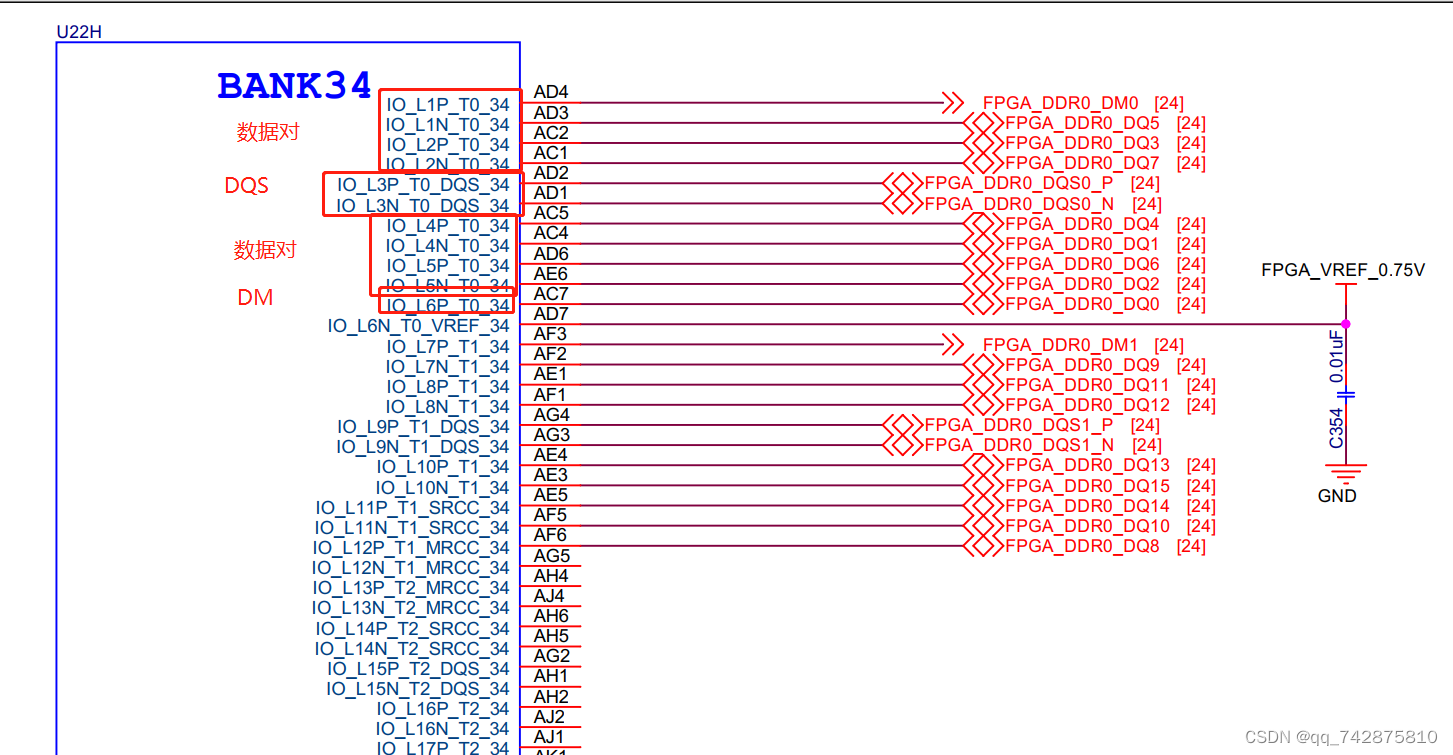

2.每个group包括1对dqs差分信号,8个数据信号,1个dm信号。其中dqs的位置是固定的,不能随意接,数据信号dq和dm在组内是可以互换的,数据放置时必须按group摆放。

3.一个mig控制器最多支持的数据位宽为72bit。这些数据分布在3个bank上。其中地址、控制、时钟信号必须在中间bank。比如使用7K325T芯片的bank32 33 34 ,地址、控制、时钟信号必须放置在bank33。

4.时钟信号必须放置在一对差分对上。

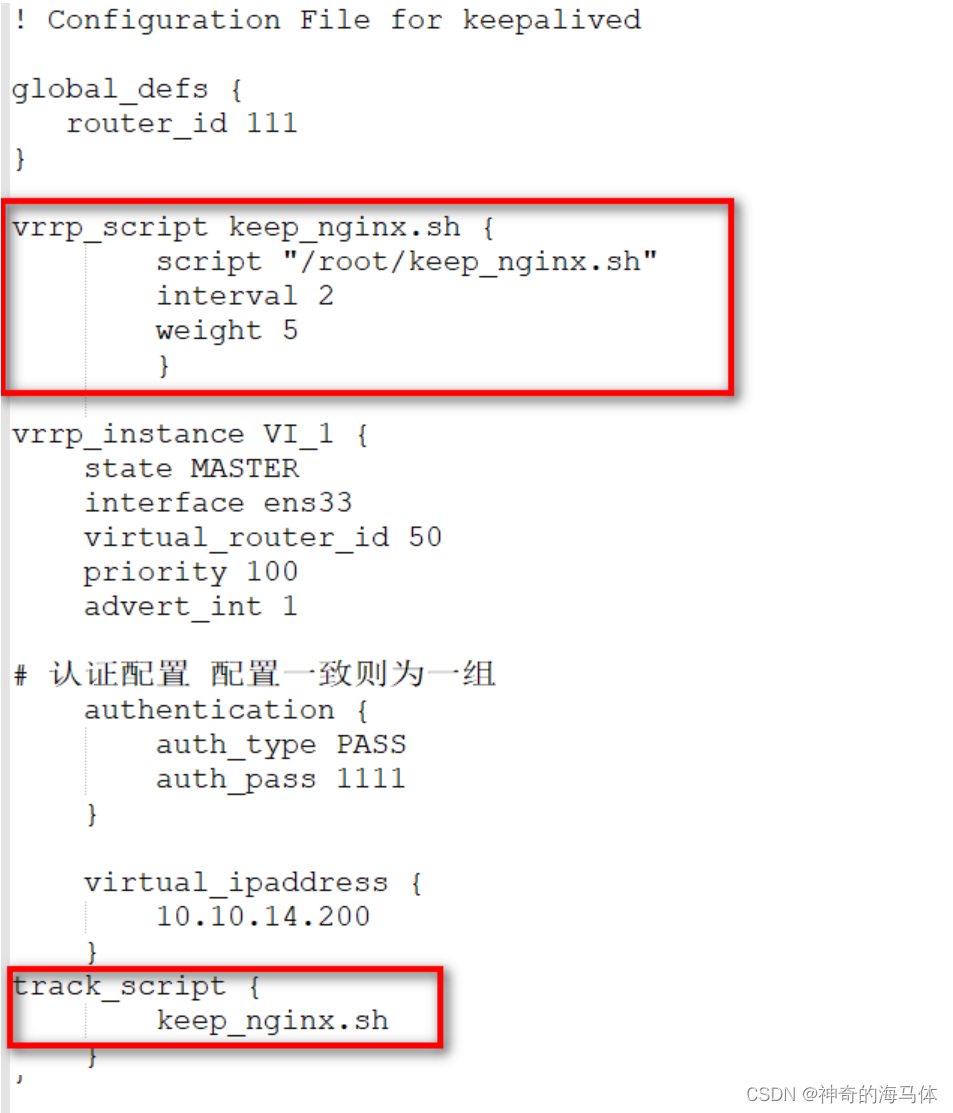

ddr3引脚分配过程中遇到的问题

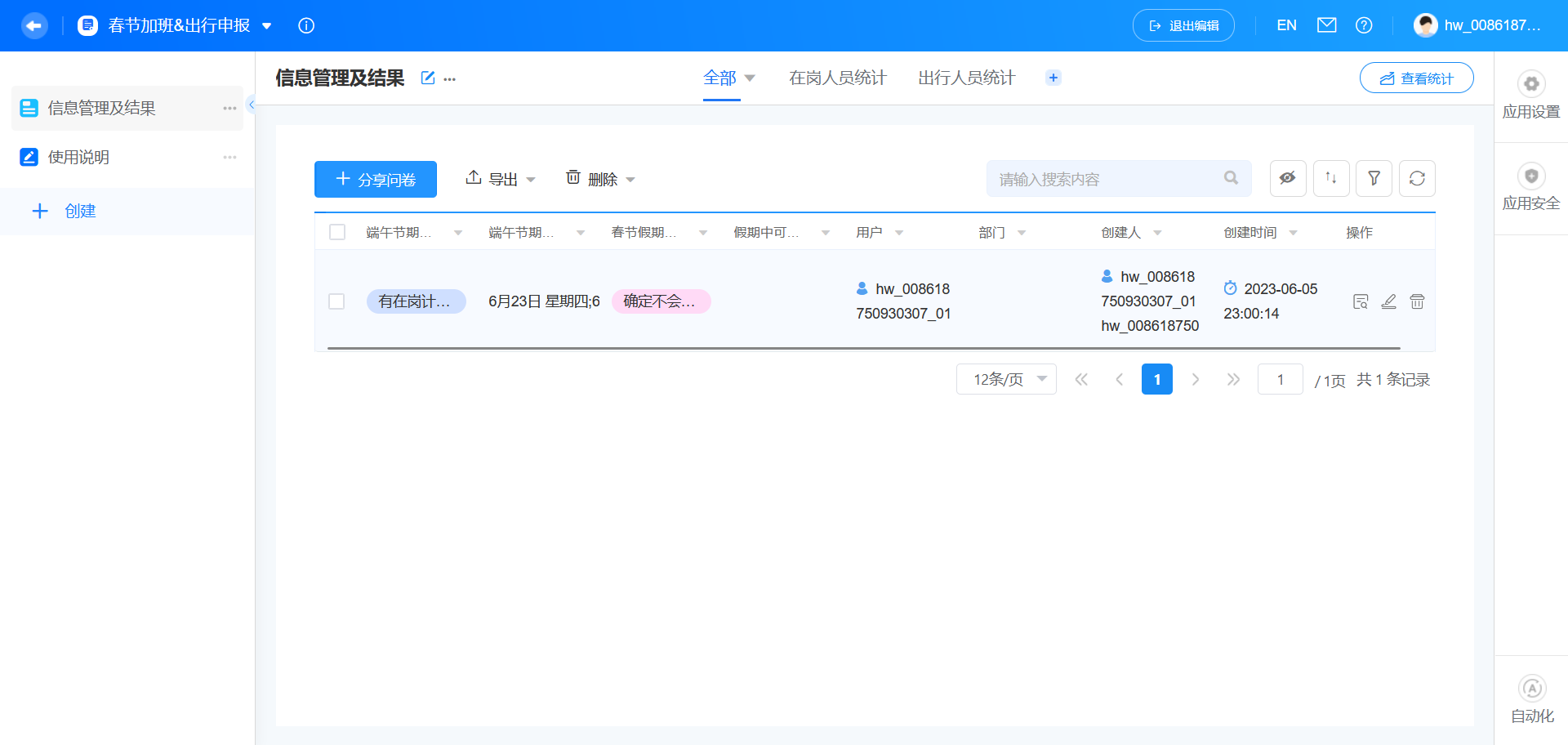

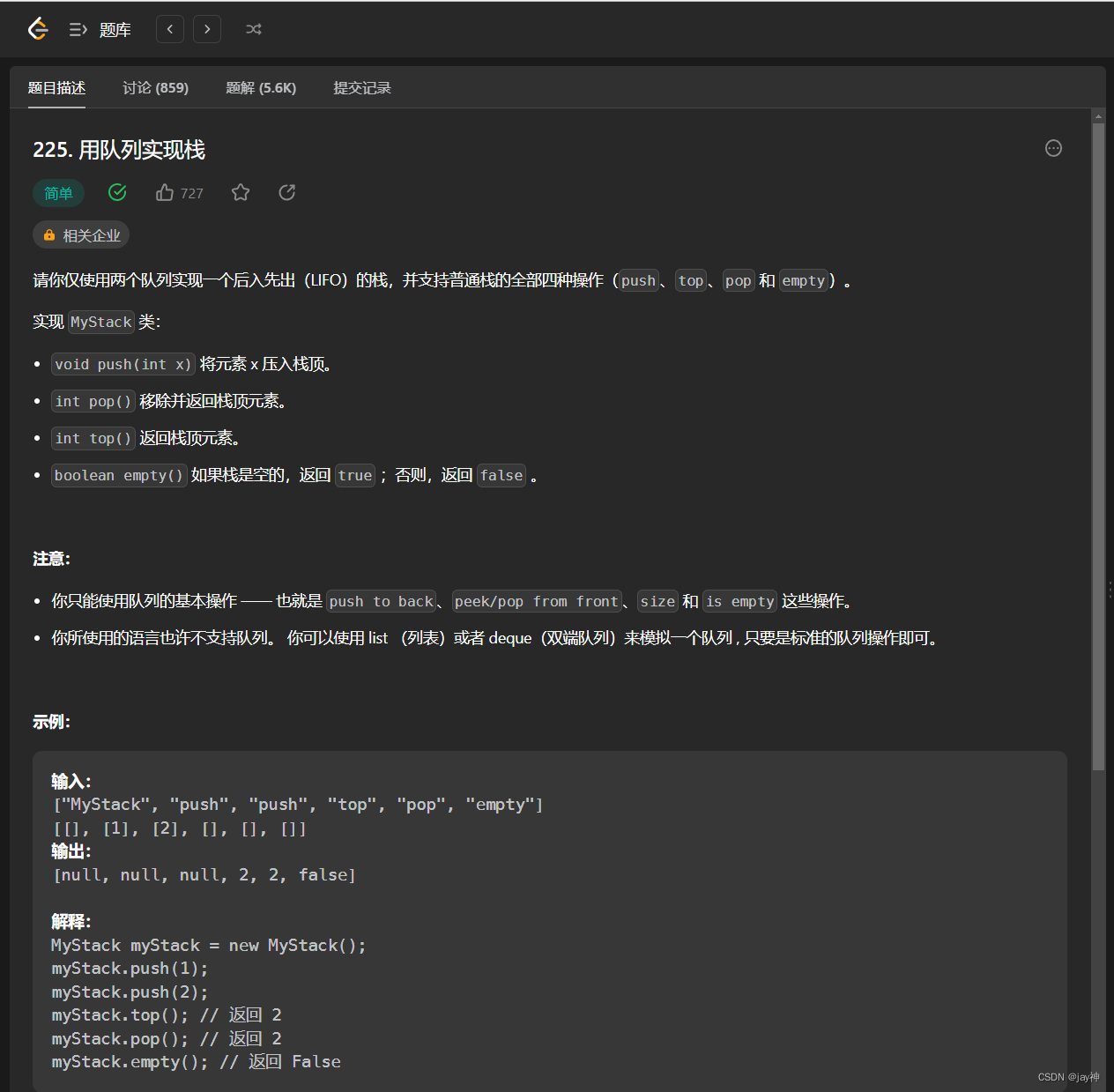

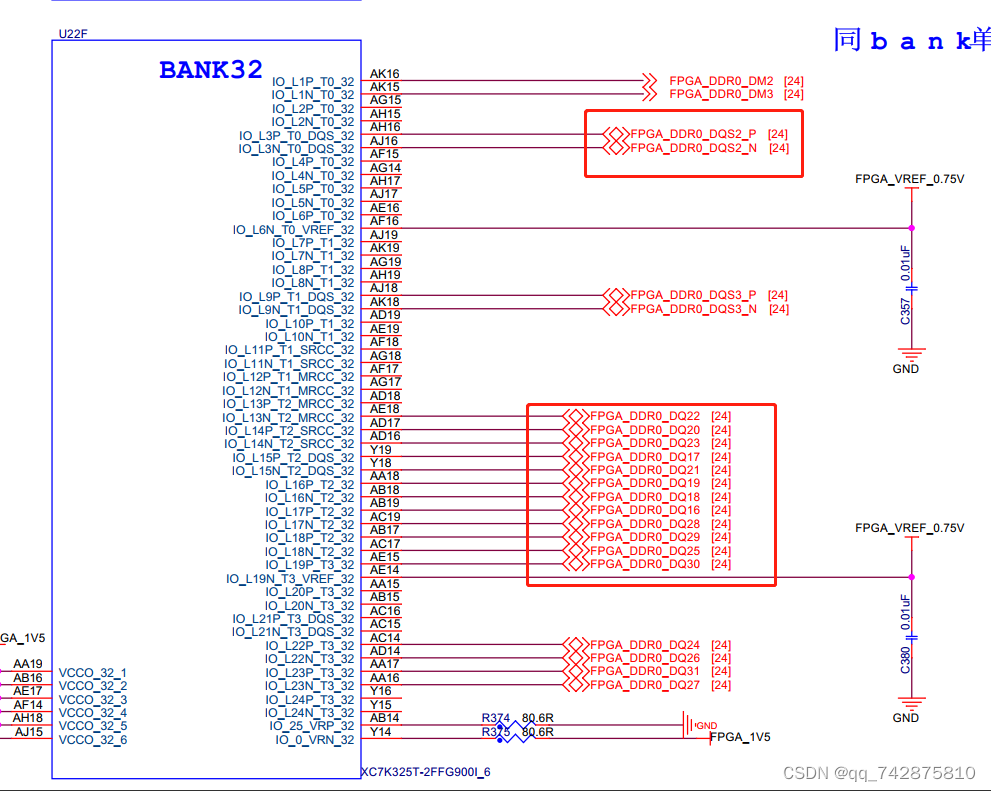

1.下图是错误设计,ddr3的数据信号和dqs没有放置在一组,错误。

2.硬件设计同事布线放置不开,将时钟的ck_p和ck_n放置在bank32,cke放置在bank33,drc验证错误。

3.warning&#