在数字电路的设计中,对关键路径的处理方法之一就是插入寄存器,然而,对握手信号插入寄存器则需要进行特殊的处理,否则可能导致数据传输的错乱,严重影响电路的功能。

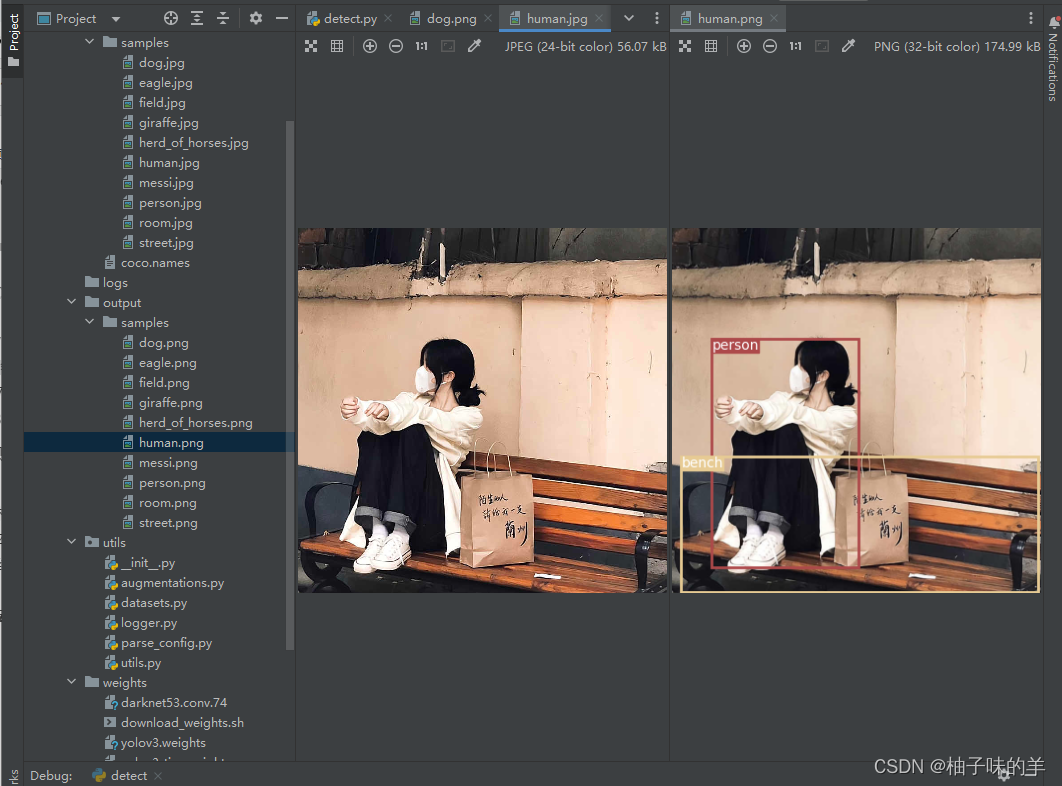

如图所示,为了阐述对握手信号打拍的处理方式,我们给出了下图所示的简化模型,其中,上游的握手信号包括valid_up,ready_up和data_up,而下游的握手信号则包括valid_down,ready_down和data_down,其数据流向如图中箭头所示。

对握手信号的打拍主要可以分为以下三种情况:

仅对valid信号打拍

当valid信号所在路径的延迟较大时,可能会影响系统整体的时钟频率。因此,可以考虑在valid信号所在的组合逻辑路径插入寄存器,以提升系统的性能。

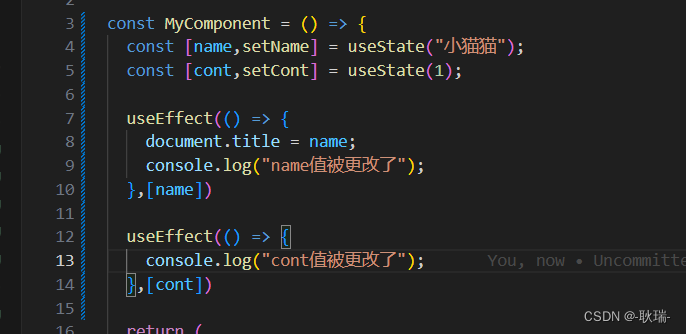

RTL实现如下:

module valid_pipe(

input logic clk,

input logic rst