知识的价值在于分享,欢迎大家批评指正,共同进步。

目录

1 功能安全

2 技术特性

3 安全系统架构

4 TI Hercules系列

4.1 TMS570安全概念基本原理

4.1.1 1oo1D双核安全概念

4.1.2 1oo1D优势

总结

参考文献

1 功能安全

根据ISO26262-2018,功能安全是指不存在因电气和电子系统故障行为引起的危害而导致的不合理风险。

在汽车功能安全标准ISO26262-5 2018 产品开发:硬件层面附录D对处理单元的诊断覆盖率推荐的安全技术措施中,作为可实现高诊断覆盖率的几种技术措施之一,硬件冗余技术中,双核锁步、非对称冗余、编码计算是三种典型的技术措施。

2 技术特性

处理器CPU作为控制器的核心,内部包括寄存器、内存、译码器、ALU、高速缓存、总线、电源、时钟、堆栈、复位电路,所有组成部分需要以正确的时序要求运行,但CPU也会出现故障,如EMC、辐射、时钟漂移、低电压都可能导致CPU出现错误导致控制行为不可控。

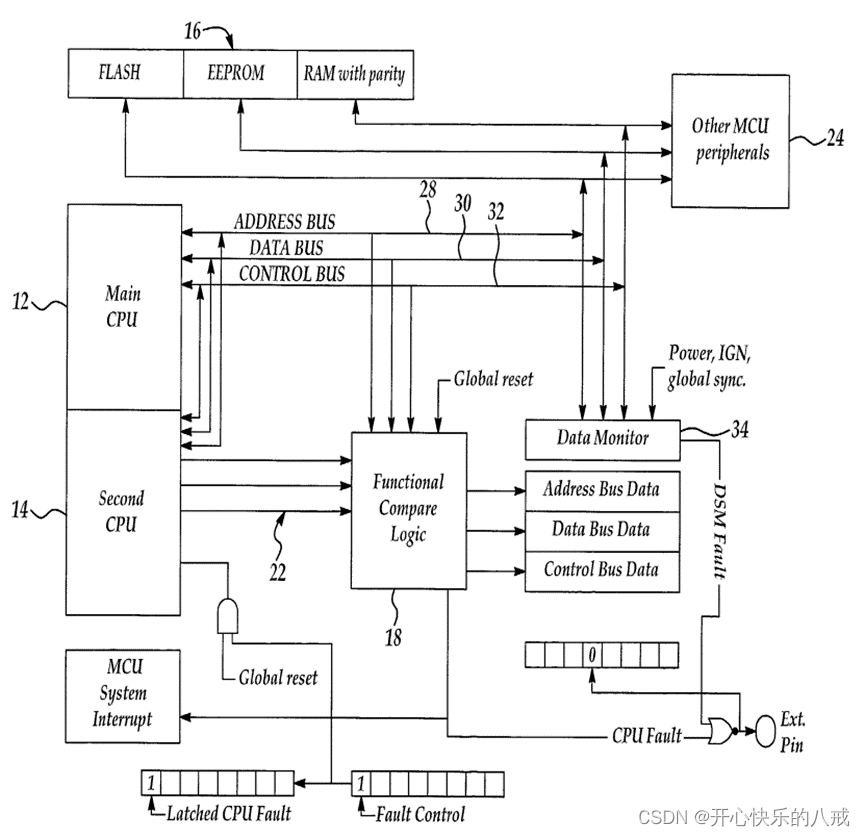

双核锁步CPU是一种CPU冗余技术,在一个芯片中包含两个相同的处理器,一个作为master,一个作为slave,它们执行相同的代码并严格同步,master可以访问系统内存并输出指令,而slave不断执行在总线上的指令(即由主处理器获取的指令)。

slave产生的输出,包括地址位和数据位,发送到比较逻辑模块,由master和slave总线接口的比较器电路组成,检查它们之间的数据、地址和控制线的一致性。检测到任何总线的值不一致时,就会发现其中一个CPU 上存在故障,但不会确定是哪个CPU故障。

这种CPU架构使得CPU自检独立于应用软件,不需要执行专门的指令集自检,实际运行的软件指令在每个时钟都进行比较,只需要测试软件用到的CPU资源,但这种架构不会对内存和总线进行检测,需要增加单独的检测方法以避免两个CPU的共模故障[注1]。

在《Delphi Secured Microcontroller Architecture》这篇关于锁步MCU的论文中,这种架构的优势有四方面:

优点:

- 由于减少了硬件元器件数量和连接,相比于使用两个独立的MCU,提高了硬件的可靠性;

- 电路板布局的小型化和复杂度降低,使得板级EMI性能提升和辐射发射降低;

- 故障诊断能力的提升,故障从源头并且在第一次出现时就被检测到,不会漏掉潜伏故障;

- 提高了软件的可靠性,不需要双CPU的通信和数据同步,减少数据比较和决策逻辑,降低了软件验证的复杂度。

应用:

各大芯片厂商都在积极开发双核锁步架构的芯片,以期望在功能安全芯片领域占有更多的市场。

3 安全系统架构

现在,我们看看如何实现系统安全,怎样的系统架构才是一个安全的系统架构。

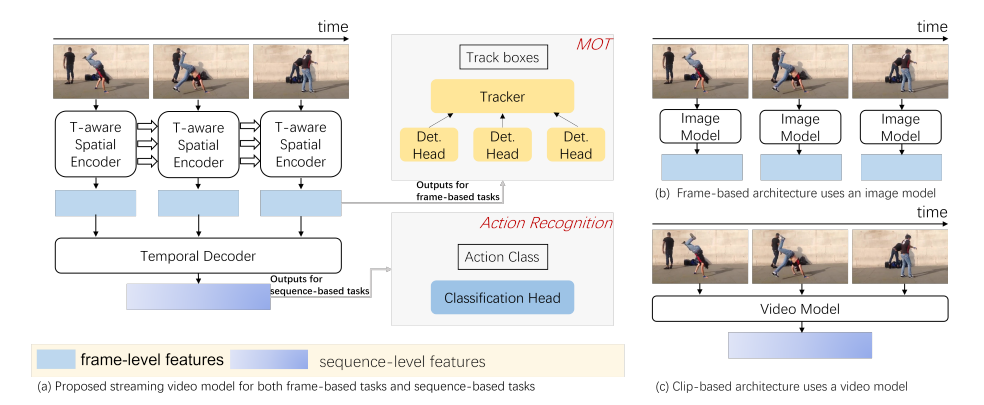

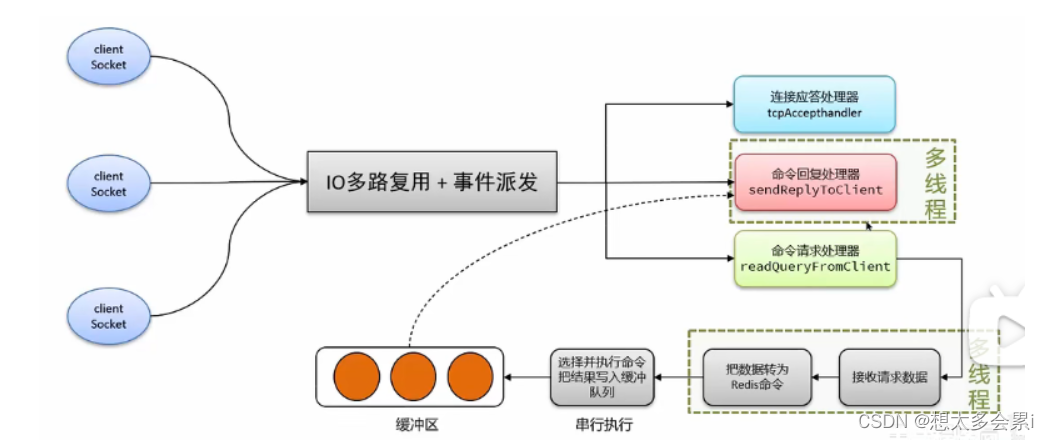

对于有功能性安全要求的系统,有很多可选择的系统架构。下面我们将介绍一些最常用的安全系统架构。通常在我们之后的系统描述时会有这样的概念——

“XooY-X out of Y -> XooY” 在这里的“Y”表示冗余通道数,"X”表示如果失效会导致系统失效的通道数。下面我们看几种不同的系统架构。

1oo1系统架构

首先,我们来看最常见、也是最简单的1oo1系统架构。

图1oo1系统架构

该结构中,整个系统只有一路输入和一路输出,任何一部分子系统的失效都会导致整个系统的失效,那么这种1oo1系统应该是能够实现某一功能的最小系统配置,该结构本身没有内部诊断和故障冗余设计,因此,这个系统不是功能安全的。

1oo2系统架构

图1oo2系统架构

与1oo1架构不同,1oo2的架构,整个系统增加了一路冗余设计,两个子系统输出部分采用串行方式,因此,两个子系统中的任何一个失效都会导致系统失效,这样的架构适合用于开路安全的系统,也就是在开路情况下系统处于安全状态,只有当两路子系统都正常的情况下,才会使系统工作在正常状态。因此,对于开路安全的系统来说,这样的架构是具有一定的安全性的。

2oo2系统架构

与1oo2类似,2oo2系统架构同样是当两个子系统都失效下才会导致系统失效。但是它们不同之处在于,2oo2执行机构部分采用并连的方式,对于闭合安全系统,当输入在正常的情况下,只要有任何一个子系统工作正常,就可以保证系统的安全。当系统其中一路出现异常断开时,保证系统仍然可以可靠闭合,起到一个开路故障冗余的作用。因此,这样的架构非常适合于闭合安全的功能。

图2oo2系统架构

1oo1D双核安全概念

图1oo1D双核安全概念

1oo1D系统架构,这里的D表示系统本身是带诊断模块的,当诊断模块发现失效之后,诊断通道可以禁止系统输出,安全等级可以等同于1oo2这样的系统架构。在这种系统架构中,诊断功能可以把检测到的一个危险失效转变成安全失效[注2]。TI TMS57OLS系列处理器所使用的就是1oo1D的系统架构。

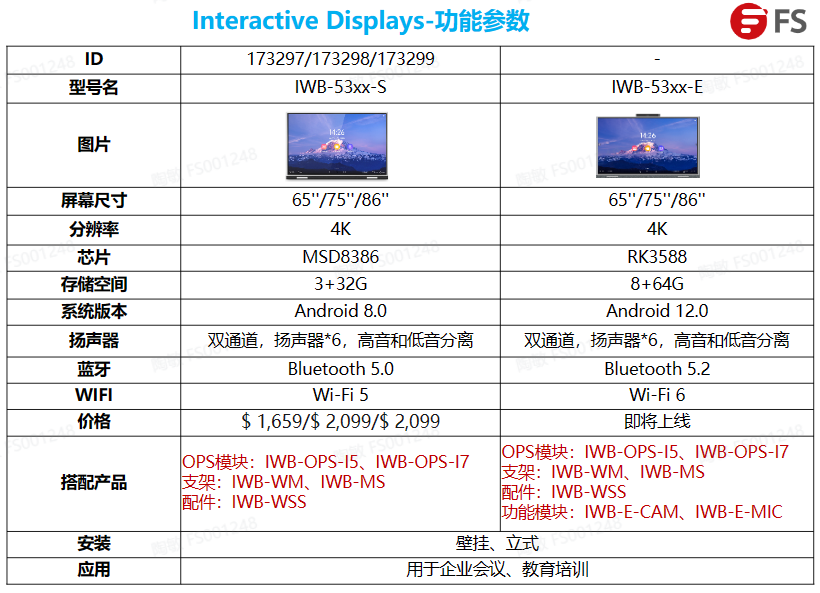

4 TI Hercules系列

Hercules是TI公司以ARM Cortex核心构建的安全关键CPU,包括三个系列:RM4,TMS570和TMS470M,内部由锁步双核CPU组成,最高可满足ISO26262 ASIL-D和IEC61508 SIL3功能安全标准的要求,并符合AEC-Q100车规级要求,双核锁步CPU架构、硬件BIST、MPU、ECC、片上时钟和电压监控可以满足汽车、铁路和航天航空关键功能安全应用。

4.1 TMS570安全概念基本原理

Hercules/'hə:kjuli:z/整个产品线安全理念是基于“安全岛[注3]”的思想展开的,对于MCU内部共享的重要的单元采取硬件诊断机制进行重点保护,比如对CPU,CPU矢量中断系统( VIM),系统控制单元:包括电源、复位、时钟以及操作系统关键部分∶如DMA,RTI定时器采用硬件诊断方式来保证其可以作为已知的绝对安全的“安全岛”。利用这些已经确认的安全岛对芯片上的其它部分进行诊断,从而覆盖至整个MCU的安全诊断。利用这种安全岛的思想,可以大大减少由于安全设计的需要而产生的成本压力,以达到安全与成本的有效统一。

图中红色部分是上面所说的由硬件完成诊断的安全岛,蓝色区域是基于安全岛概念,由硬件、软件混合完成诊断的模块。黑色部分为非关键性区域,不会进行任何诊断。

下面我们具体来看一下“安全岛”范围内各个安全模块的特性,到底是如何通过硬件方式来实现的。

4.1.1 1oo1D双核安全概念

首先,带双核锁步的双CPU部分,两个完全相同的CPU采用1oo1和1oo1D 的架构设计;空间上看,第二个CPU采用镜像旋转90度的放置方式,并且保证与第一个CPU之间的间距大于100微米,从空间上避免了共模失效;从时间来看,两个CPU在分别在运算之前和之后有两个周期的延时,从时间上避免了共模失效。并且每个CPU都有独立的保护环,所以可以有效减少共因失效的可能性[注4]。

当指令在进入第一个CPU进行运算的同时,另一路指令会经过一个周期的延时之后送至第二个CPU。经过两个周期的延时后,第一个CPU计算的结果,与第二个CPU所计算出的结果同时到达CPU比较模块(CCM),以完成两个CPU计算结果的比对。当比较发现两个CPU的结果不一致时,输出比较错误信息。比较模块具有自检功能,可以将自检错误信号输出,也可以根据需要强制输出错误信号,或者将错误信号从引脚输出,这样我们不仅能够检测CPU,还能检测比较器本身。4.1.2 1oo1D优势

采用这样1oo1D的双核锁步架构优势在什么地方呢?与用软件/多核方式的架构相比,1oo1D优势在于∶

※具有更快地错误检测,只需要2、3个周期就可以采用硬件方式检测到系统出错;具有更高的错误覆盖率,

※可以检测的故障覆盖硬件、瞬态、持续等各种错误类型﹔

※诊断功能工作时对性能的影响非常低,甚至没有任何影响,不需要额外的软件开销,对存储空间没有影响,而且几乎不占用Flash和RAM空间﹔

※对于原有的设计,用户不需要额外的软件开发工作,易于集成入已经现有的应用中,从而缩短产品开发的周期。

※诊断覆盖率可控:用户不需要担心软件的校验是否已经足够保证CPU的安全性,而可以将时间用来更多地开发自己的应用程序。

总结

LOCKSTEP技术使用相同的、冗余的硬件组件在同一时间内处理相同的指令。LOCKSTEP技术可以保持多个CPU、内存精确的同步,在正确的相同 时钟周期内执行相同的指令。

该技术保证能够发现任何错误,即使短暂的错误,系统也能在不间断处理和不损失数据的情况下恢复正常运行。

参考文献

[1]TI Hercules MCU构筑安全核心,开发套件如虎添翼-AET-电子技术应用 (chinaaet.com)

[2]ARM Cortex-M3内核_开心快乐的八戒的博客-CSDN博客

[3]锁步,冗余执行,以及分核锁 - 知乎 (zhihu.com)

[4]谈一谈自动驾驶中的Lock-Step Core - 知乎 (zhihu.com)

[5]独家详解Intel主板下的『LockStep』内存模式,以及为何开启它能让 ECC 内存比可靠更可靠 - 知乎

[6]E3430高性能多核MCU:面向BMS,显著提升汽车续航能力和安全性 - 知乎

[7]lock-step技术_lock step_mark_note的博客-CSDN博客

[8]Comparing Lock-Step, redundant execution & Split-Lock - Embedded blog - Arm [9]Community blogs - Arm Community

[10]谈双核锁步安全芯片 - 知乎

[11]The Lockstep Comparator Logic (LCL) provides one of the TriCore cores (CPU1) with an identical checker (or shadow) core which has the same inputs and runs the same operations as the main core. This allows the core to be checked for soft errors and other transient failures by comparing the outputs of the two core instances.

[12]德州仪器推出最快速的 Hercules™ MCU,满足开发人员的功能安全性 工业、医疗、汽车及交通运输设计需求-AET-电子技术应用 (chinaaet.com)

[13]NXP汽车MCU系列产品家族(Family)功能特性及应用介绍_汽车功能安全-商业新知 (shangyexinzhi.com)

[14] “安全岛”是什么?_智车科技-商业新知 (shangyexinzhi.com)

[注1] common cause failure共因失效CCF:一个或者多个故障源引起的多通道系统里两个或多个独立通道的失效。原因有很多:温湿度环境,粉尘,EMC等外部应力导致的随机硬件失效;或者是设计或规范错误导致的系统性故障引起等;或者是上述两种情况共同导致。其造成的故障结果不同。

common mode failure共模失效CMF:两个或者多个通道以相同的方式失效,导致了相同的故障结果。

[注2] 危险失效指的是在故障发生后,系统、设备或产品会处于一个会危及人身安全的状态。比如说,一辆汽车的制动系统失效,导致司机无法控制车速,这就是危险失效。

而安全失效则指在故障发生后,系统、设备或产品处于一个不会危及人身安全的状态,但是仍然会影响其正常使用或者造成财产损失。比如说,一台电视机的某个零部件出现故障,导致不能正常播放节目,这就是安全失效。

因此,危险失效和安全失效的区别在于故障发生后,是否会危及人身安全。

[注3] 现在很多芯片厂商都会宣称自己的芯片中有“安全岛”,但其实每家的概念都不完全统一。有的仅仅是在芯片中集成了带有“双核锁步”机制的Arm Cortex R-52安全系列内核;有的则是将外挂的安全MCU集成到SOC芯片中,可以认为这里的"安全内核"及周边满足安全需求设计的安全存储,安全外设,安全总线等一系列IP的集合称为“安全岛”,广义上就是一个安全的MCU被封装到了SOC中;

[注4] To avoid an erroneous CCM-R4 compare error, the application software must initialize the registers ofboth CPUs before the registers are used, including function calls where the register values are pushed onto the stack.