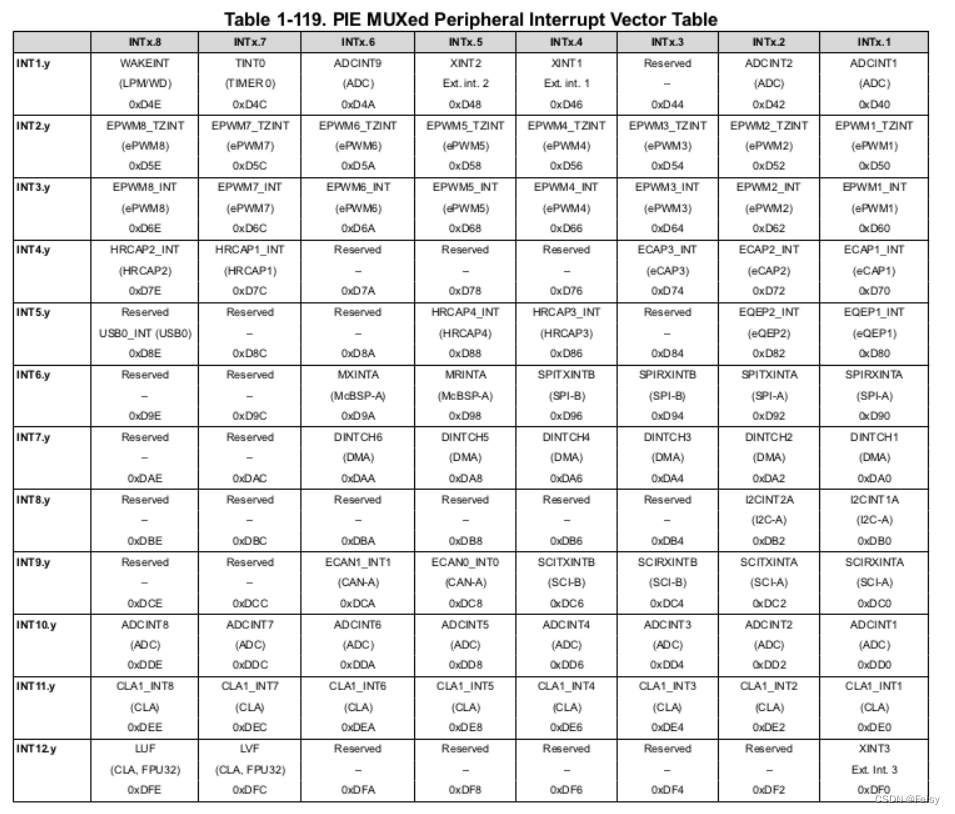

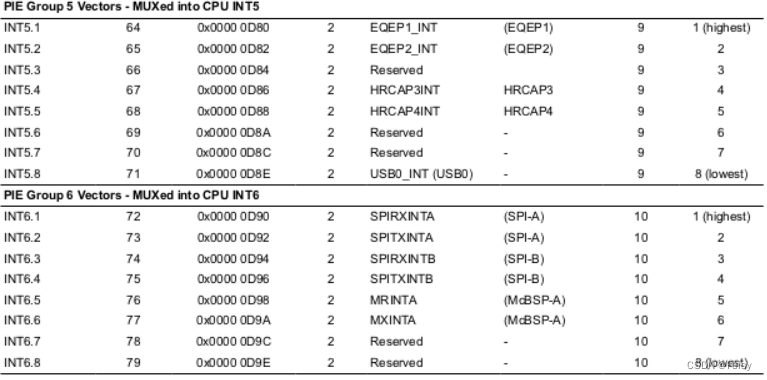

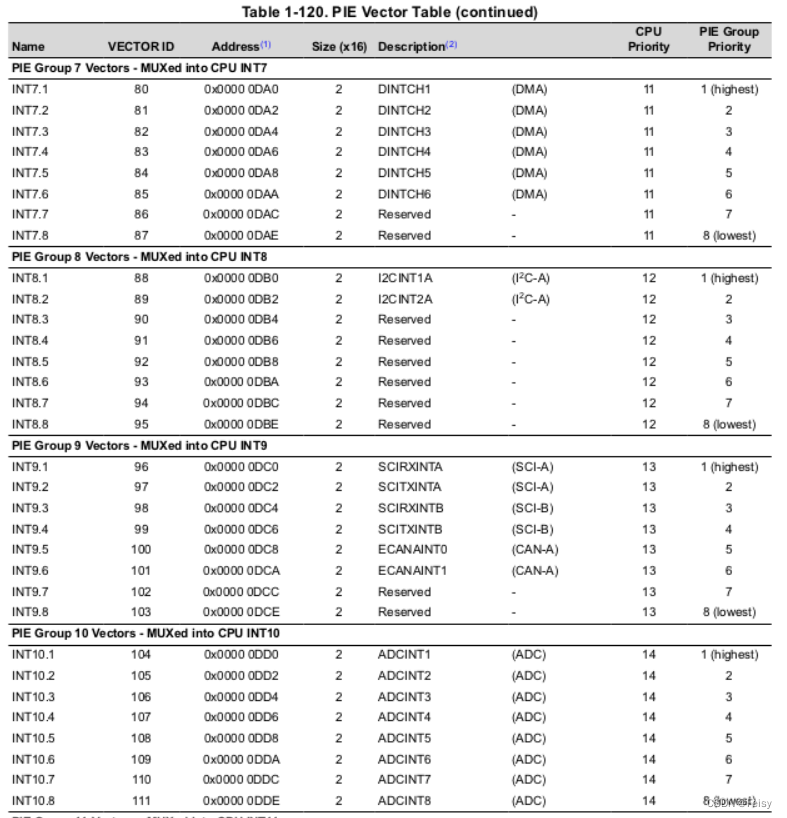

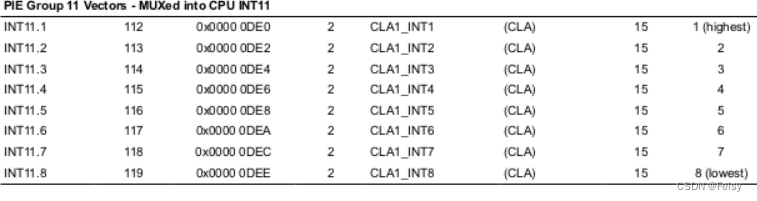

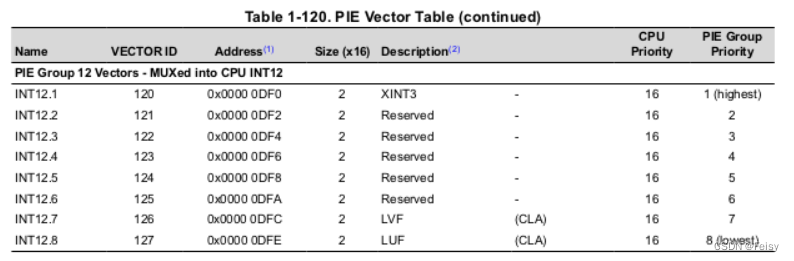

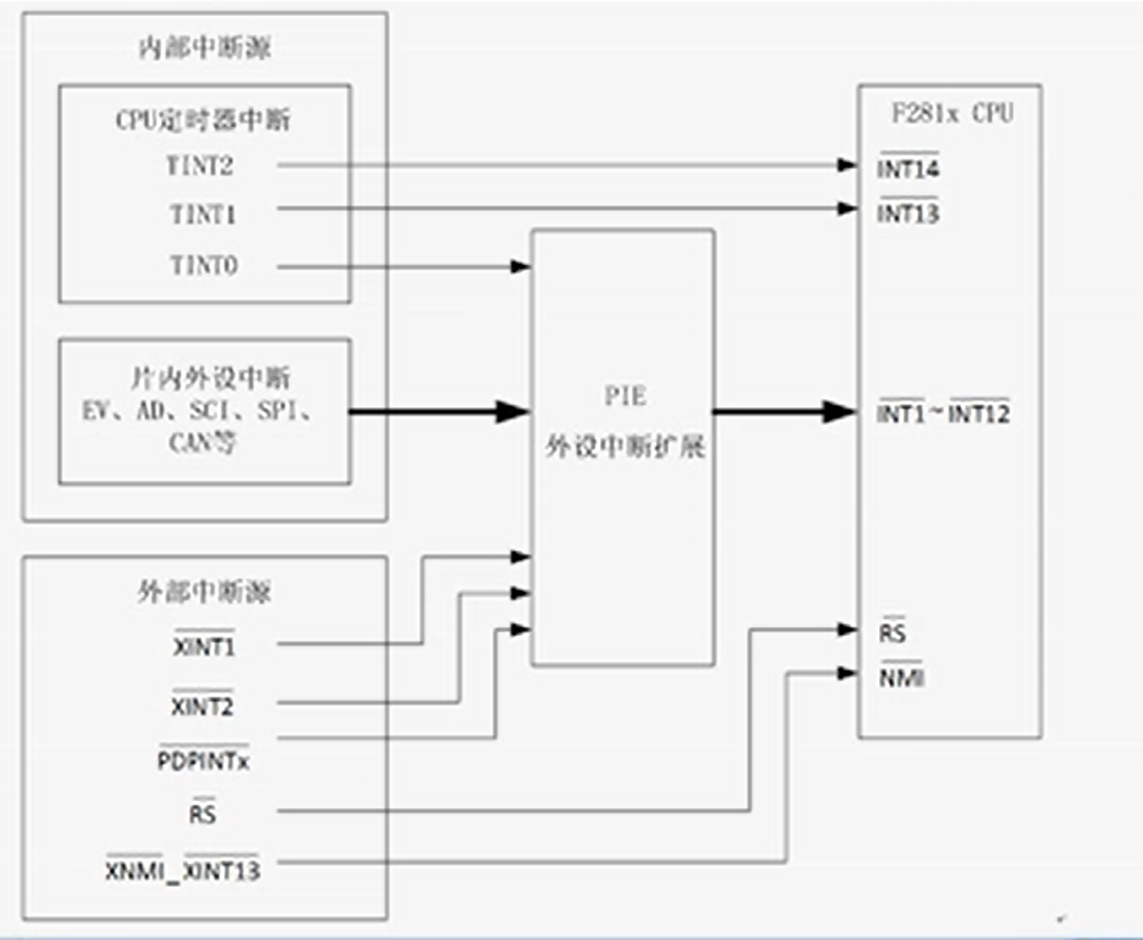

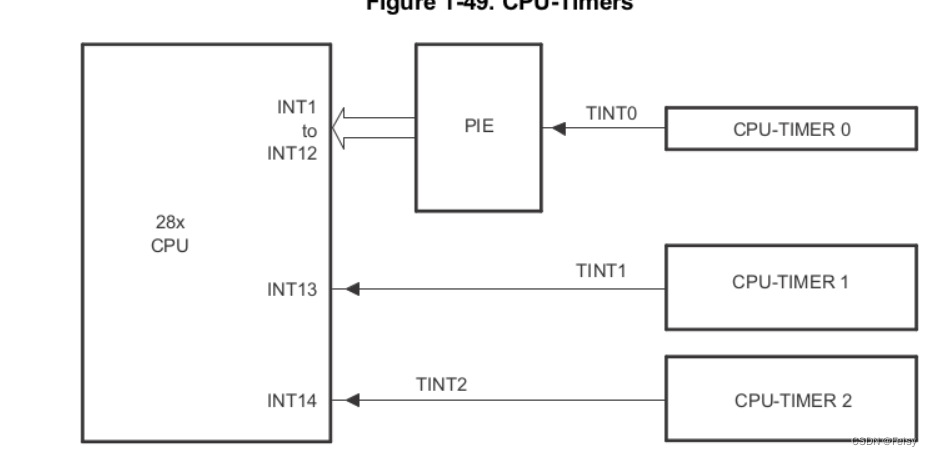

F28069的中断数是96个,分为12组

The PIE block can support 96 individual interrupts that are grouped into blocks of eight.Each

group is fed into one of 12 core interrupt lines (INT1 to INT12)

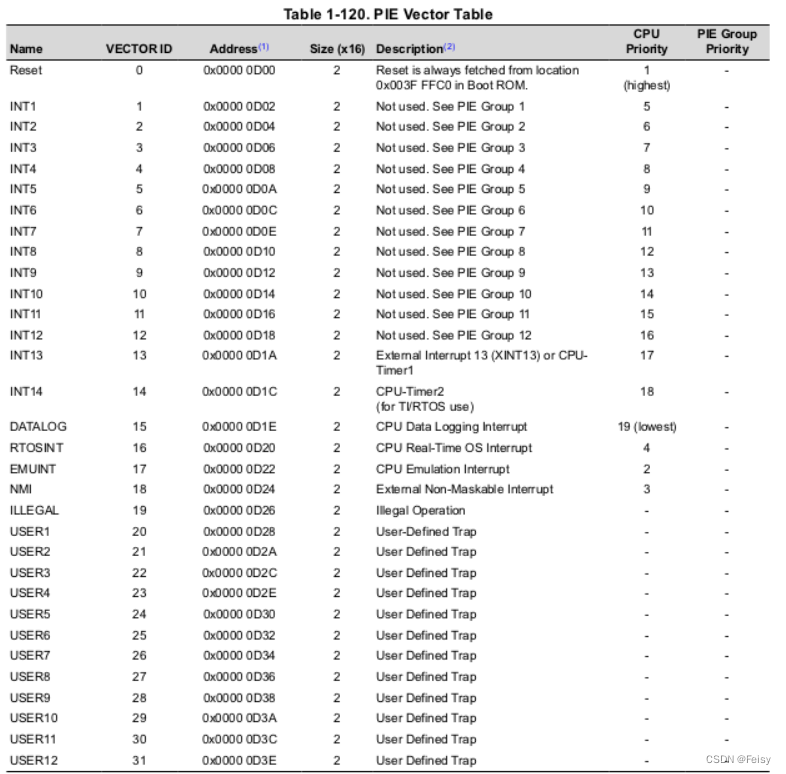

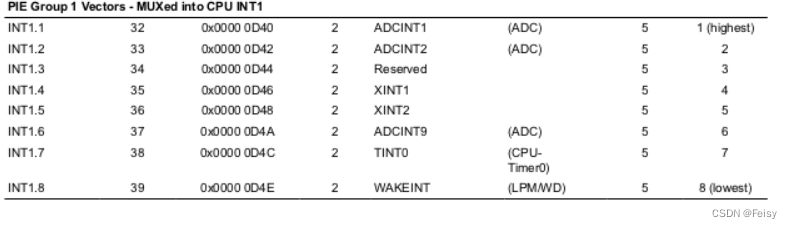

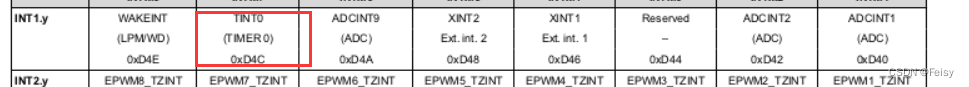

比如常用的的CPU0定时器这个中断就是在第一组的第7个,它在代码里面有个名字,TINT0

// Group 1 PIE Peripheral Vectors:

PINT ADCINT1; // ADC - if Group 10 ADCINT1 is enabled, this must be rsvd1_1

PINT ADCINT2; // ADC - if Group 10 ADCINT2 is enabled, this must be rsvd1_2

PINT rsvd1_3;

PINT XINT1; // External Interrupt 1

PINT XINT2; // External Interrupt 2

PINT ADCINT9; // ADC 9

PINT TINT0; // Timer 0

PINT WAKEINT; // WD

F28069在代码里的中断定义

// Define Vector Table:

struct PIE_VECT_TABLE {

// Reset is never fetched from this table.

// It will always be fetched from 0x3FFFC0 in

// boot ROM

PINT PIE1_RESERVED;

PINT PIE2_RESERVED;

PINT PIE3_RESERVED;

PINT PIE4_RESERVED;

PINT PIE5_RESERVED;

PINT PIE6_RESERVED;

PINT PIE7_RESERVED;

PINT PIE8_RESERVED;

PINT PIE9_RESERVED;

PINT PIE10_RESERVED;

PINT PIE11_RESERVED;

PINT PIE12_RESERVED;

PINT PIE13_RESERVED;

// Non-Peripheral Interrupts:

PINT TINT1; // CPU-Timer1

PINT TINT2; // CPU-Timer2

PINT DATALOG; // Datalogging interrupt

PINT RTOSINT; // RTOS interrupt

PINT EMUINT; // Emulation interrupt

PINT NMI; // Non-maskable interrupt

PINT ILLEGAL; // Illegal operation TRAP

PINT USER1; // User Defined trap 1

PINT USER2; // User Defined trap 2

PINT USER3; // User Defined trap 3

PINT USER4; // User Defined trap 4

PINT USER5; // User Defined trap 5

PINT USER6; // User Defined trap 6

PINT USER7; // User Defined trap 7

PINT USER8; // User Defined trap 8

PINT USER9; // User Defined trap 9

PINT USER10; // User Defined trap 10

PINT USER11; // User Defined trap 11

PINT USER12; // User Defined trap 12

// Group 1 PIE Peripheral Vectors:

PINT ADCINT1; // ADC - if Group 10 ADCINT1 is enabled, this must be rsvd1_1

PINT ADCINT2; // ADC - if Group 10 ADCINT2 is enabled, this must be rsvd1_2

PINT rsvd1_3;

PINT XINT1; // External Interrupt 1

PINT XINT2; // External Interrupt 2

PINT ADCINT9; // ADC 9

PINT TINT0; // Timer 0

PINT WAKEINT; // WD

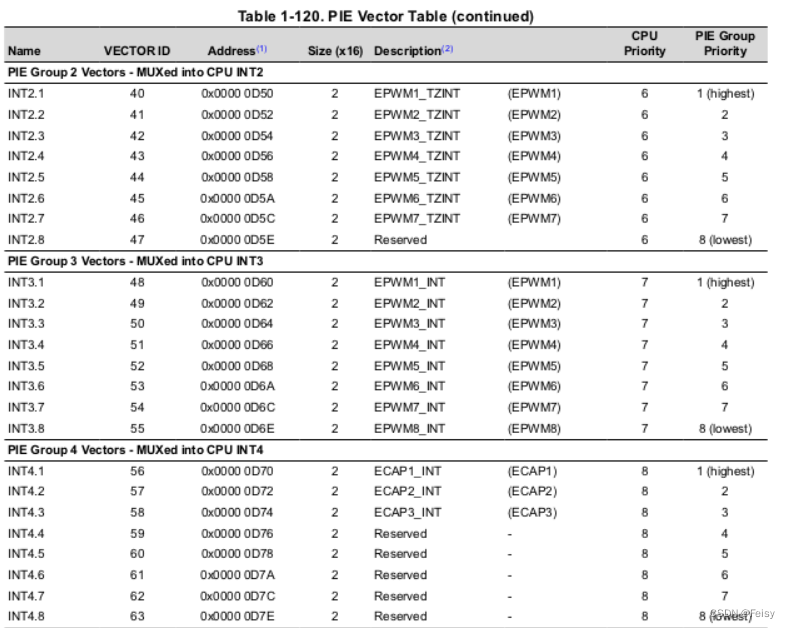

// Group 2 PIE Peripheral Vectors:

PINT EPWM1_TZINT; // EPWM-1

PINT EPWM2_TZINT; // EPWM-2

PINT EPWM3_TZINT; // EPWM-3

PINT EPWM4_TZINT; // EPWM-4

PINT EPWM5_TZINT; // EPWM-5

PINT EPWM6_TZINT; // EPWM-6

PINT EPWM7_TZINT; // EPWM-7

PINT EPWM8_TZINT; // EPWM-8

// Group 3 PIE Peripheral Vectors:

PINT EPWM1_INT; // EPWM-1

PINT EPWM2_INT; // EPWM-2

PINT EPWM3_INT; // EPWM-3

PINT EPWM4_INT; // EPWM-4

PINT EPWM5_INT; // EPWM-5

PINT EPWM6_INT; // EPWM-6

PINT EPWM7_INT; // EPWM-7

PINT EPWM8_INT; // EPWM-8

// Group 4 PIE Peripheral Vectors:

PINT ECAP1_INT; // ECAP-1

PINT ECAP2_INT; // ECAP-2

PINT ECAP3_INT; // ECAP-3

PINT rsvd4_4;

PINT rsvd4_5;

PINT rsvd4_6;

PINT HRCAP1_INT; // HRCAP-1

PINT HRCAP2_INT; // HRCAP-2

// Group 5 PIE Peripheral Vectors:

PINT EQEP1_INT; // EQEP-1

PINT EQEP2_INT; // EQEP-2

PINT rsvd5_3;

PINT HRCAP3_INT; // HRCAP-3

PINT HRCAP4_INT; // HRCAP-4

PINT rsvd5_6;

PINT rsvd5_7;

PINT USB0_INT; // USB-0

// Group 6 PIE Peripheral Vectors:

PINT SPIRXINTA; // SPI-A

PINT SPITXINTA; // SPI-A

PINT SPIRXINTB; // SPI-B

PINT SPITXINTB; // SPI-B

PINT MRINTA; // McBSP-A

PINT MXINTA; // McBSP-A

PINT rsvd6_7;

PINT rsvd6_8;

// Group 7 PIE Peripheral Vectors:

PINT DINTCH1; // DMA CH1

PINT DINTCH2; // DMA CH2

PINT DINTCH3; // DMA CH3

PINT DINTCH4; // DMA CH4

PINT DINTCH5; // DMA CH5

PINT DINTCH6; // DMA CH6

PINT rsvd7_7;

PINT rsvd7_8;

// Group 8 PIE Peripheral Vectors:

PINT I2CINT1A; // I2C-A

PINT I2CINT2A; // I2C-A

PINT rsvd8_3;

PINT rsvd8_4;

PINT rsvd8_5;

PINT rsvd8_6;

PINT rsvd8_7;

PINT rsvd8_8;

// Group 9 PIE Peripheral Vectors:

PINT SCIRXINTA; // SCI-A

PINT SCITXINTA; // SCI-A

PINT SCIRXINTB; // SCI-B

PINT SCITXINTB; // SCI-B

PINT ECAN0INTA; // eCAN-A

PINT ECAN1INTA; // eCAN-A

PINT rsvd9_7;

PINT rsvd9_8;

// Group 10 PIE Peripheral Vectors:

PINT rsvd10_1; // Can be ADCINT1, but must make ADCINT1 in Group 1 space "reserved".

PINT rsvd10_2; // Can be ADCINT2, but must make ADCINT2 in Group 1 space "reserved".

PINT ADCINT3; // ADC

PINT ADCINT4; // ADC

PINT ADCINT5; // ADC

PINT ADCINT6; // ADC

PINT ADCINT7; // ADC

PINT ADCINT8; // ADC

// Group 11 PIE Peripheral Vectors:

PINT CLA1_INT1; // CLA

PINT CLA1_INT2; // CLA

PINT CLA1_INT3; // CLA

PINT CLA1_INT4; // CLA

PINT CLA1_INT5; // CLA

PINT CLA1_INT6; // CLA

PINT CLA1_INT7; // CLA

PINT CLA1_INT8; // CLA

// Group 12 PIE Peripheral Vectors:

PINT XINT3;

PINT rsvd12_2;

PINT rsvd12_3;

PINT rsvd12_4;

PINT rsvd12_5;

PINT rsvd12_6;

PINT LVF; // Latched overflow

PINT LUF; // Latched underflow

};

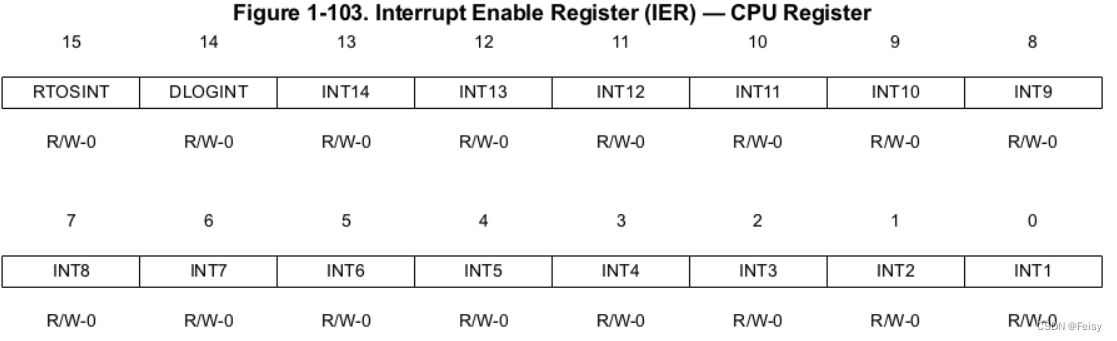

CPU 中断使能寄存器IER(interrup enable register)

该寄存器用来配置是否启用中断

The interrupt flag (IF) bit corresponding to that event is

set in a register for that particular peripheral.

If the corresponding interrupt enable (IE) bit is set, the peripheral generates an interrupt request to the PIE

controller. If the interrupt is not enabled at the peripheral level, then the IF remains set until cleared by

software. If the interrupt is enabled

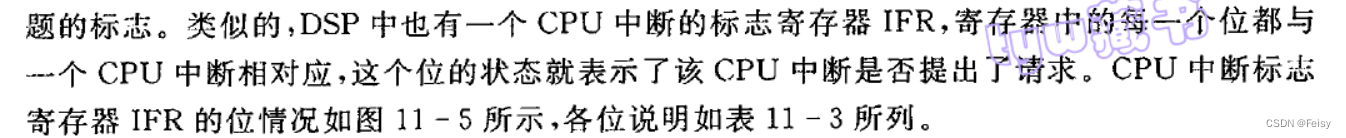

中断是可以启用和禁止的,者通过IER,IFR两个寄存器来操作,比如一般程序开头,我们会禁用所有中断:

//

// Disable CPU interrupts and clear all CPU interrupt flags

//

IER = 0x0000;

IFR = 0x0000;//清除标志,表示一开始没有任何中断发生

启用中断的话,给IER或上值,比如,启用cup0,1,2,启用了int1,int13,int14这三个组的中断

// Enable CPU int1 which is connected to CPU-Timer 0, CPU int13

// which is connected to CPU-Timer 1, and CPU int 14, which is connected

// to CPU-Timer 2:

IER |= M_INT1;

IER |= M_INT13;

IER |= M_INT14;

// Enable TINT0 in the PIE: Group 1 interrupt 7

PieCtrlRegs.PIEIER1.bit.INTx7 = 1;

CPU 中断标志寄存器IFR(interrup flag register)

该寄存器用来表示,那个中断发生了。如果中断发生,IFR该中断的位会自动置1.

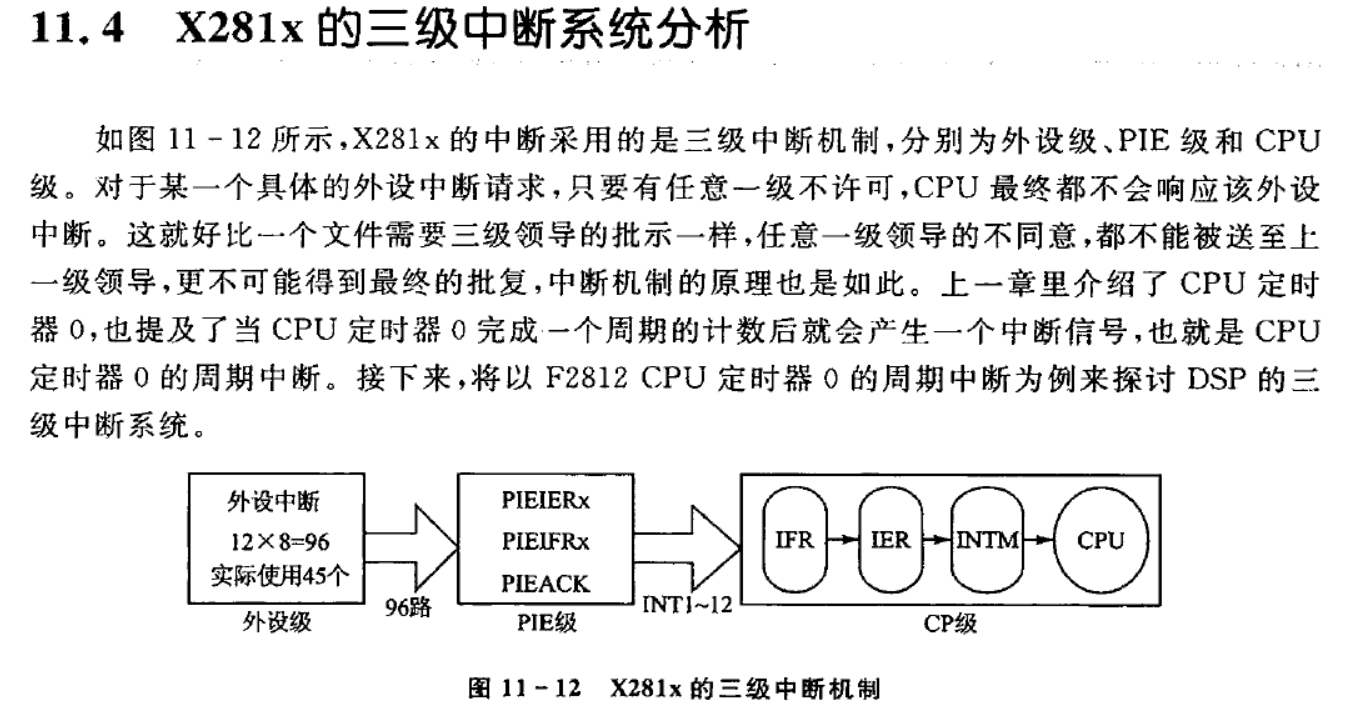

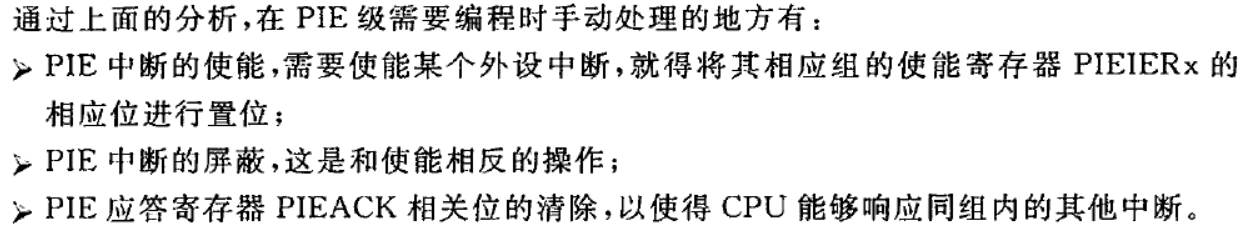

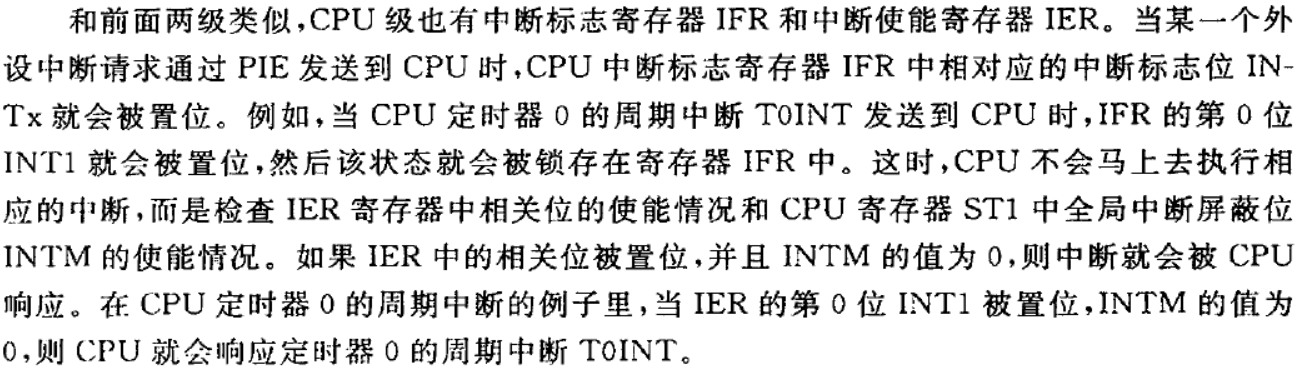

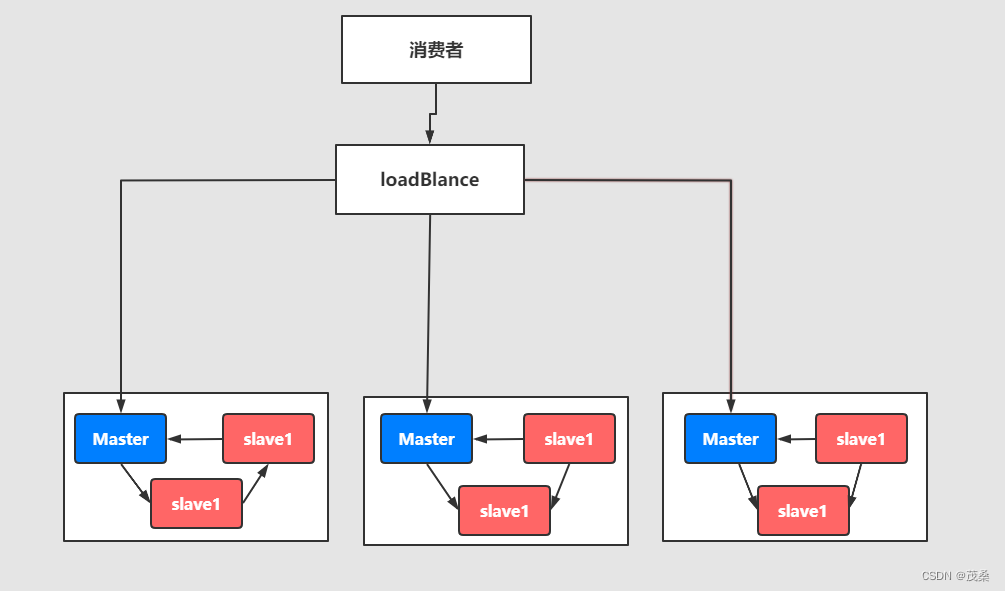

三级中断系统

外设级

PIE级

CPU级

三级中断总结图

中断源图示

注意,改图是2812系列的,跟F28069有点不同,比如28069的timer0,1是可被用户使用的,如果没有用到DSP/BIOS,timer2也可以被用户使用

![[附源码]计算机毕业设计通用病例管理系统Springboot程序](https://img-blog.csdnimg.cn/8b9f11332f124e7ba56b03464a1a47a7.png)

![[激光原理与应用-37]:《光电检测技术-4》- 光学测量基础 - 噪声与光学中的常见电路](https://img-blog.csdnimg.cn/33a386a5161a4f6db8816f0f8e66007e.png)