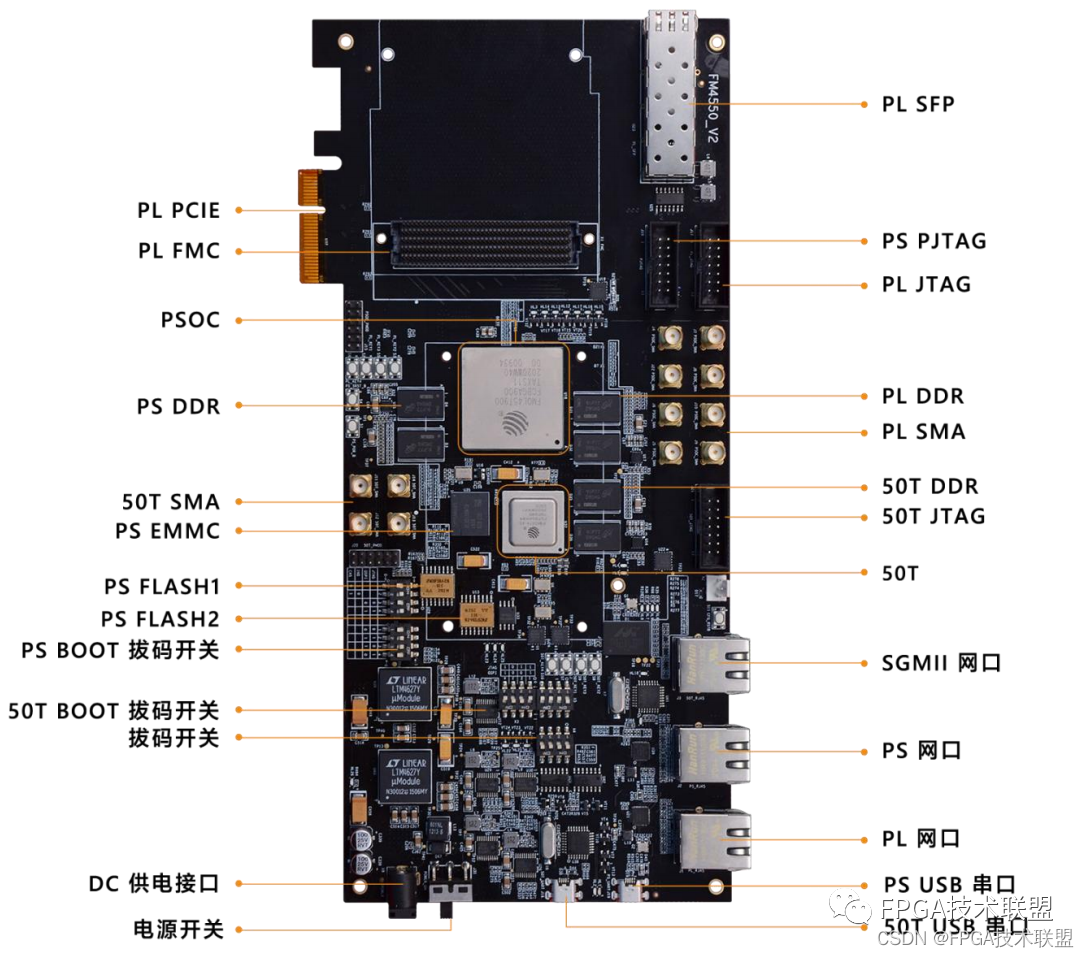

本教程采用 FMQL7045 FPGA开发板来完成整个试验,板卡照片如下:

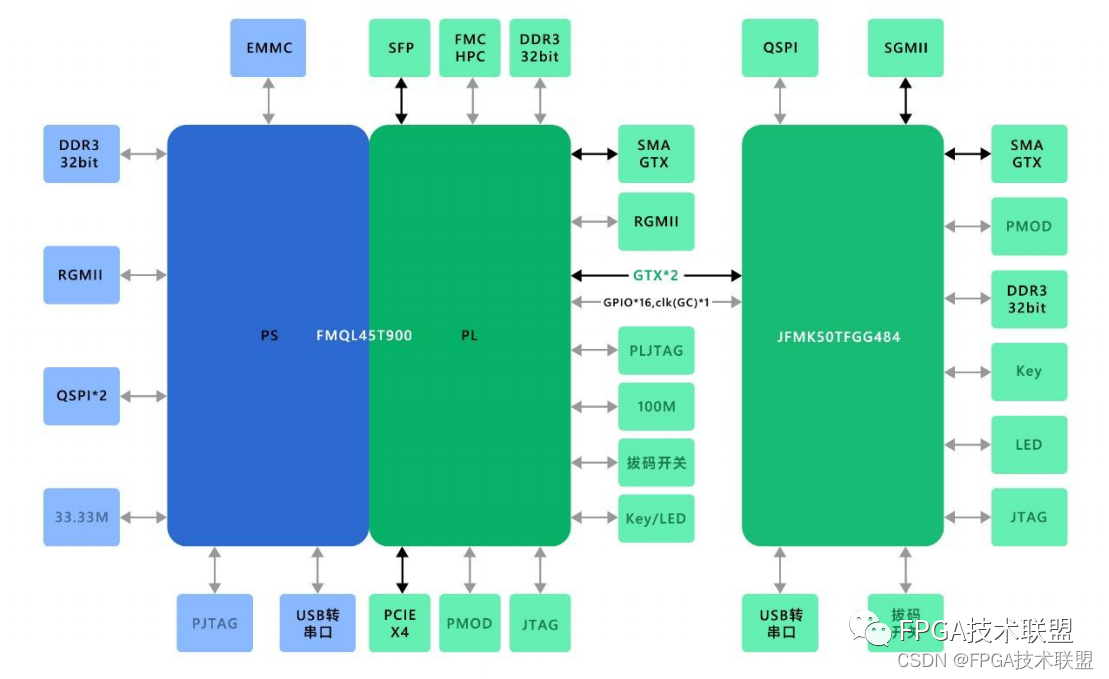

具有丰富的接口资源,系统框图如下:

本教程用于完成基于Vivado的FMQL45的LED实验,目标是能够将这款开发板PL端先跑起来。

对于纯 PL 设计,我们的 FMQL45 和 Zynq7045 是管脚全兼容,所以可以直接使用 Vivado 进行逻辑开发,对于简单的逻辑也可以使用 Procise 开发,但是如果要大量使用 IPcore,推荐使用 Vivado 。

这边先介绍 Vivado 流程。

实验 Vivado 工程为“00_led”。本例程主要实现的功能是每秒钟控制扩展板上的8 个 LED 灯翻转一次。

1 LED硬件介绍

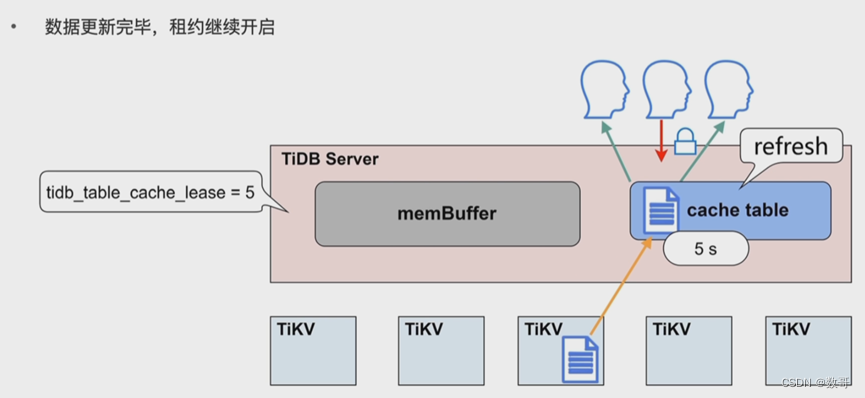

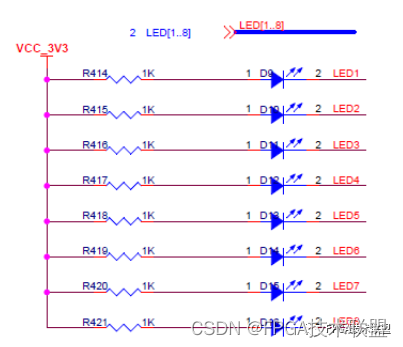

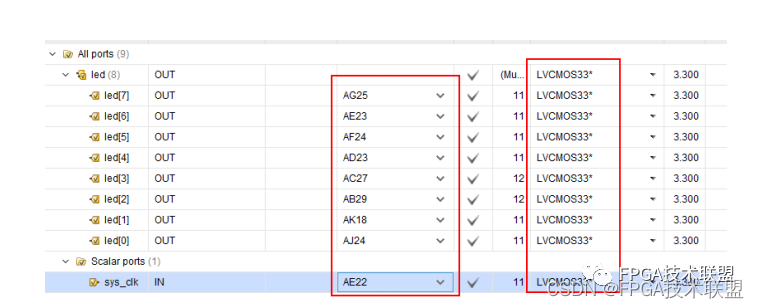

PL 端只能直接控制 PL 侧的 LED 灯,无法直接控制 PS 端的外设。8 颗 LED 灯通过三极管连接到 3.3V 电源,当三极管导通 LED 就会亮。结合核心板和扩展板的原理图,我们可以看到 8 个 LED 对应 FMQL45 芯片的管脚情况如下所示:

LED1 --- AJ24

LED2 --- AK18

LED3 --- AB29

LED4 --- AC27

LED5 --- AD23

LED6 --- AF24

LED7 --- AE23

LED8 --- AG25

2 Vivado工程建立

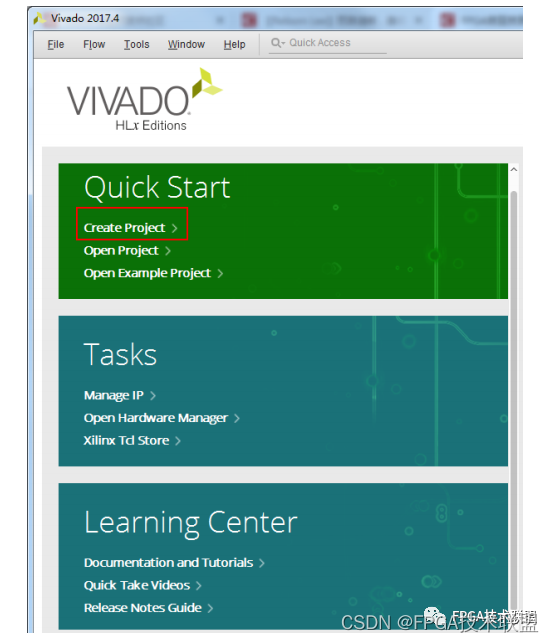

(1)在 Windows 中可以双击 Vivado 快捷方式启动 Vivado。

(2)在 Vivado 开发环境中点击“Create Project”可以创建一个新工程。

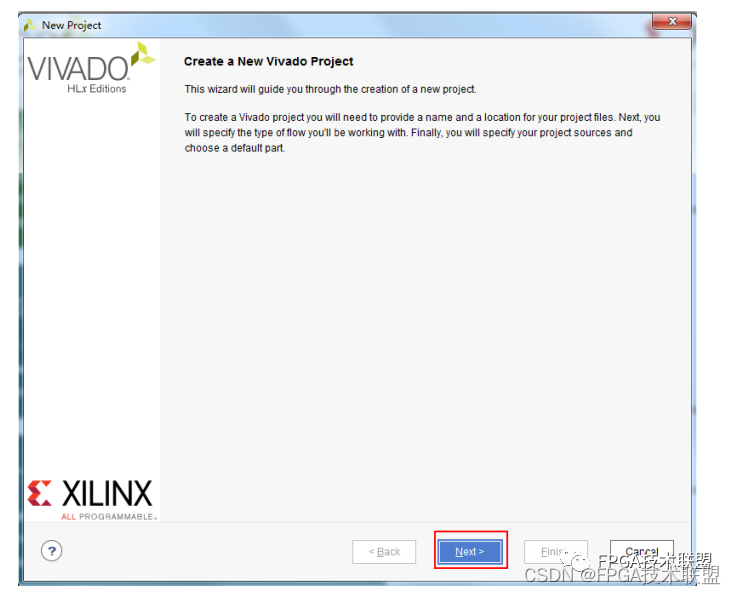

(3)弹出建立新工程的向导,点击“Next”

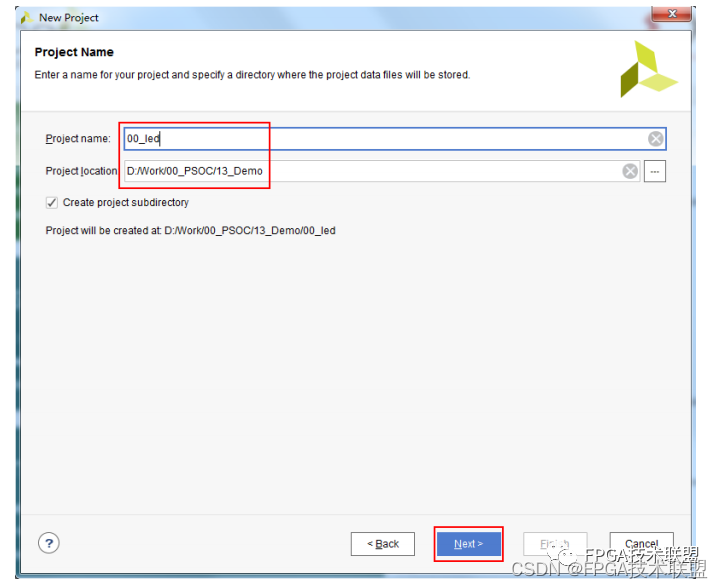

(4)在弹出的对话框中输入工程名和工程存放路径,我们这里取名叫 00_led。需要注意工程路径“Project location”中不能有中文空格,路径名最好也不要太长。然后点击 Next。

(5)在工程类型中选择“RTL Project”。

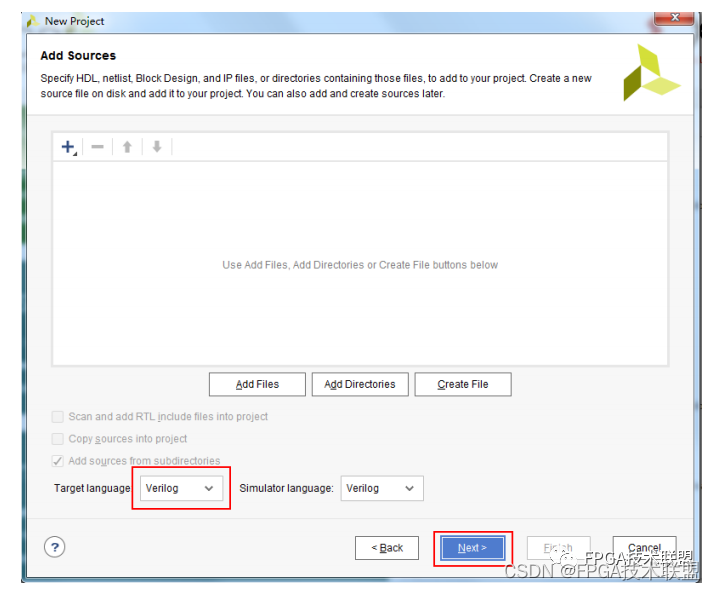

(6)Target language 选择“Verilog”。

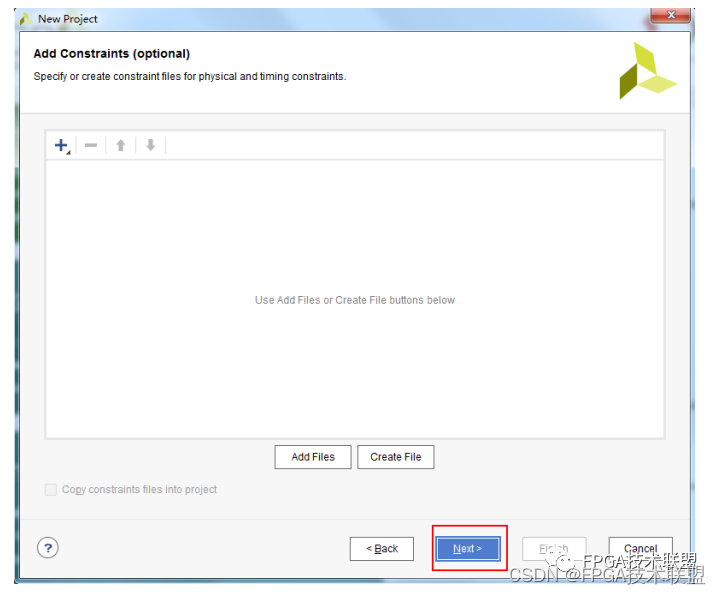

(7)点击“Next”,不添加任何文件,后续再补充。

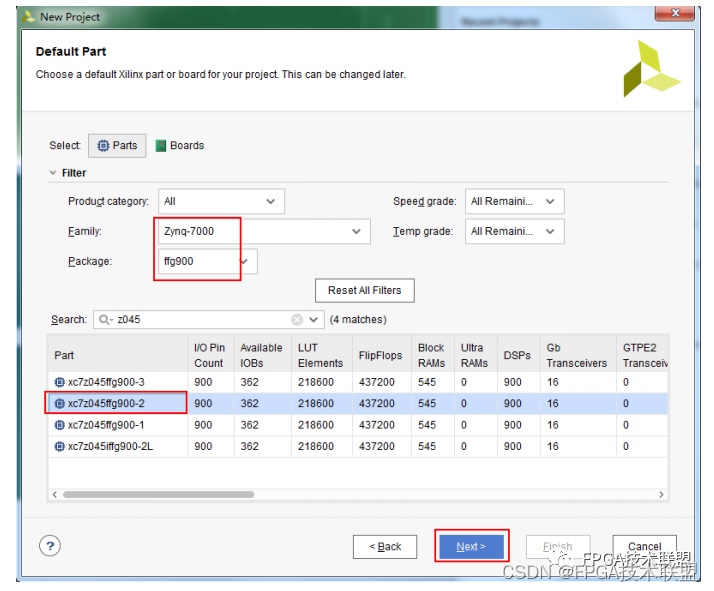

(8)筛选出 xc7z045ffg900-2 器件并选择,点击“Next”。

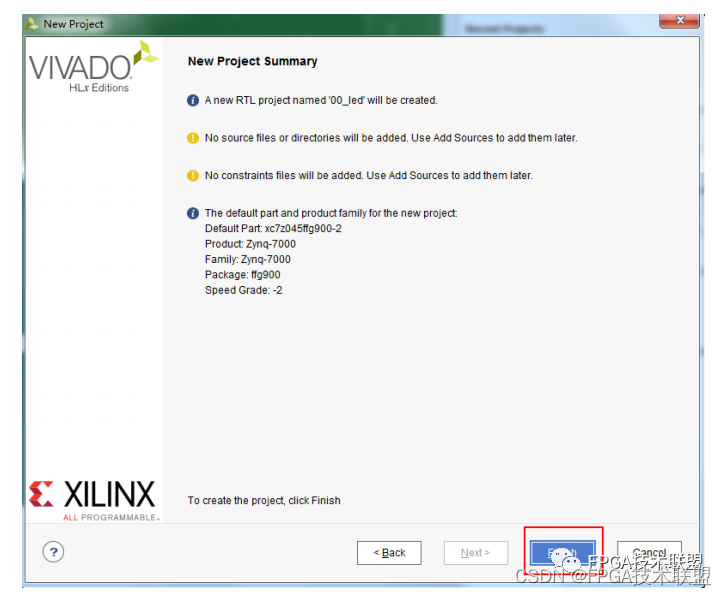

(9)点击“Finish”即可完成“led”工程的创建。

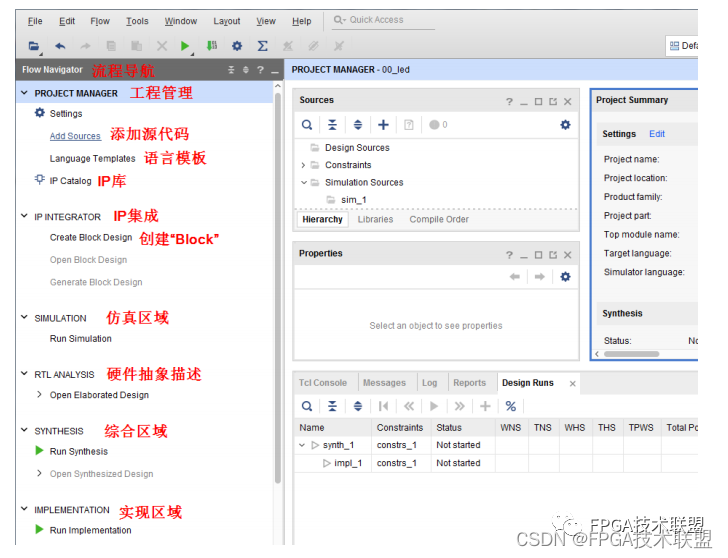

(10)下图为 Vivado 的软件界面。

3 创建Verilog HDL文件

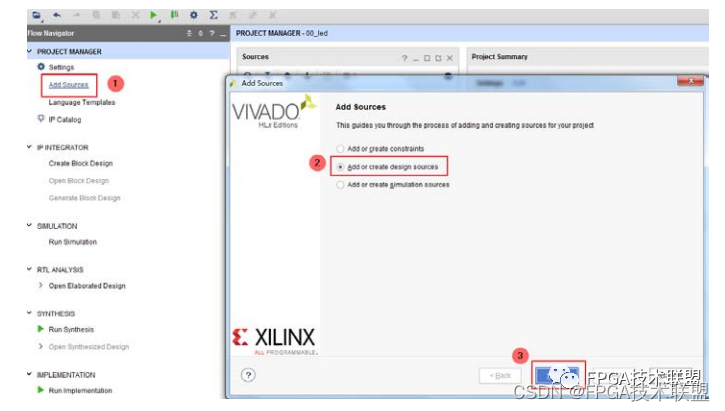

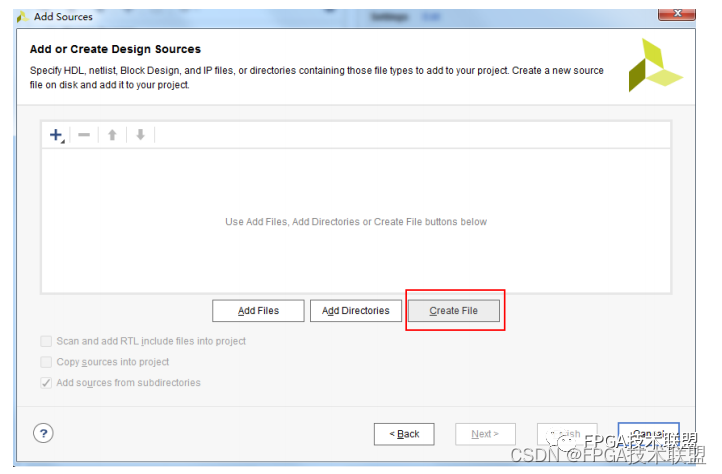

(1)点击 Project Manager 下面的 Add Sources 图标,选择添加或者创建设计源文件“Add or create design sources”,然后点击“Next”。

(2)选择创建文件“Create File”

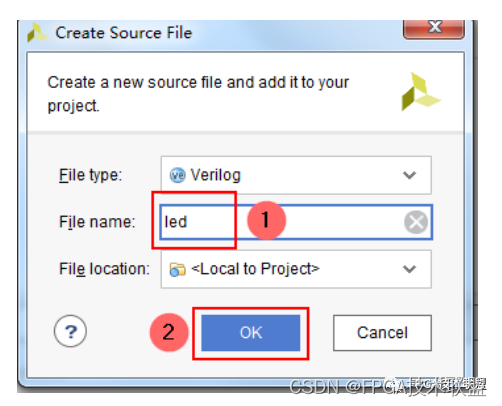

(3)弹出的窗口里,设置“File name”为“led”后点击“OK”。

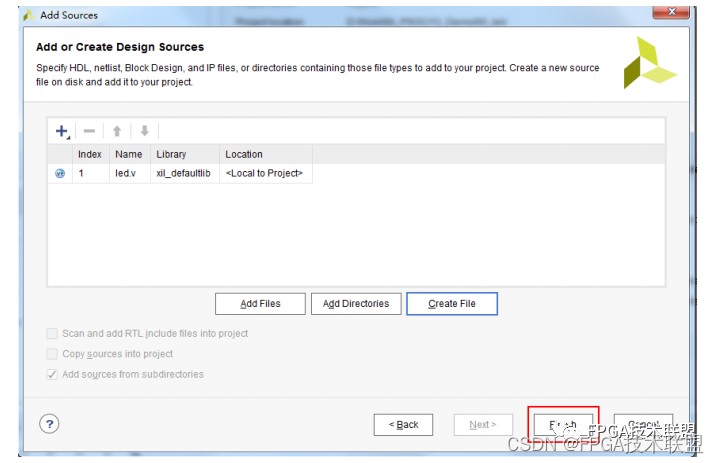

(4)点击“Finish”就完成了“led.v”文件的添加。

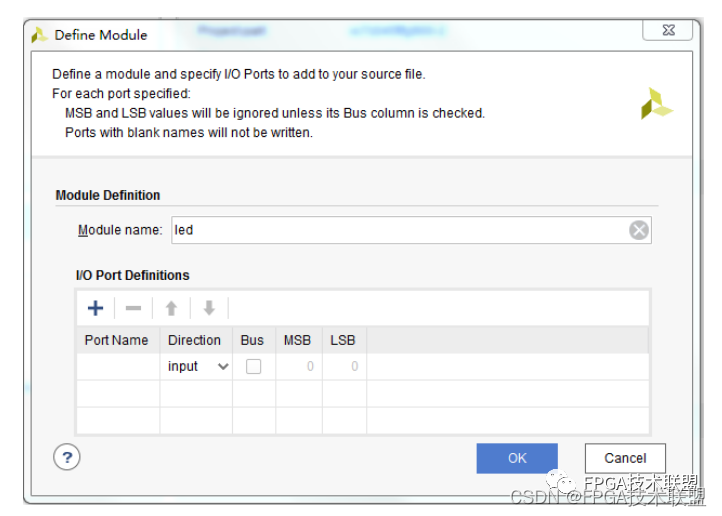

(5)这个时候在弹出的窗口上可以指定“Module name”,这里我们按照默认的就好了,点击“OK”。

(5)这个时候在弹出的窗口上可以指定“Module name”,这里我们按照默认的就好了,点击“OK”。

(6)在弹出的对话框里选择“Yes”。

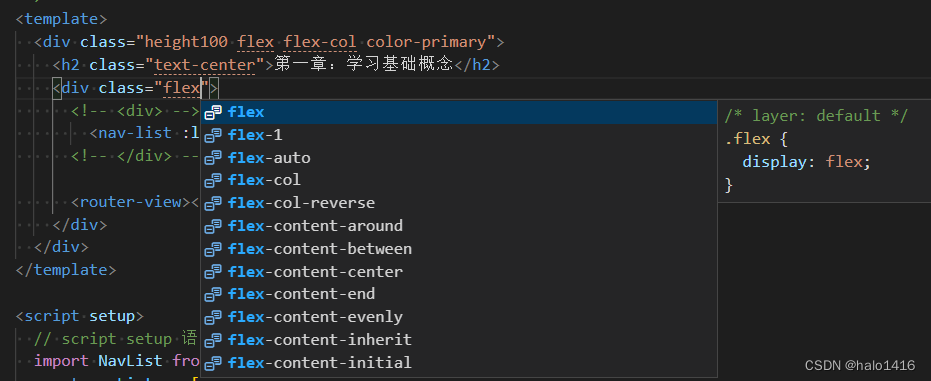

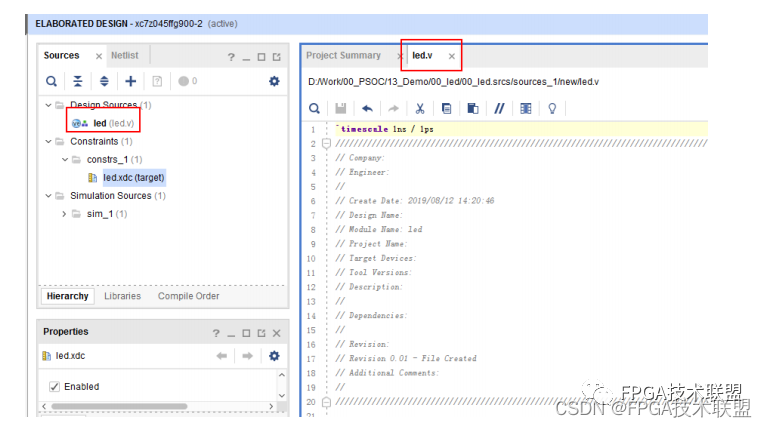

(7)双击“led.v”即可编辑该文件。

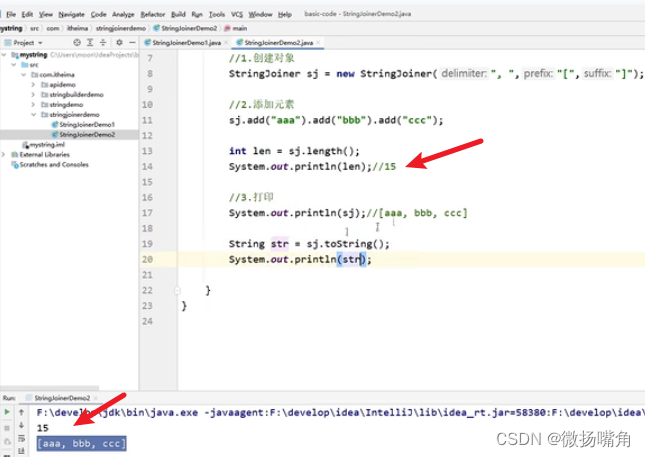

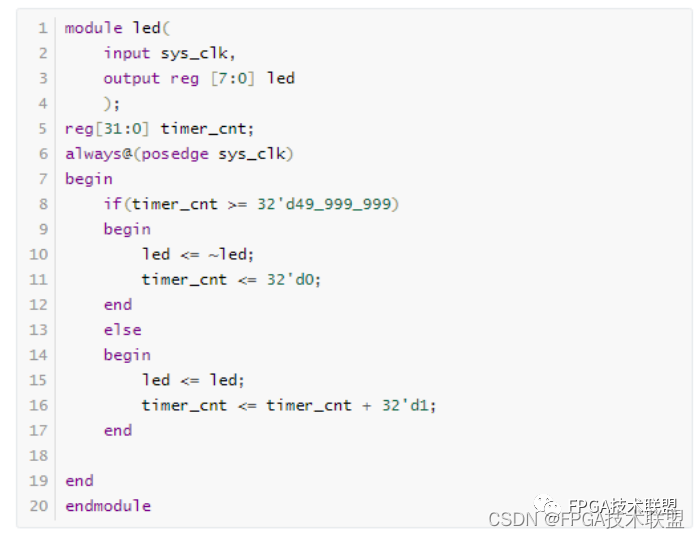

(8)编写一段“led.v”逻辑代码,这里定义了一个 32 位的寄存器 timer,用于循环计数 0~499999999(1 秒),计数到 499999999 的时候,timer 变 0,并翻转 8 个LED 灯。在硬件上表现为 LED 会每秒钟切换一次亮灭状态。编写完代码后记得保存,源代码如下图:

4 添加管脚约束

Vivado 上我们使用的约束文件为 XDC 格式,里面主要完成管脚的约束、时钟的约束和组的约束。这里需要对 led.v 程序中的输入输出端口分配到 FPGA 的真实管脚上。

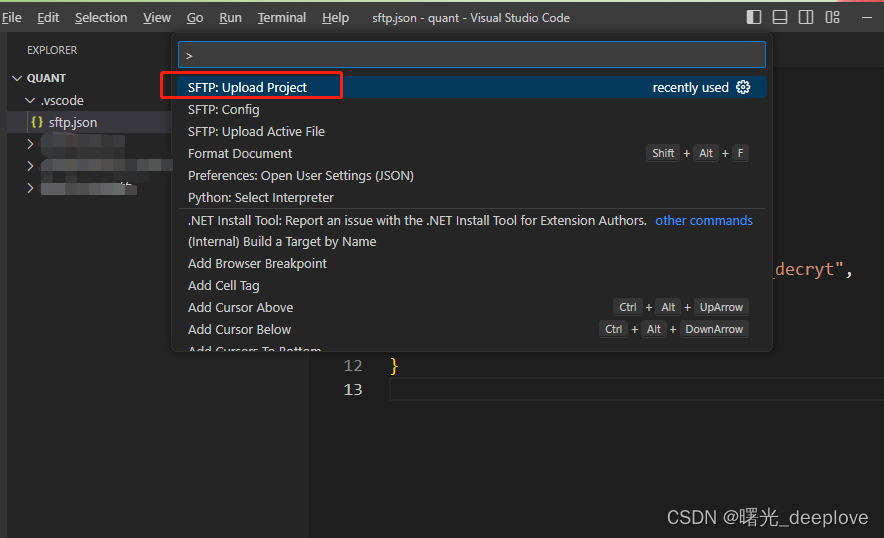

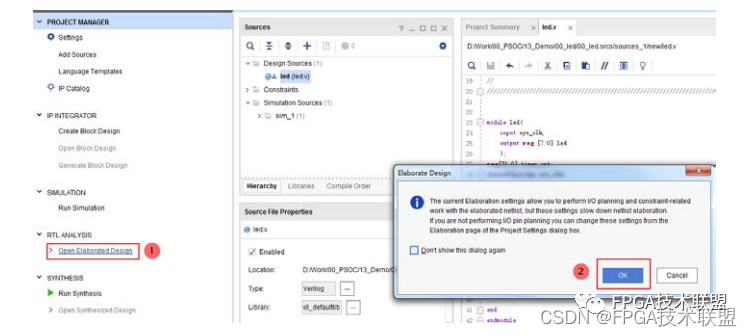

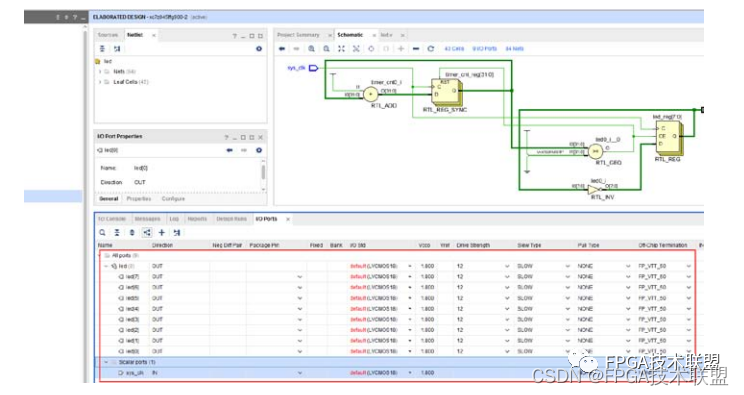

(1)点击“Open Elaborated Design”,在弹出的窗口上点击“OK”。

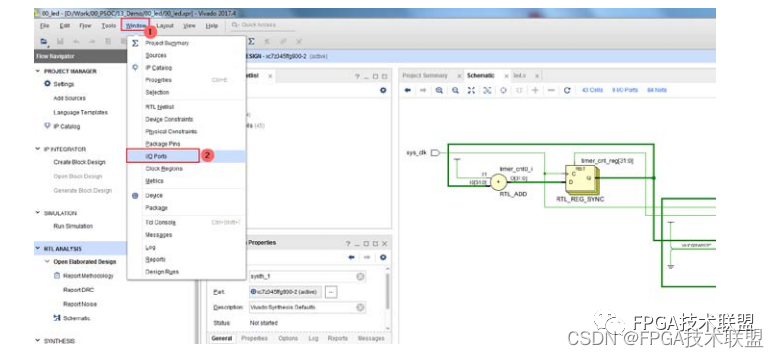

(2)菜单中选择“Window --> I/O Ports”

(3)在弹出的 I/O Ports 中可以看到管脚分配情况。

(4)给 LED 和时钟分频管脚和电平标准,完成后保存。这块的分配请看原理图确定。

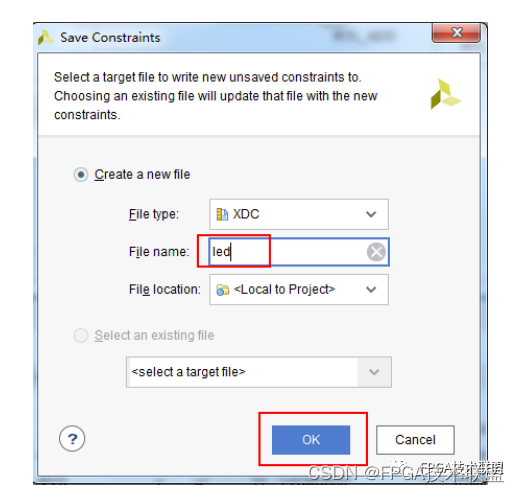

(5)弹出窗口要求保存约束文件,文件名我们填写“led”,文件类型默认“XDC”,点击“OK”。

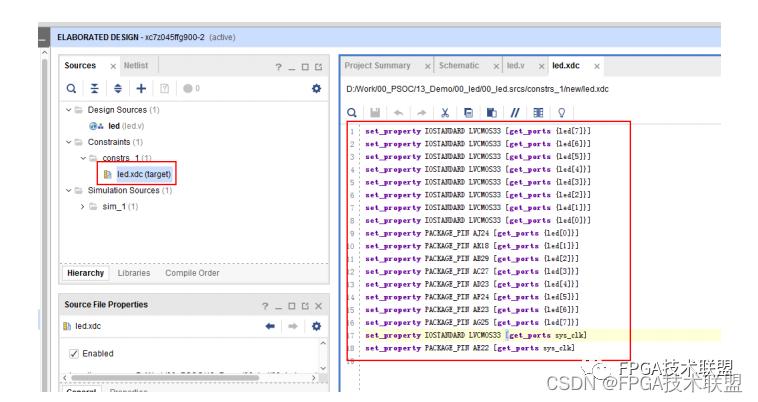

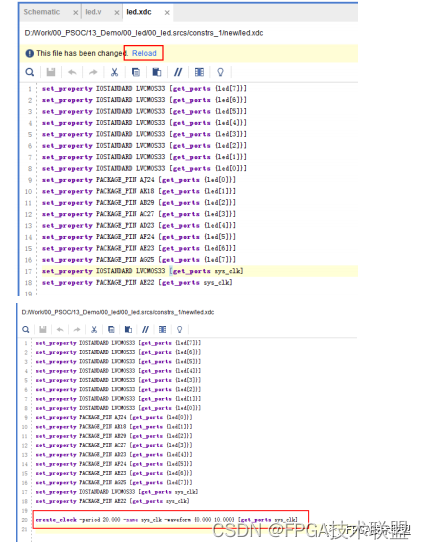

(6)打开刚刚生成的“led.xdc”可以看到相关的 TCL 脚本,这些其实我们在熟悉相关语法后都可以自己直接写,不用通过上面的图形化界面生成。相关语法请开发人员自己去熟悉和学习,这里不再赘述。

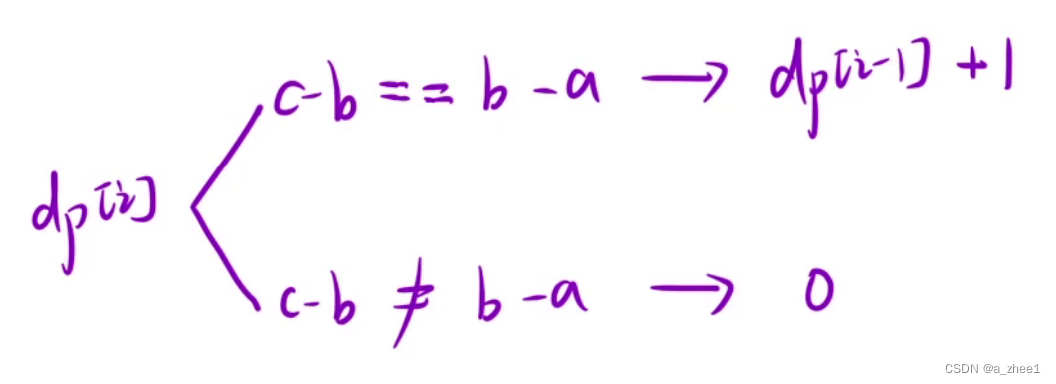

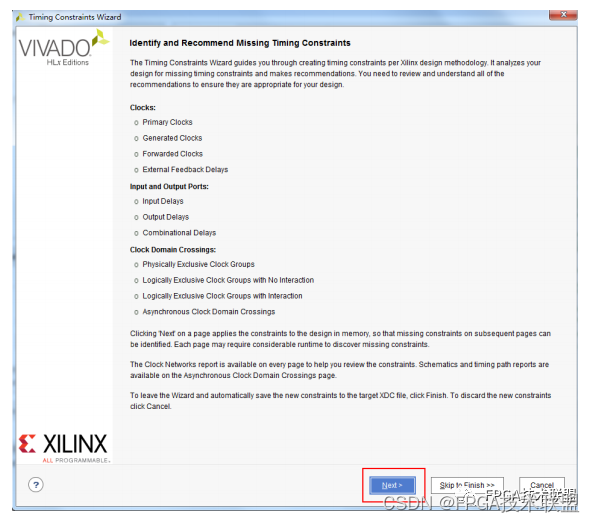

一个 FPGA 设计除了管脚约束外还有时序约束,这里通过向导方式演示如何进行时序约束。

(1)点击“Run Synthesis”开始综合流程。

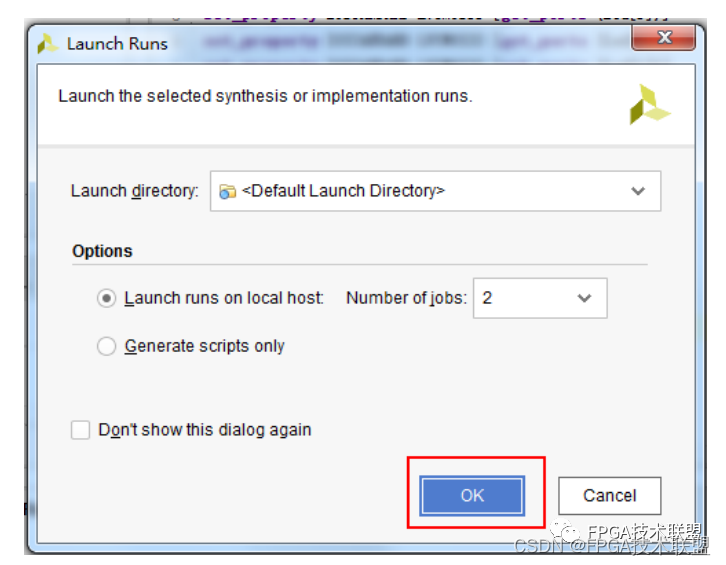

(2)弹出的对话框点击“OK”。

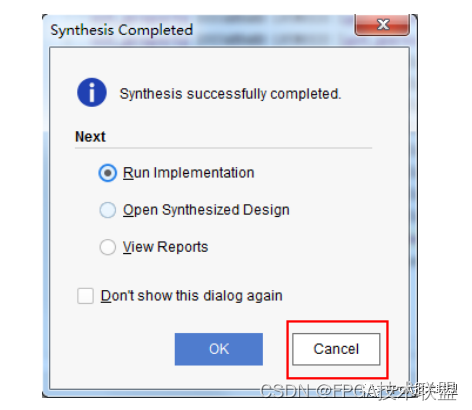

(3)综合完成后点击“Cancel”。

(4)点击“Constrain Wizard”

(5)在弹出的窗口点击“Next”

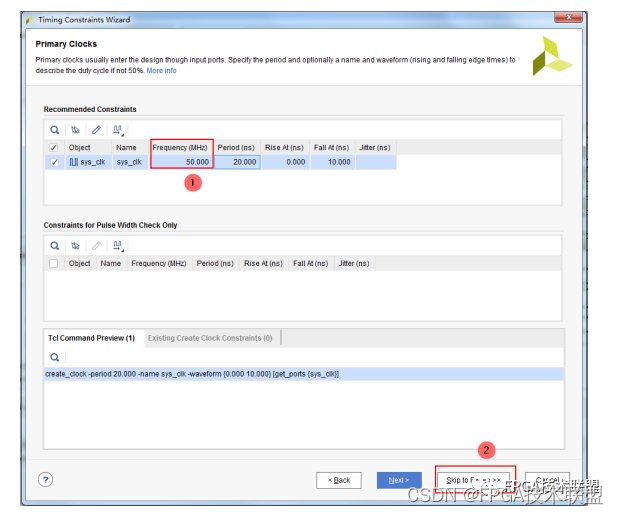

(6)把“sys_clk”频率设置为 50MHz,然后点击“Skip to Finish”结束时序约束向导。

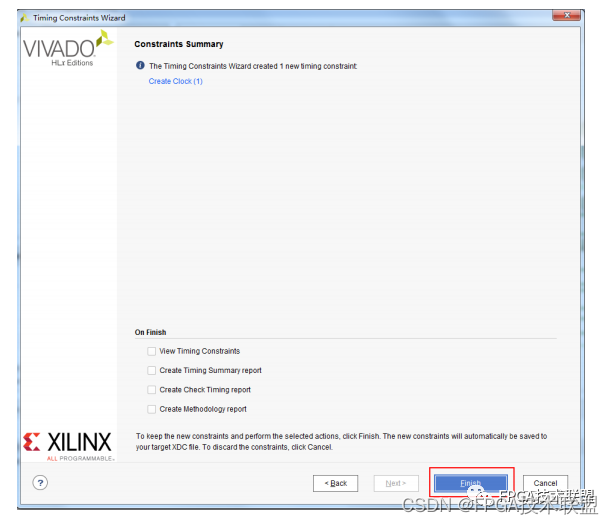

(7)点击“Finish”

(8)这个时候 led.xdc 就更新了,点击“Reload”可以重新加载文件。可以看到最后一行加上了时钟约束。

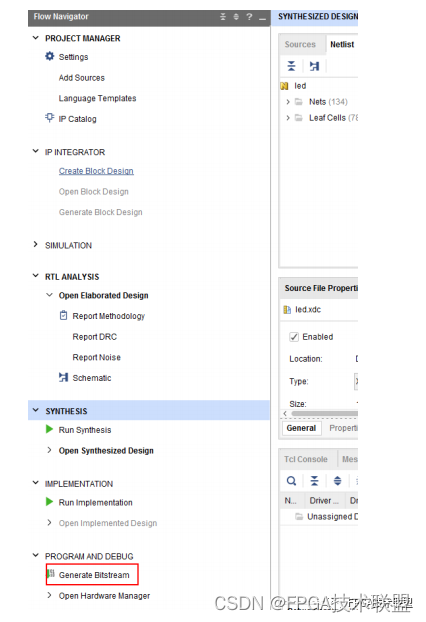

6 生成BIT位流

(1)编译过程可以分为综合、布局布线、生成 bit 位流等,这里我们直接点击“Generate Bitstream”就可以直接一键式生成 bit 位流。

(2)在弹出的对话框中选择任务数量,这里和 CPU 核心数相关,一般设置数字越大编译越快,但是占用的系统资源越多。这里需要用户自己衡量,这里我们就按照默认的,直接点击“OK”。

(3)开始编译,软件右上角有编译状态信息。

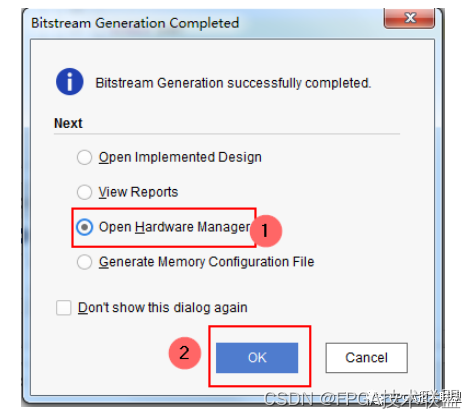

(4)编译如果没有任何错误,会弹出一个对话框让我们选择后续操作,我们这里选择“Open Hardware Manger”然后点击“OK”去下载调试。

7 下载调试

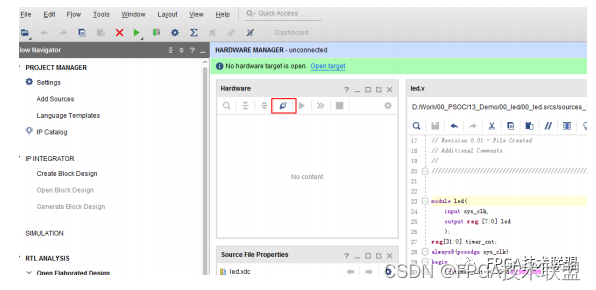

(1)连接好开发板的 Jtag 接口,给开发板上电。在“HARDWARE MANAGER”界面点击“Auto Connect”会自动扫描到设备并连接。

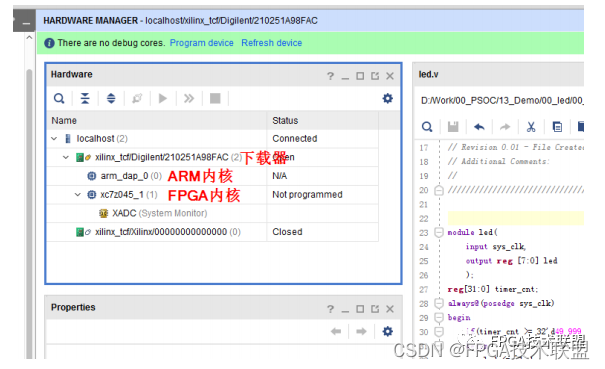

(2)可以看到 Jtag 扫描到的 ARM 和 FPGA 内核,还有一个 XADC 可以检测系统电压和温度。

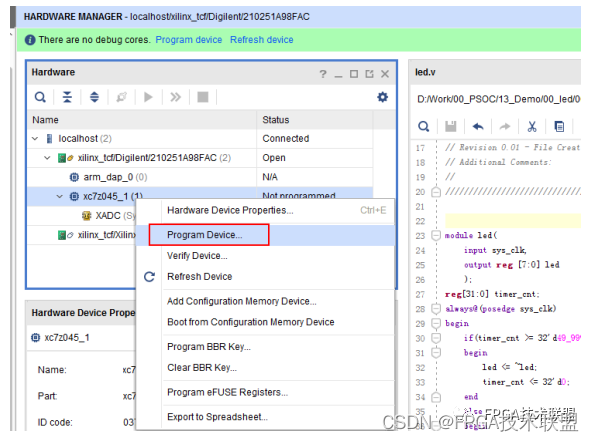

(3)选择 xc7z045_1,右键“Program Device...”

(4)在弹出的窗口选择好具体的位流路径,然后点击“Program”。

(5)等待下载成功后,我们可以看到 8 颗 LED 灯每秒变化一次,纯 PL 的 Vivado流程至此结束。

8 总结

采用国产复旦微的FMQL45完成了LED灯的点亮,也是开启了国产FPGA使用的第一步。后续会再介绍进一步的教程。

有对这款板卡感兴趣的朋友,可以参考下面的链接,有详细介绍,国产FPGA解决方案,我们是专业的!

国产化复旦微电子 FMQL45T900 FPGA开发板( 替代Xilinx ZYNQ ARM+FPGA 7045开发板)