文章目录

- Clock详解

- 特征

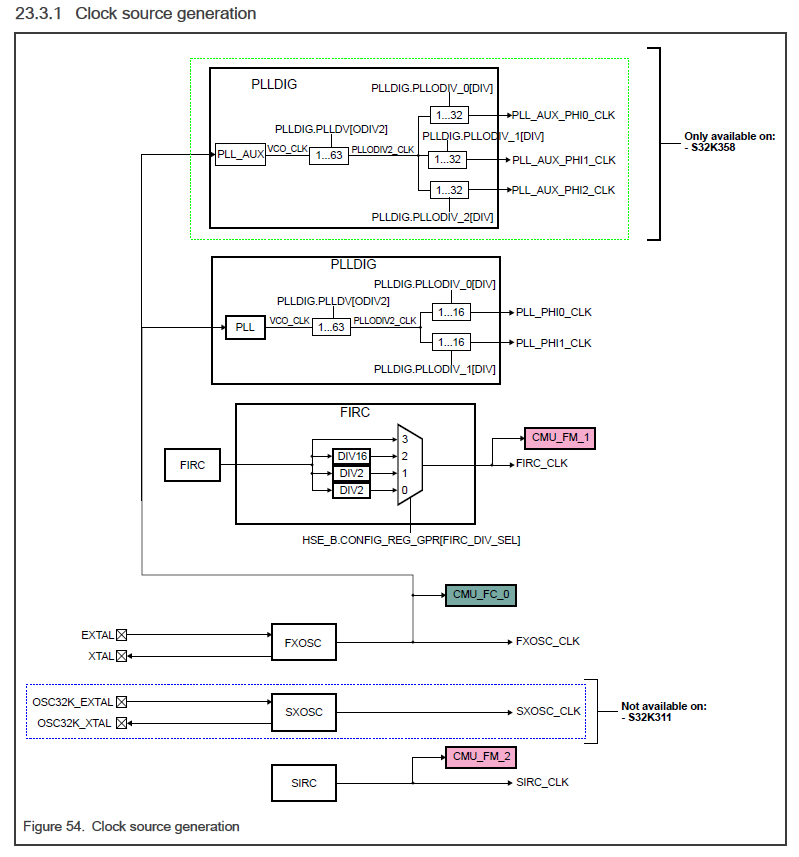

- 时钟生成

- MC_CGM mux 0时钟

- 时钟输出概述

- 其他时钟

- 整体框图

- 时钟源

- 芯片时钟源

- 芯片输入时钟

- 芯片输出时钟

- FIRC快速内部RC振荡器

- 待机模式下的FIRC_CLK行为

- SIRC慢速内部RC振荡器

- 待机模式下的SIRC行为

- FXOSC快速外部晶振

- 慢速外部晶振

- PLL

- 锁相环配置

- PLL配置序列

- 芯片时钟输出

- MC_CGM时钟生成模块

- MC_CGM时钟多路复用器类型

- MC_CGM时钟源映射

- 时钟细节

- 系统时钟频率限制

- 参考使用case

- MC_CGM register descriptions

- MC_CGM memory map

- Clock Mux 0 Select Control Register (MUX_0_CSC)

- Clock Mux 0 Select Status Register (MUX_0_CSS)

- Clock Mux 0 Divider 0-6 Control Register (MUX_0_DC_0-6)

- Clock Mux 0 Divider Trigger Control Register (MUX_0_DIV_TRIG_CTRL)

- Clock Mux 0 Divider Trigger Register (MUX_0_DIV_TRIG)

- Clock Mux 1 Select Control Register (MUX_1_CSC)

- Clock Mux 1 Select Status Register (MUX_1_CSS)

- Clock Mux 1 Divider 0 Control Register (MUX_1_DC_0)

- Fast Internal RC Oscillator (FIRC)

- FIRC register descriptions

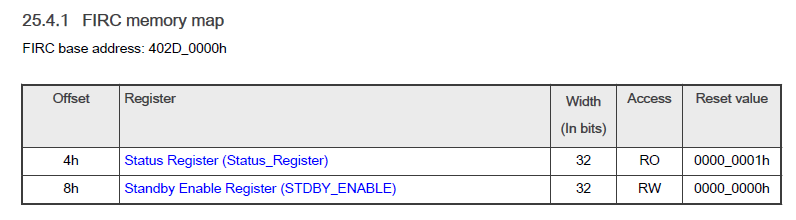

- FIRC memory map

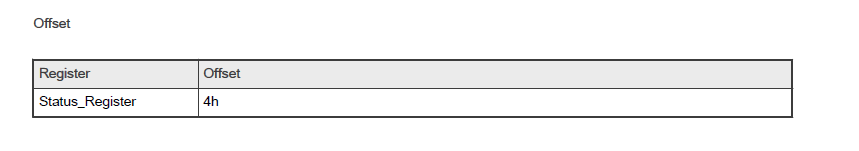

- Status Register (Status_Register)

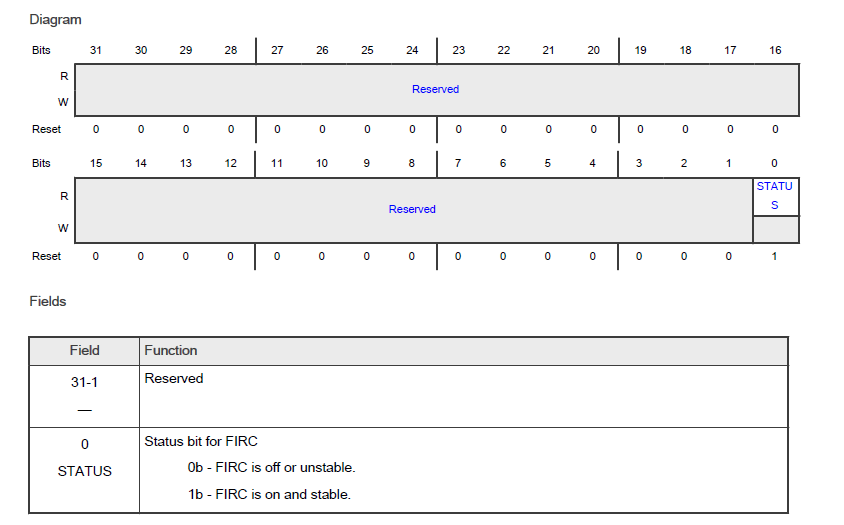

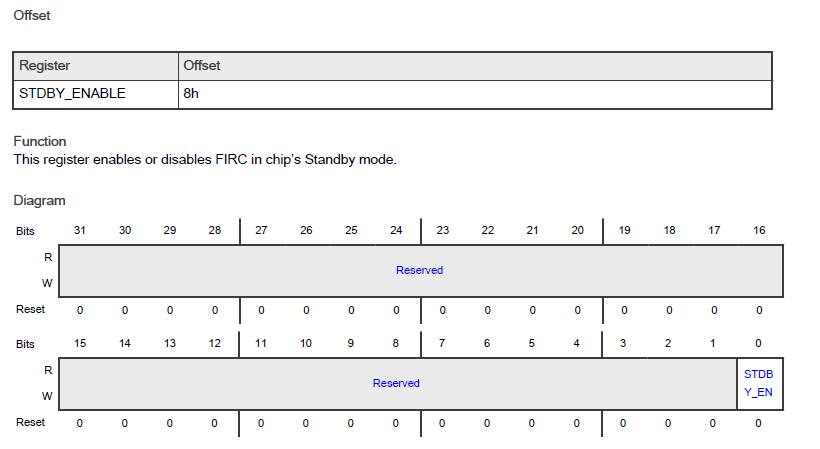

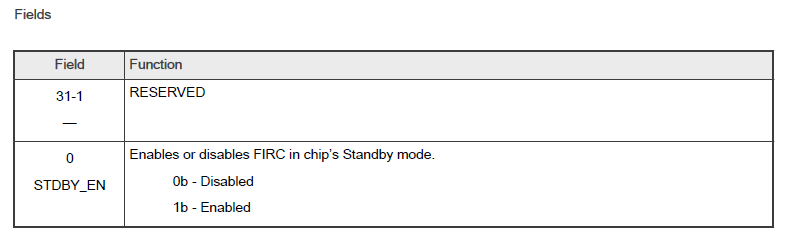

- Standby Enable Register (STDBY_ENABLE)

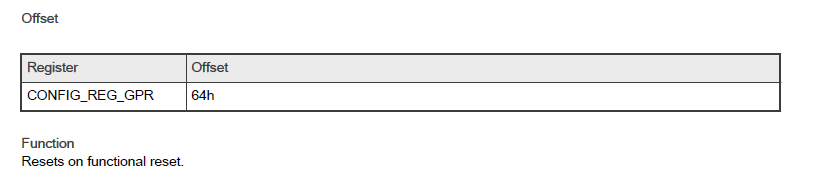

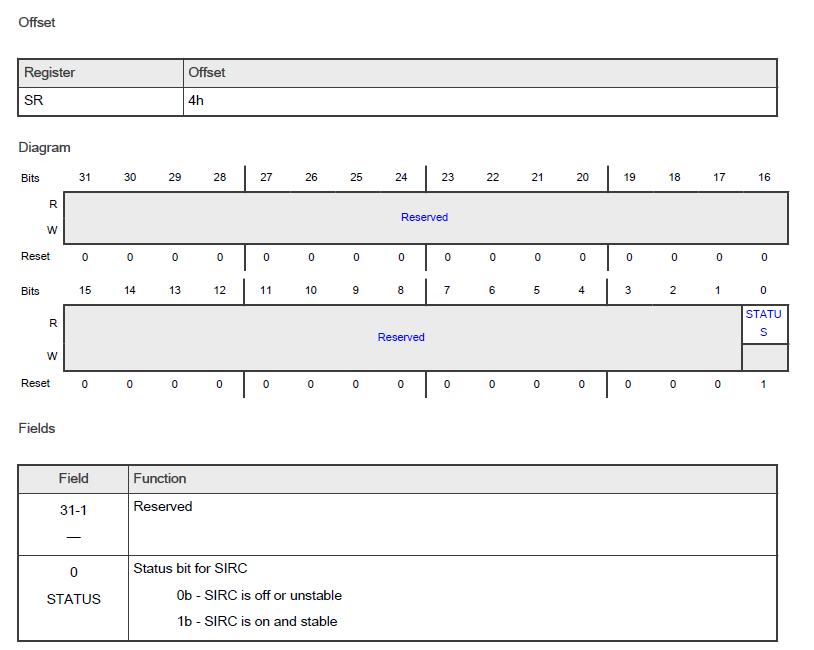

- Configuration REG_GPR (CONFIG_REG_GPR)

- Slow Internal RC Oscillator (SIRC)

- SIRC register descriptions

- SIRC memory map

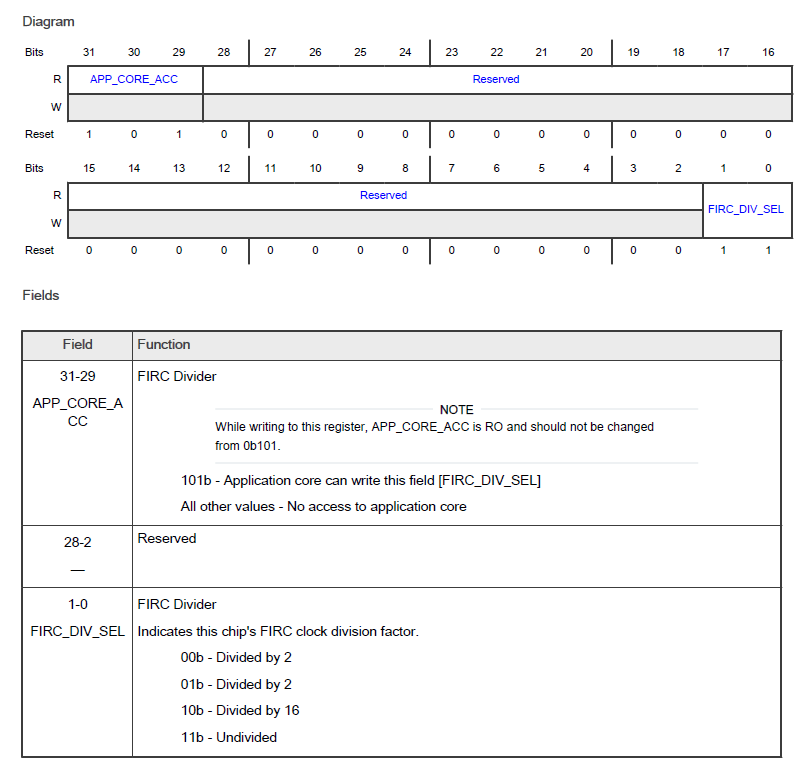

- Status Register (SR)

- Miscellaneous input (MISCELLANEOUS_IN)

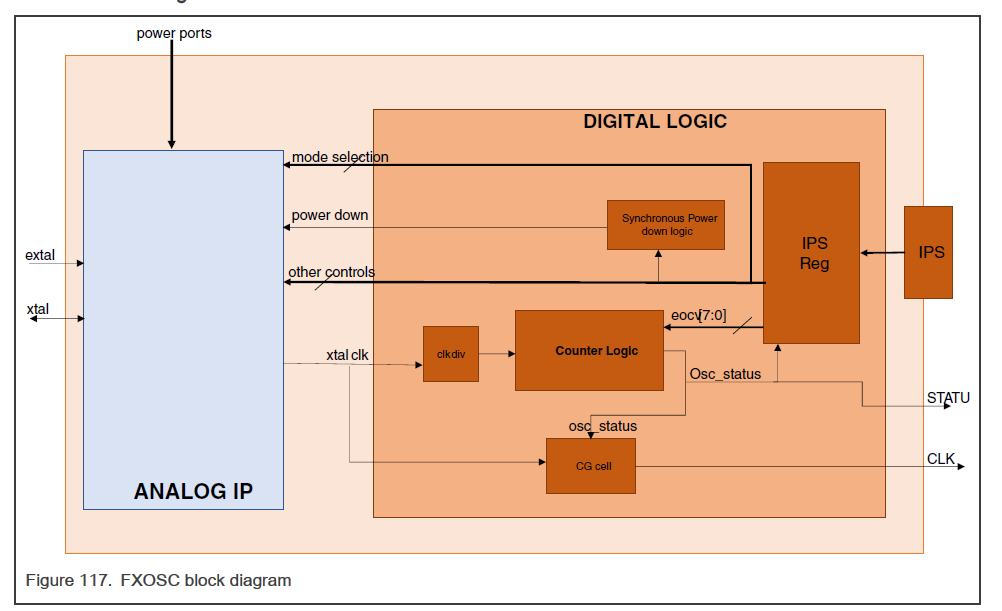

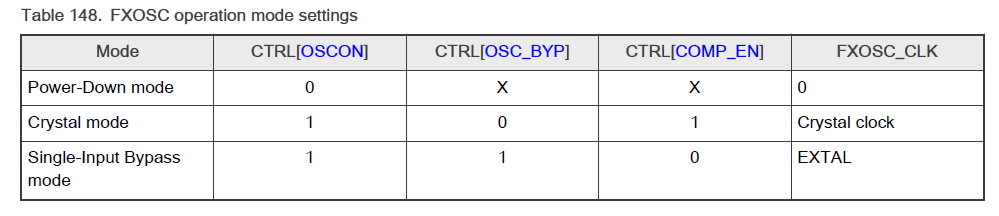

- Fast Crystal Oscillator Digital Controller (FXOSC)

- Functional description

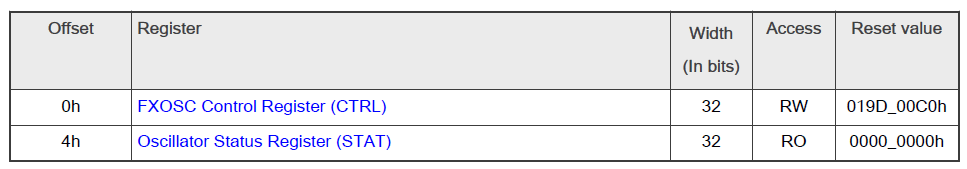

- FXOSC memory map

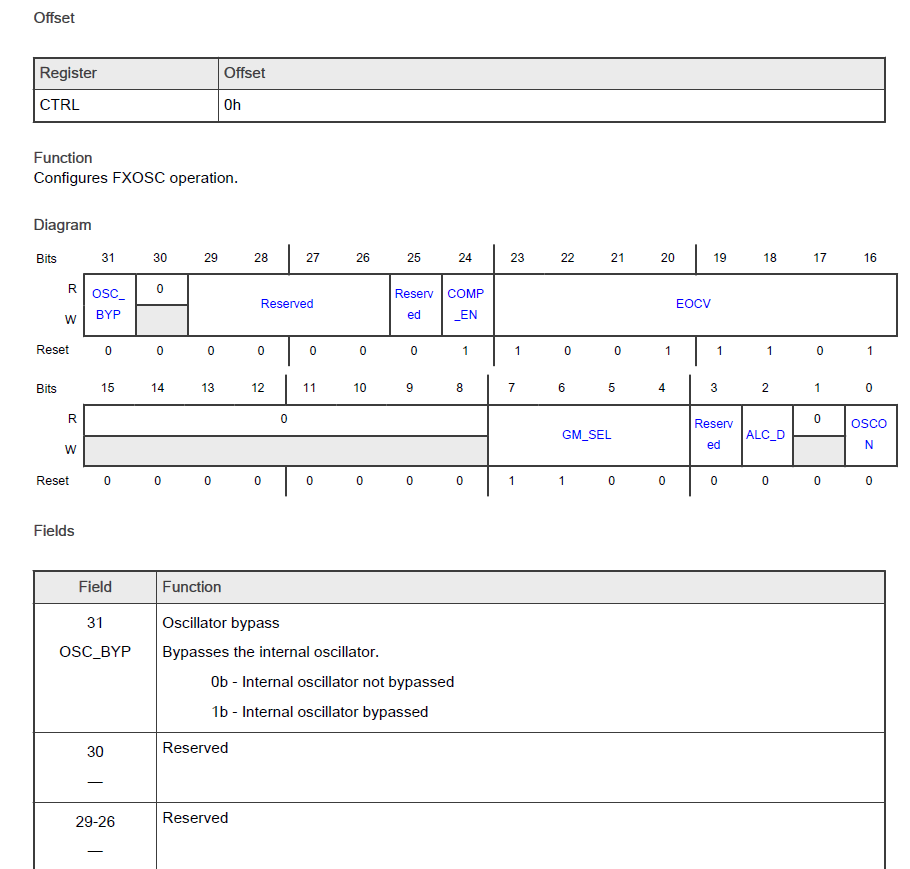

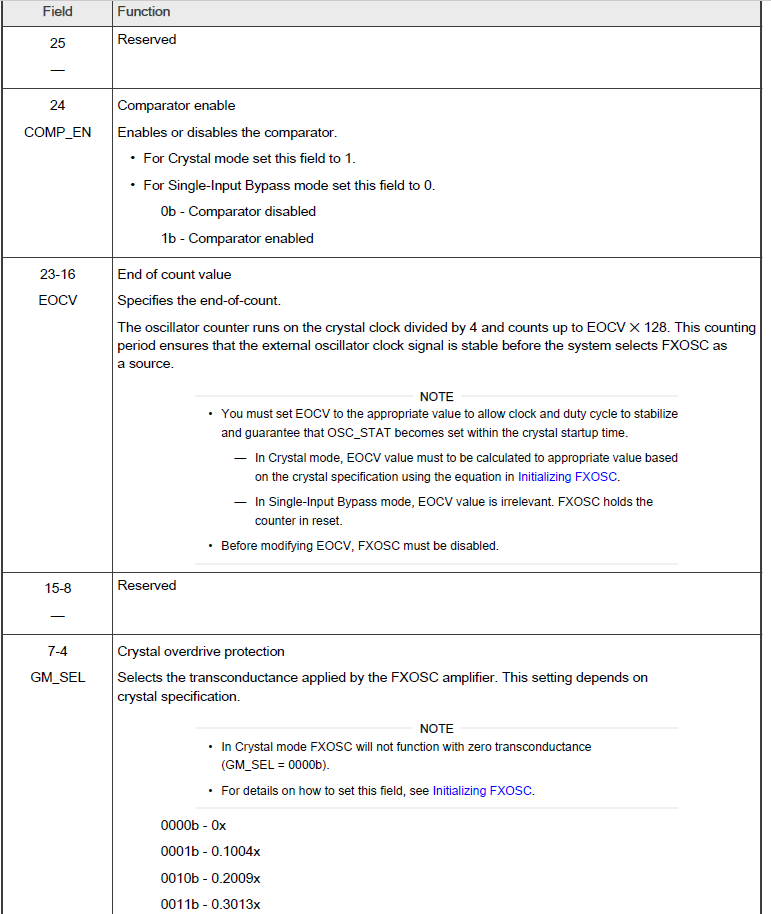

- FXOSC Control Register (CTRL)

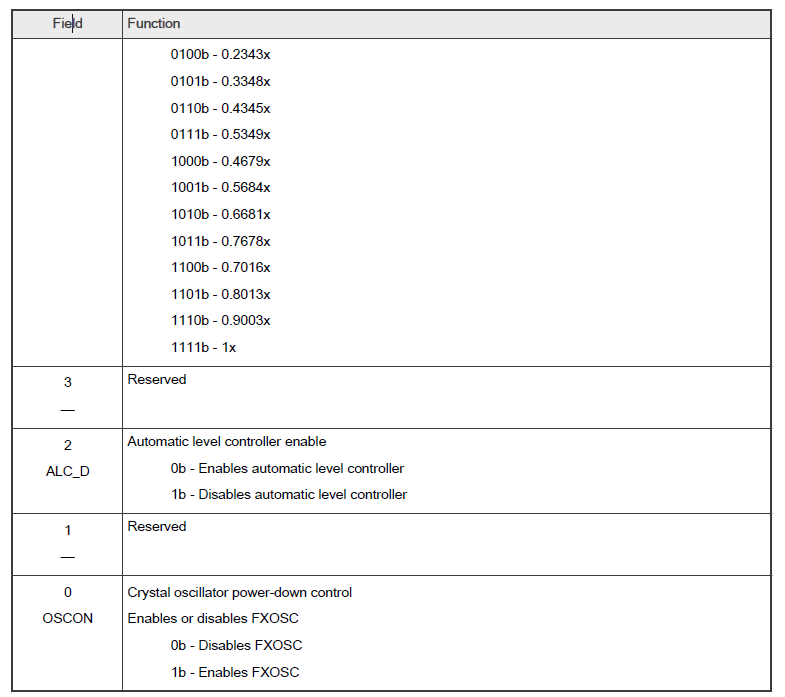

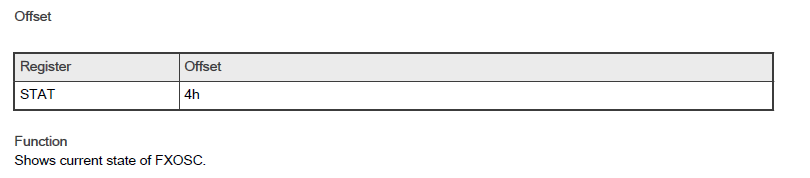

- Oscillator Status Register (STAT)

- Slow Crystal Oscillator Digital Controller (SXOSC)

- 操作模式

- Crystal mode

- Bypass mode

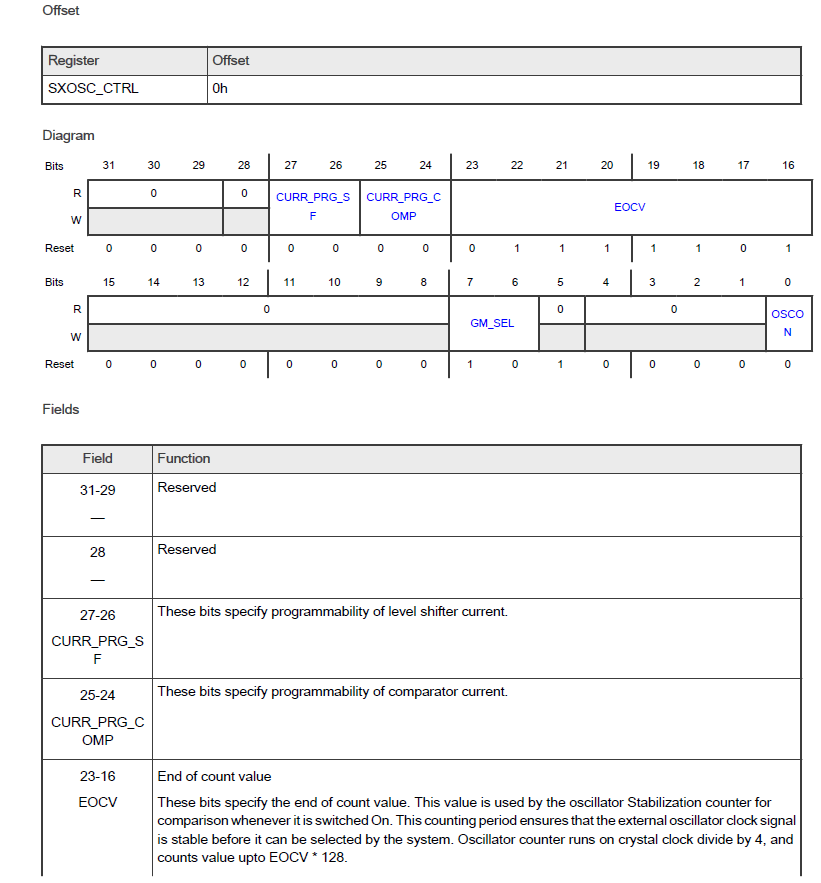

- SXOSC register descriptions

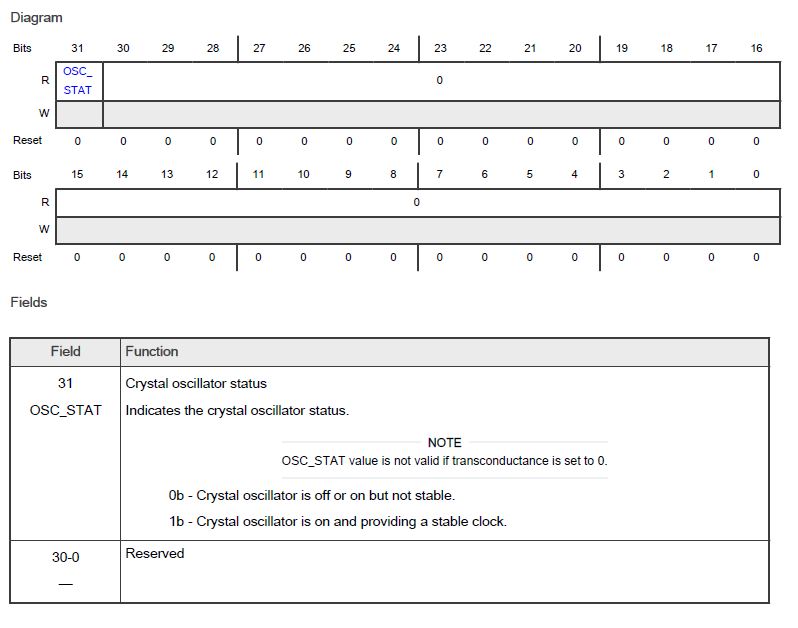

- SXOSC memory map

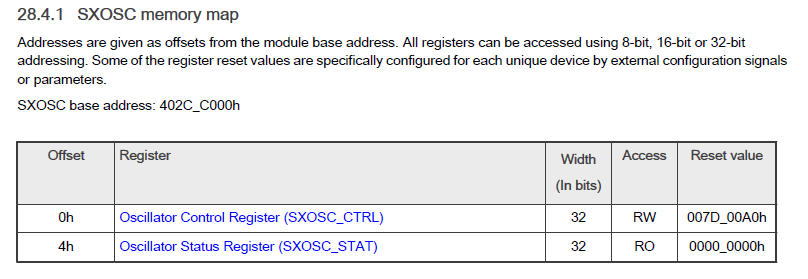

- Oscillator Control Register (SXOSC_CTRL)

- Oscillator Status Register (SXOSC_STAT)

- PLL Digital Interface (PLLDIG)

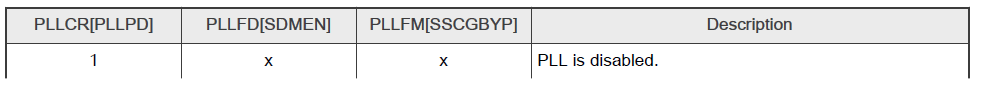

- 工作模式

- 输入时钟频率

- Clock configuration时钟配置

- 频率调制

- 调频编程

- PLLDIG register descriptions

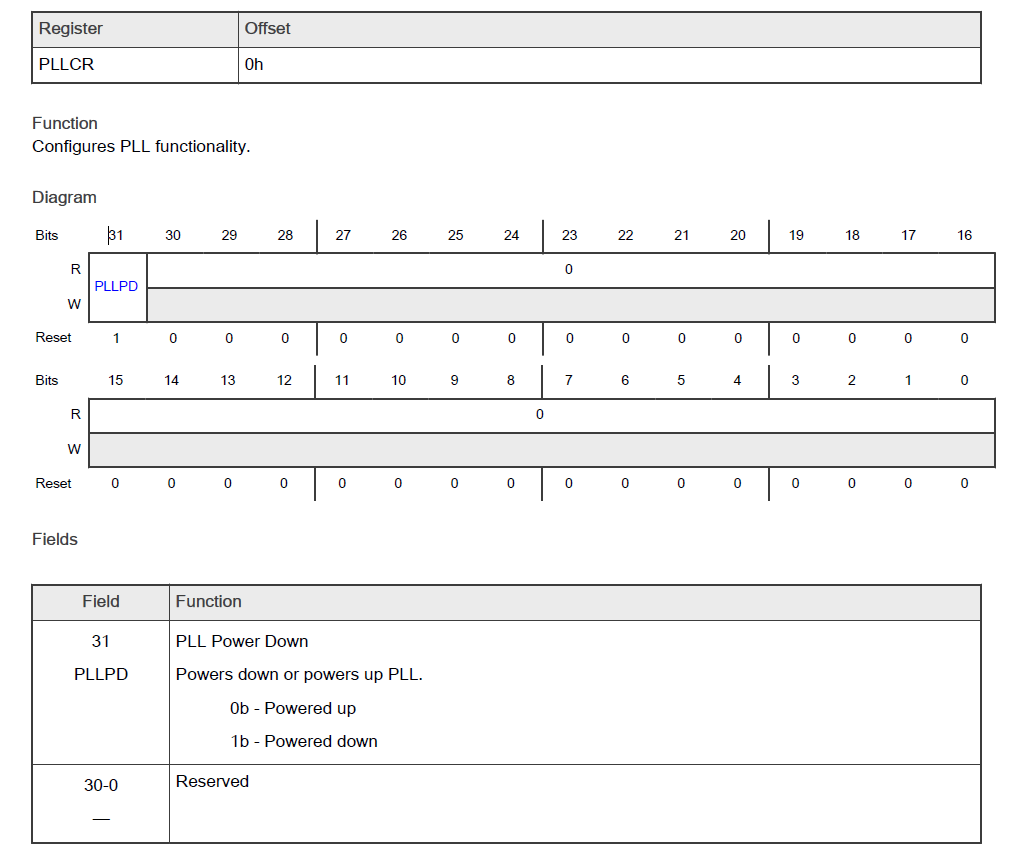

- PLL Control (PLLCR)

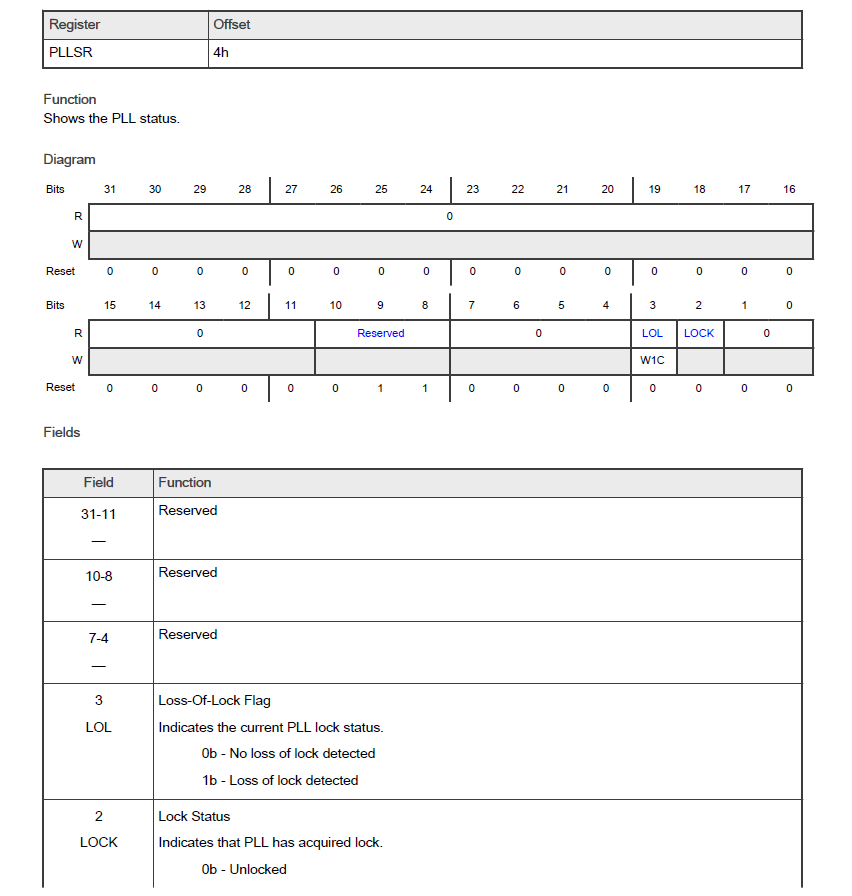

- PLL Status (PLLSR)

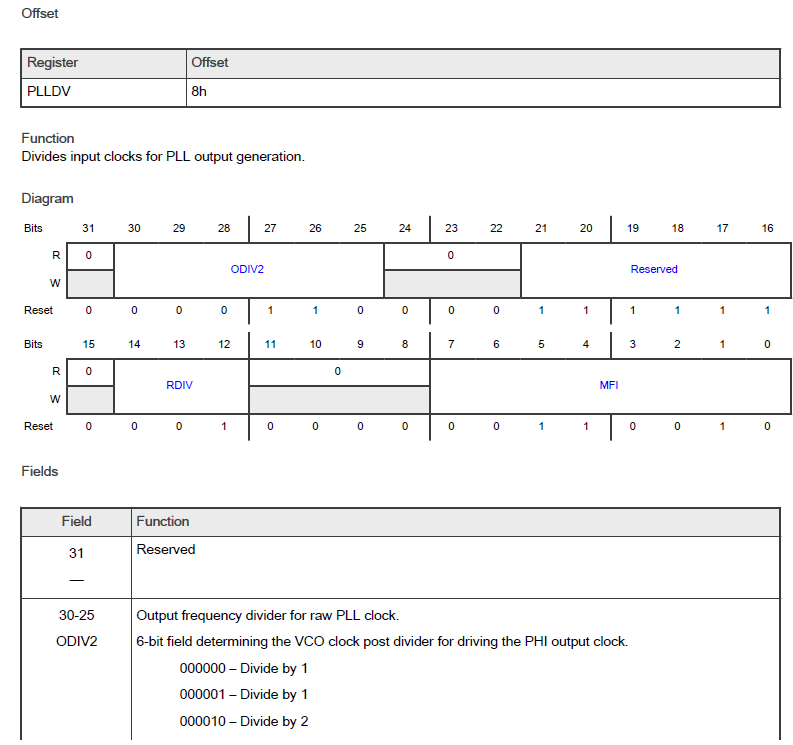

- PLL Divider (PLLDV)

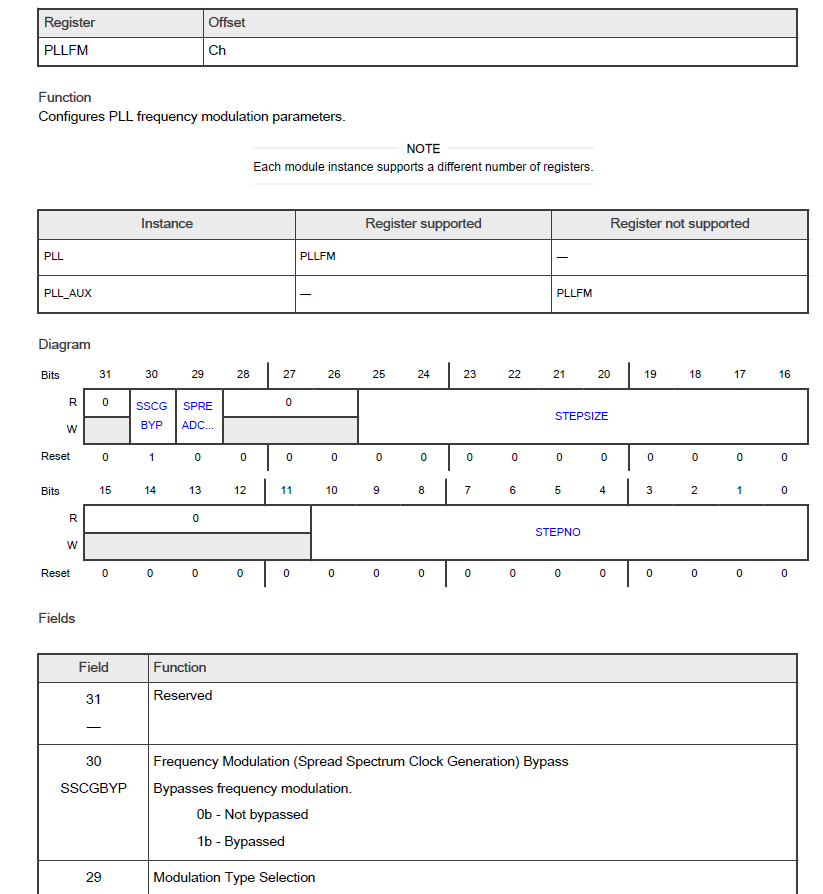

- PLL Frequency Modulation (PLLFM)

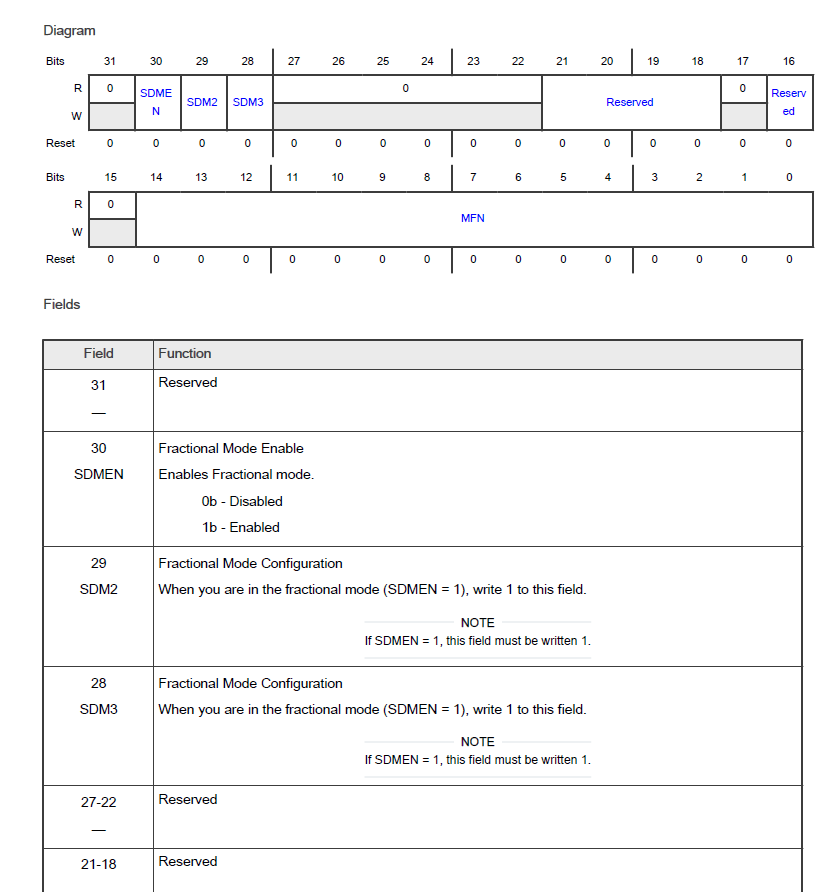

- PLL Fractional Divider (PLLFD)

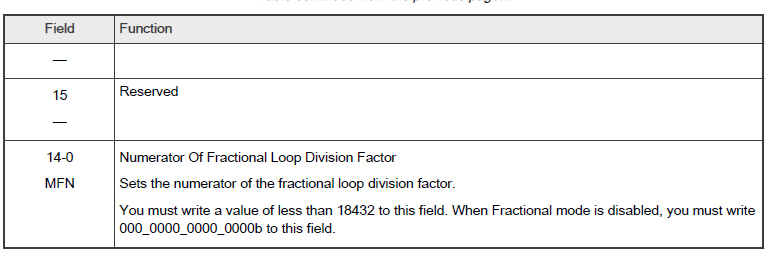

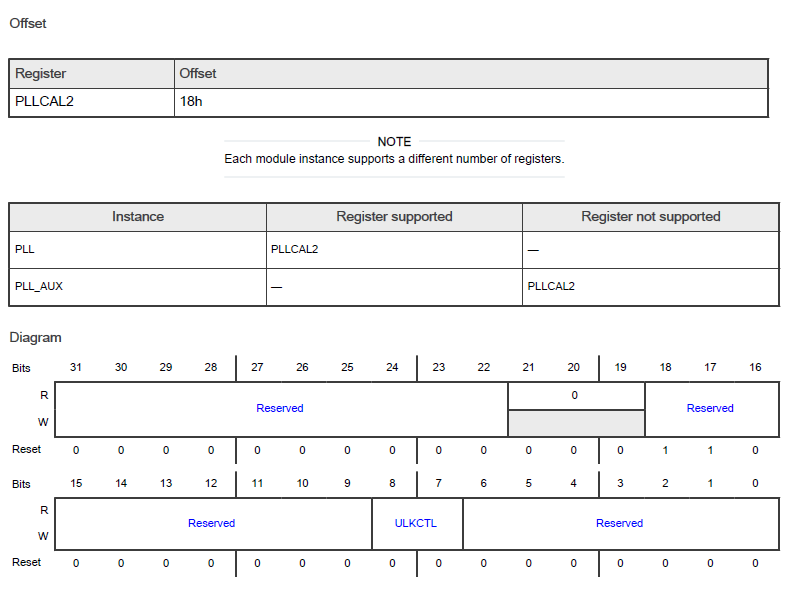

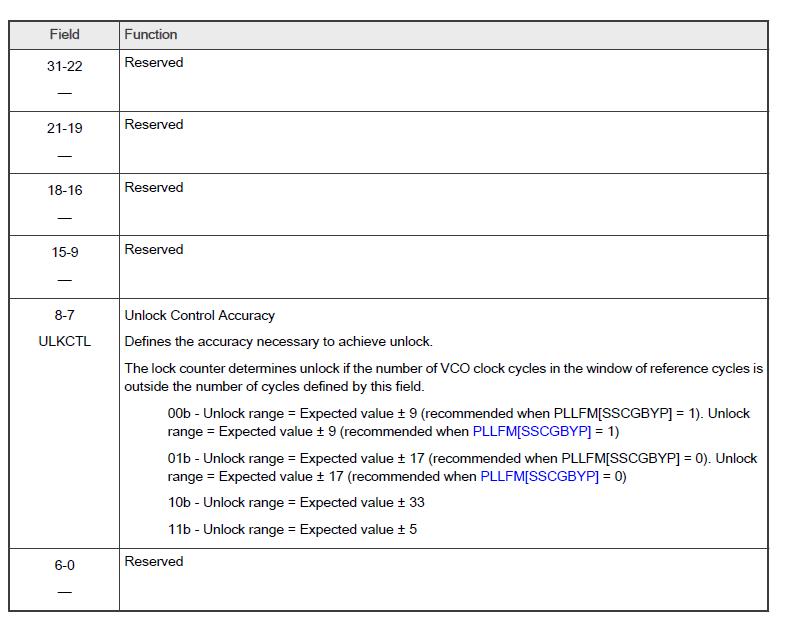

- PLL Calibration Register 2 (PLLCAL2)

- PLL Output Divider (PLLODIV_0 - PLLODIV_1)

- Real Time Clock (RTC)

- 特点

- 功能描述

- RTC

- API功能描述

- 工作模式

- 功能模式

- Debug mode

- RTC register descriptions

- RTC memory map

- RTC Supervisor control register (RTCSUPV)

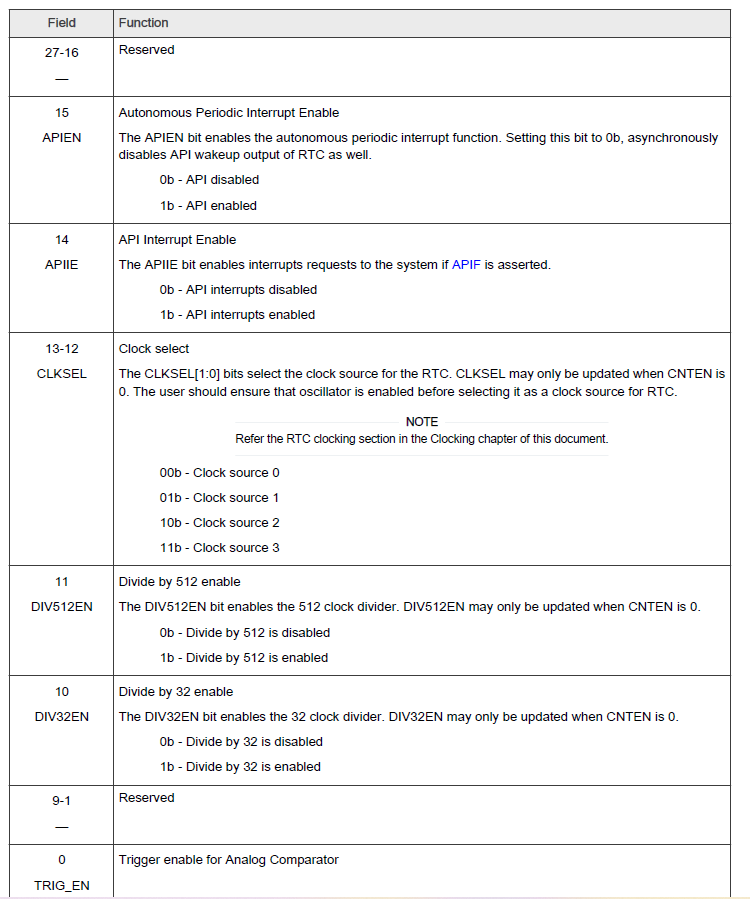

- RTC Control register (RTCC)

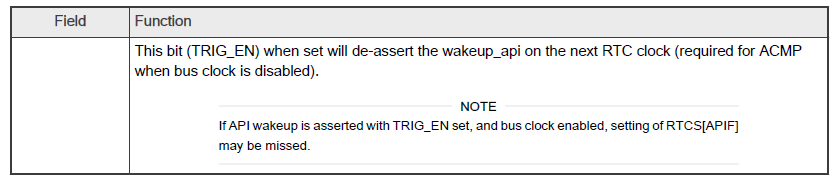

- RTC Status register (RTCS)

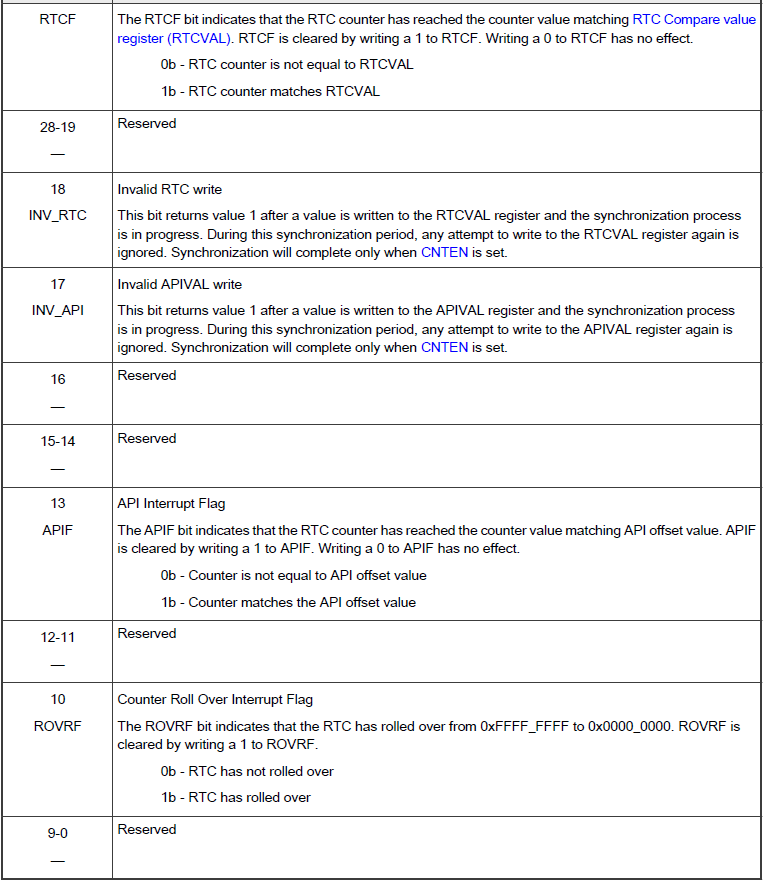

- RTC Counter register (RTCCNT)

- API Compare value register (APIVAL)

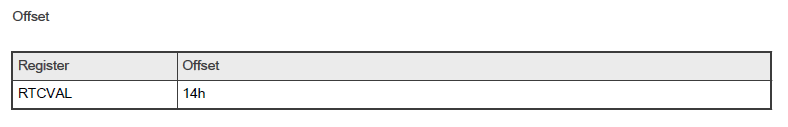

- RTC Compare value register (RTCVAL)

Clock详解

特征

多个时钟源可选用于时钟生成:

- 快速内部RC振荡器(FIRC)

- 慢速内部RC振荡器(SIRC)

- 快速外部晶体振荡器(FXOSC)

- 慢速外部晶体振荡器(SXOSC)

注意:SXOSC没有100-MAX QFP和48针LQFP封装。具体请参见“简介”章节“S32K3xx芯片的特性比较”表。 - 锁相环(PLL)

调频锁相环输出时钟,减少电磁辐射

用于计时和通信功能的精确时钟

无故障时钟开关时钟生成模块(MC_CGM)时钟选择器

系统时钟渐进时钟频率开关(PCFS)

时钟监控单元(CMU_FC, CMU_FM)检查时钟完整性

使用模式输入模块(MC_ME)分区进程配置寄存器的核心和外围时钟门控

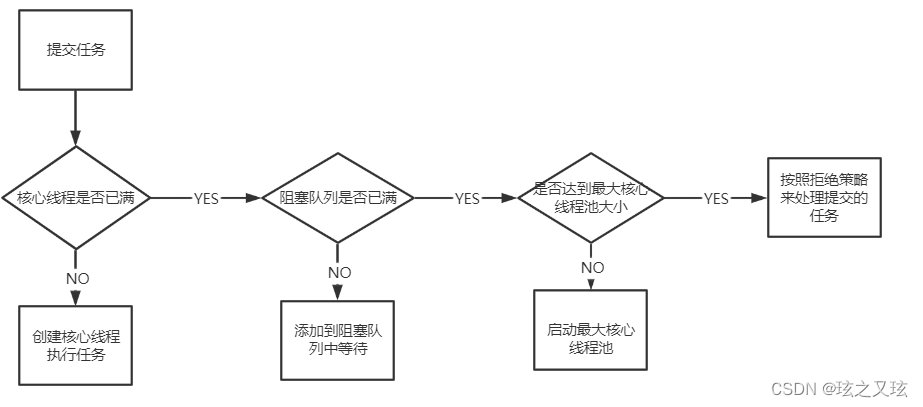

时钟生成

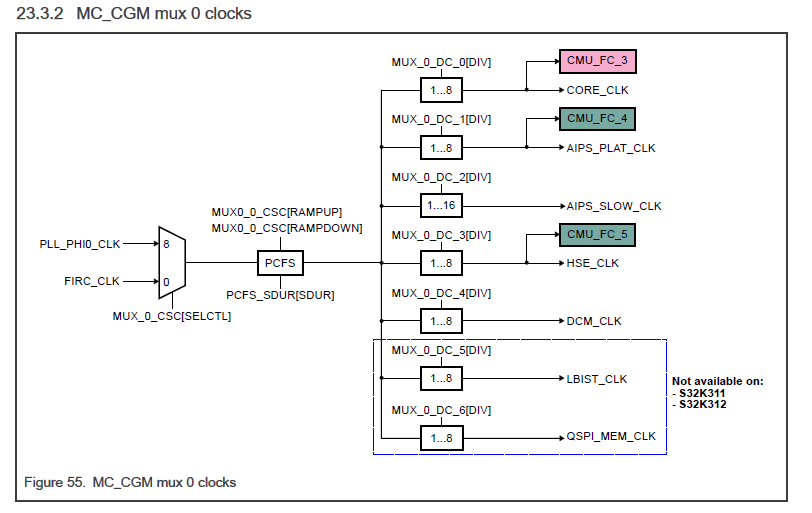

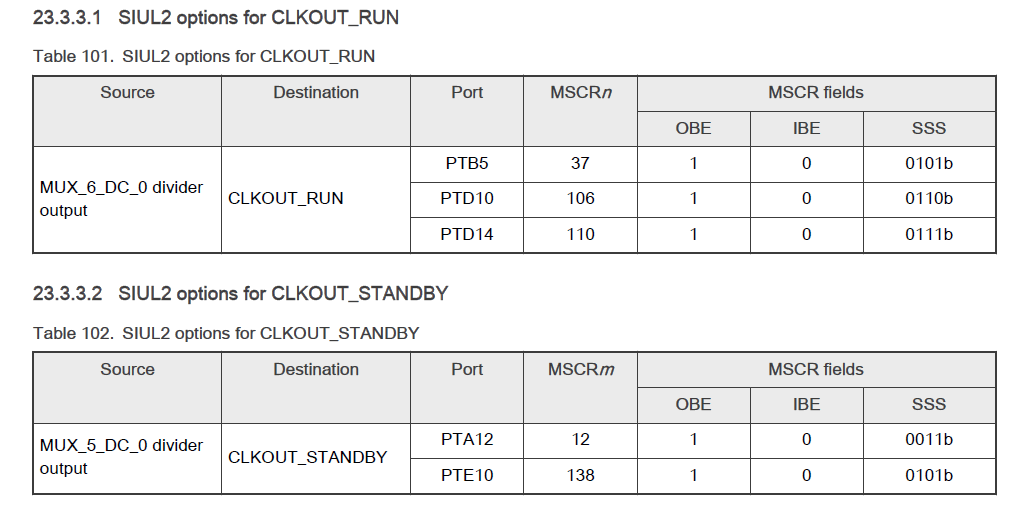

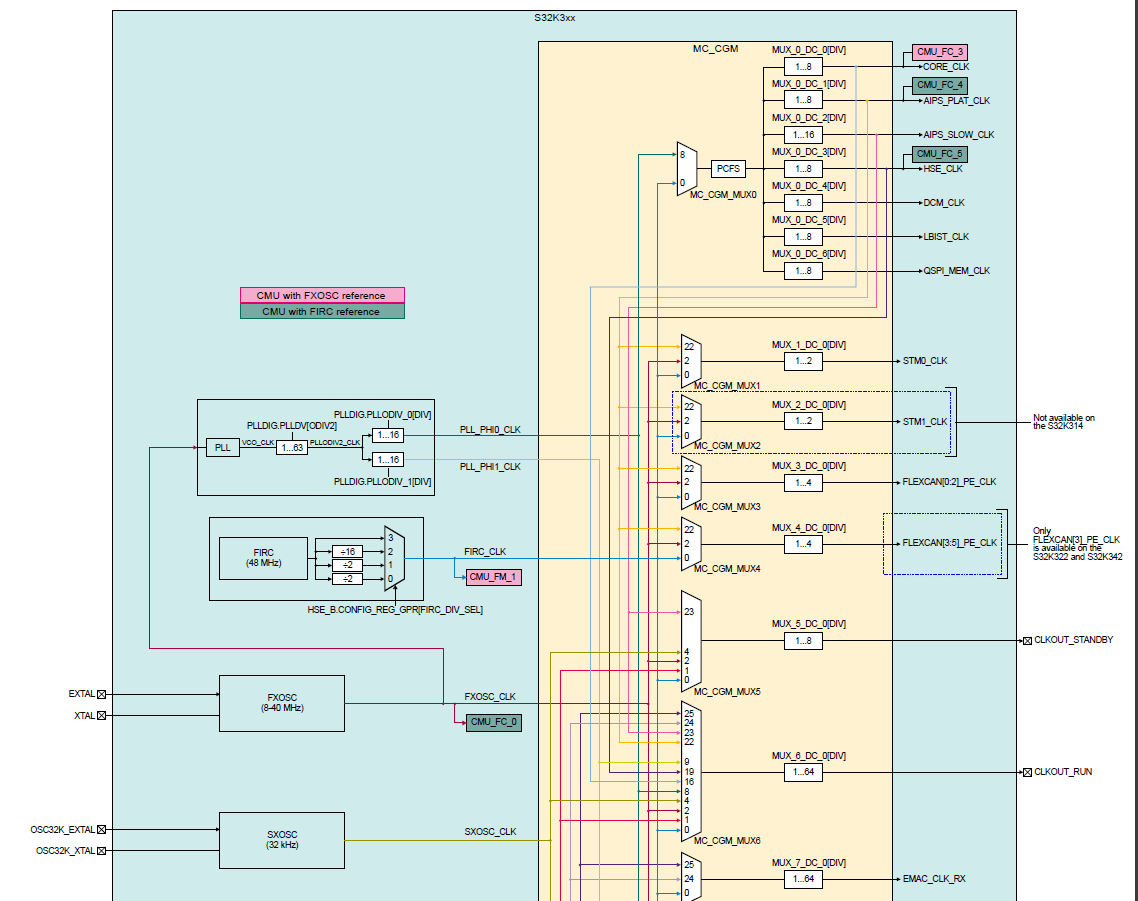

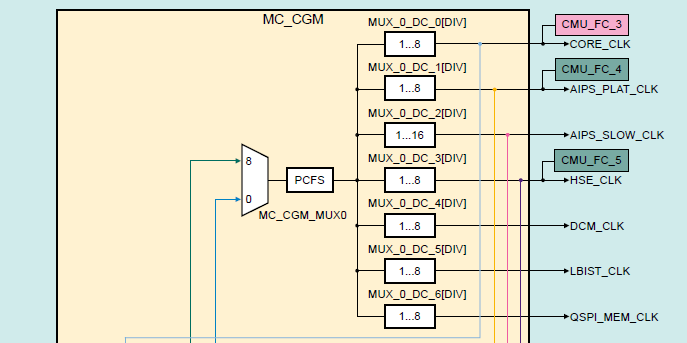

MC_CGM mux 0时钟

对于HSE_B, TCK和HSE_CLK时钟之间的时钟频率关系必须是1:1.5的最小比例。例如,如果HSE_CLK等于80 MHz,那么TCK必须小于或等于53 MHz (80 MHz ÷ 1.5)。(TCK来自于JTAG_TCK/SWD_CLK)

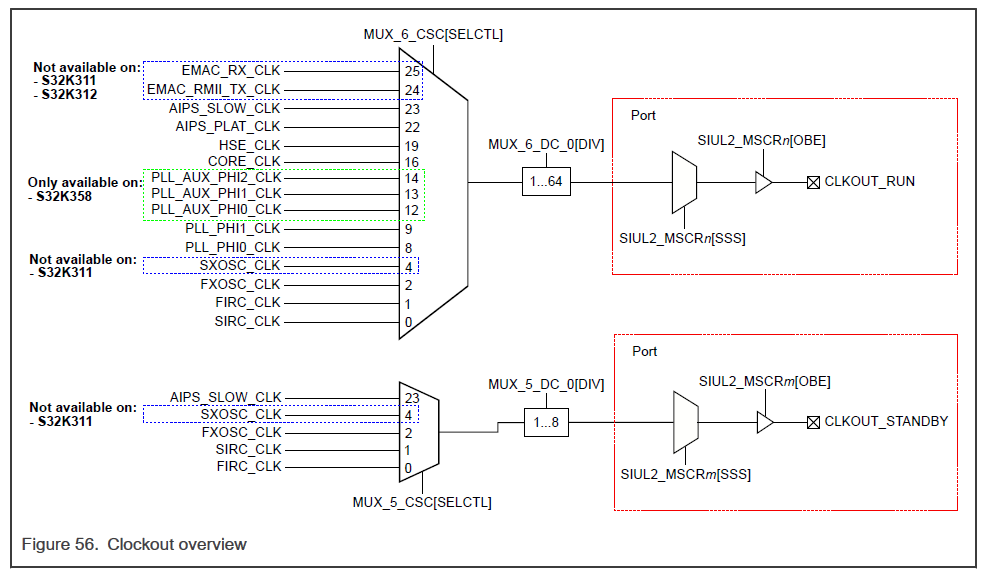

时钟输出概述

在待机模式下CLKOUT_RUN不可用

其他时钟

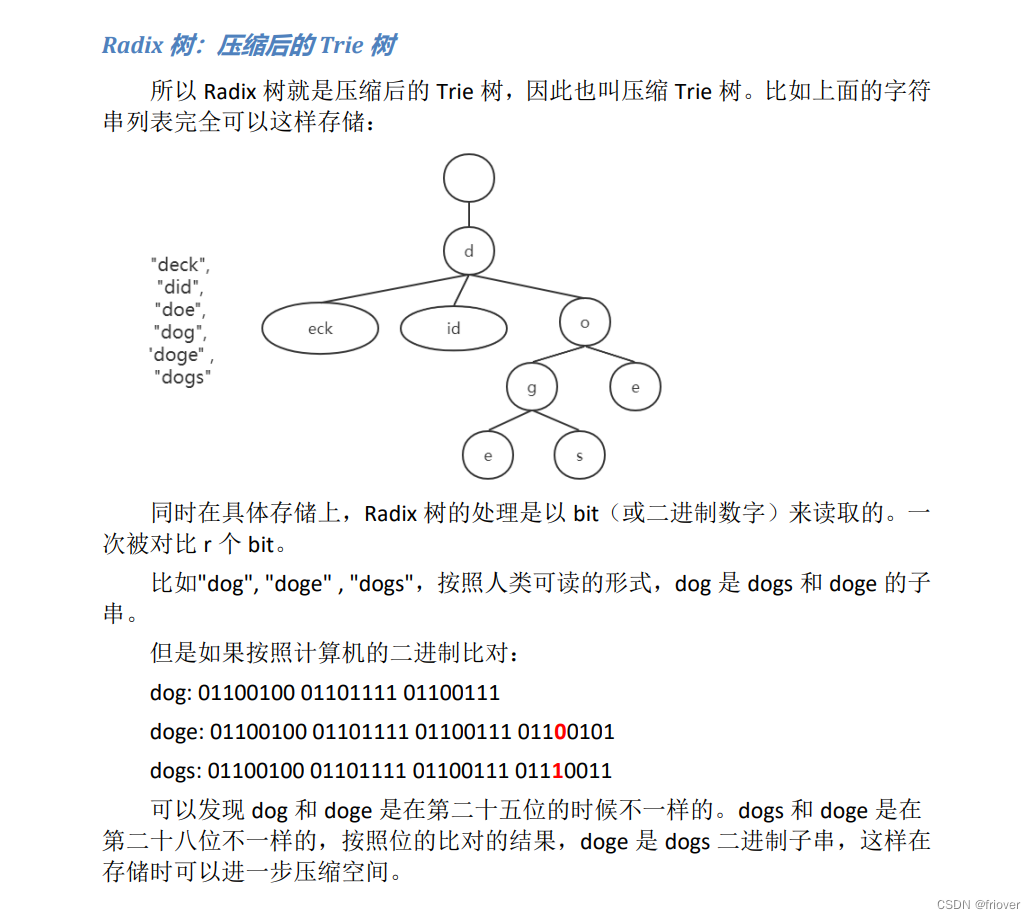

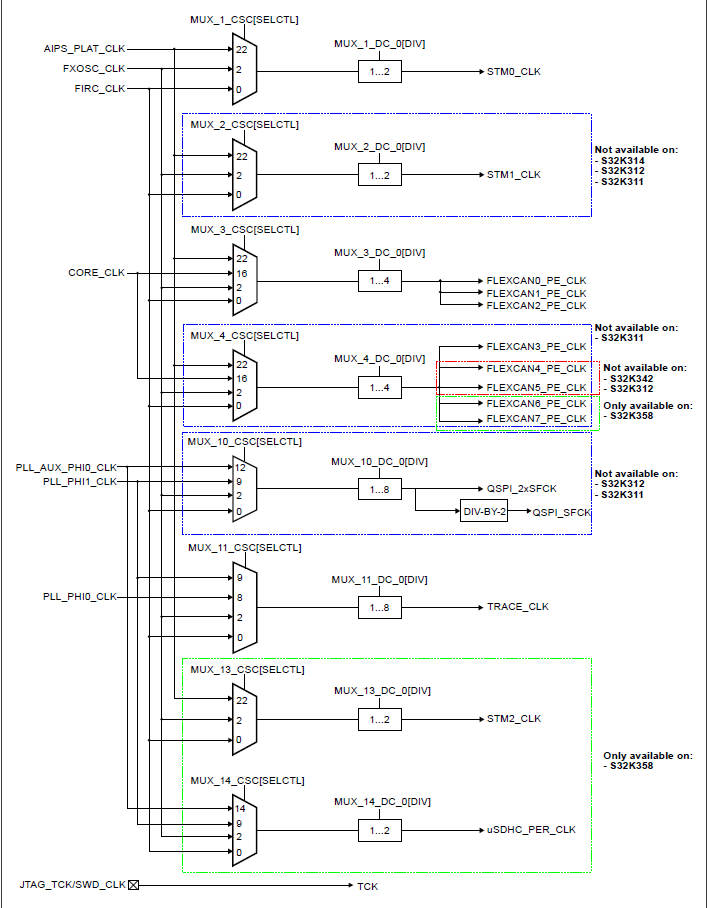

整体框图

S32K324-P723/4649

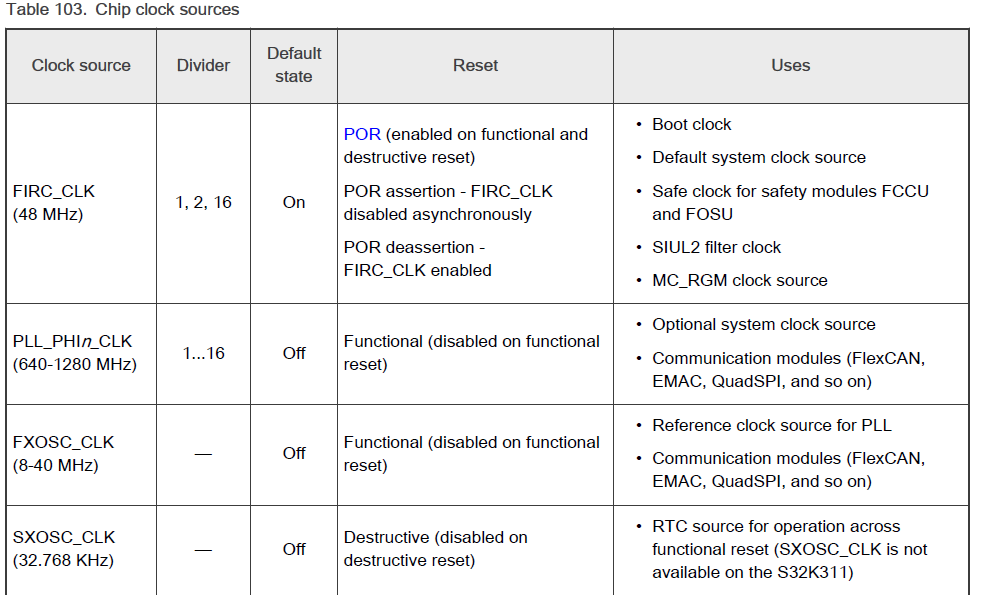

时钟源

芯片包含以下时钟源模块:

•FIRC-快速内部RC振荡器

- “FIRC_CLK”为系统默认时钟源。

•SIRC- 慢速内部RC振荡器

•锁相环

•FXOSC-快速外部晶振输出时钟

•SXOSC (S32K311无)慢速外部晶振输出时钟

以下列表显示了时钟系统的一些功能:

•所有时钟源都支持开启或关闭的软件配置。

•除SXOSC_CLK外,所有时钟源在功能复位时初始化为默认状态。

•SXOSC_CLK支持跨功能复位的RTC应用程序,并在破坏性复位时复位。

只有SIRC_CLK和FIRC_CLK在复位后启用,并且在任何功能复位时启用。其他时钟源在复位时关闭。

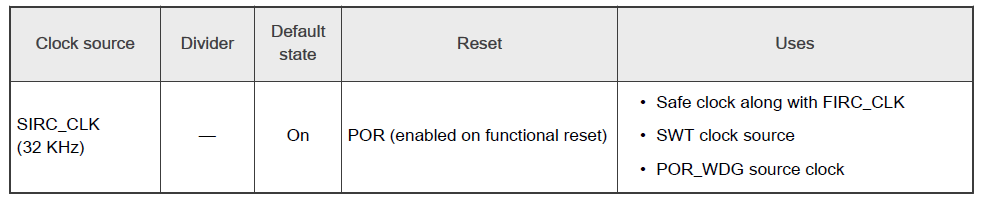

芯片时钟源

芯片输入时钟

| Pin | 描述 |

|---|---|

| XTAL | FXOSC相关 |

| EXTAL | FXOSC相关 |

| OSC32K_XTAL | SXOSC相关 |

| OSC32K_EXTAL | SXOSC相关 |

| EMAC_MII_RMII_TX_CLK | EMAC TX时钟/EMAC RMII时钟(S32K311或S32K312不支持) |

| EMAC_MII_RX_CLK | EMAC RX时钟(S32K311或S32K312不支持) |

| JTAG_TCLK/SWD_CLK | JTAG/SWD时钟 |

| SAIn_MCLK | 从模式下SAI_n时钟(S32K311或S32K312不支持) |

| SAIn_BCLK | 从模式下SAI_n位时钟(S32K311和S32K312不支持) |

| LPSPIn_SCK | 从模式下LPSPIn串行时钟 |

| LPI2Cn_SCL | LPI2C_n时钟 |

| LPI2C_n时钟 | LPI2C_n第二时钟 |

芯片输出时钟

| Pin | 描述 |

|---|---|

| CLKOUT_RUN | 运行模式下可用,待机模式下不可用 |

| CLKOUT_STANDBY | 在运行和待机模式下均可用 |

| LPSPIn_SCK | 主机模式下SPI时钟输出 |

| LPI2Cn_SCL | I2C时钟输出 |

| LPI2Cn_SCLS | I2C第二时钟输出 |

| LPI2Cn_SCL | I2C时钟输出 |

| EMAC_MII_RMII_MDC | 用于将控制数据传输到PHY的EMAC时钟(在S32K311或S32K312上不可用) |

| EMAC_MII_RMII_TX_CLK | EMAC传输时钟(S32K311或S32K312上没有) |

| TRACE_ETM_CLKOUT | ETM跟踪时钟(在S32K311、S32K312或S32K342/S32K322/S32K341上不可用) |

| SAIn_BCLK | 主模式SAI_n位时钟(在S32K311或S32K312上不可用) |

| QuadSPI_SCKFA | 用于串行闪存设备A的QuadSPI串行时钟(fast)(在S32K311或S32K312上没有) |

FIRC快速内部RC振荡器

该芯片具有FIRC,具有以下特点:

•在上电和任何复位事件后,作为系统时钟源。

-重要的是检测FIRC_CLK故障和恢复

•作为芯片的安全时钟,用于与安全相关的应用。

•在运行模式下始终启用,在待机模式下可选启用。

•用作以下时钟源:

- MC_RGM

- FCCU和FOSU

- SIUL2过滤器

待机模式下的FIRC_CLK行为

FIRC_CLK可以通过配置FIRC.STDBY_ENABLE[STDBY_EN]在Standby模式下可选启用。

当PMC确认进入待机模式时,FIRC_CLK从On状态切换到FIRC选择的Standby模式配置,通过FIRC.STDBY_ENABLE[STDBY_EN]配置。从Standby模式唤醒时,FIRC_CLK配置从Standby模式配置状态切换到On状态。

3 MHz的FIRC仅用于低功耗运行模式。如果芯片需要进入待机模式,那么在待机模式下,FIRC必须配置为48 MHz, FIRC_DIV_SEL为’0b11’。退出待机模式后,如果需要,FIRC可以更改为3 MHz。

SIRC慢速内部RC振荡器

该芯片有一个SIRC,具有以下特点:

•在运行模式下始终启用,在待机模式下可选启用。在降低待机模式下的芯片功耗时,始终启用SIRC可以确保各种swt的时钟始终可用,从而提高系统的健壮性。

•用作以下时钟源:

- SWT

- POR_WDG

待机模式下的SIRC行为

通过配置SIRC.MISCELLANEOUS_IN[STANDBY_ENABLE],可以选择在Standby模式下启用SIRC。

当PMC确定进入待机模式时,SIRC从On状态切换到SIRC选择的待机模式,通过SIRC.MISCELLANEOUS_IN[STANDBY_ENABLE]配置。从Standby模式唤醒时,SIRC配置从Standby配置状态切换回On状态。

FXOSC快速外部晶振

该芯片支持8-40 MHz的快速晶体振荡器,具有以下特点:

•作为PLL的参考。

•如果使用外部振荡器,支持晶体输入模式和旁路模式。

•作为通信模块的时钟源:

—FlexCAN

—QuadSPI

—EMAC (EMAC_CLK_TS)

慢速外部晶振

该芯片支持慢速晶体振荡器(SXOSC), SXOSC具有以下特性(S32K311上没有):

•支持晶体输入模式。

•作为RTC时钟源。SXOSC不受功能复位的影响,支持跨功能复位的RTC操作。SXOSC仅在破坏性复位时复位。

PLL

通过PLL对晶振超频,输出稳定时钟

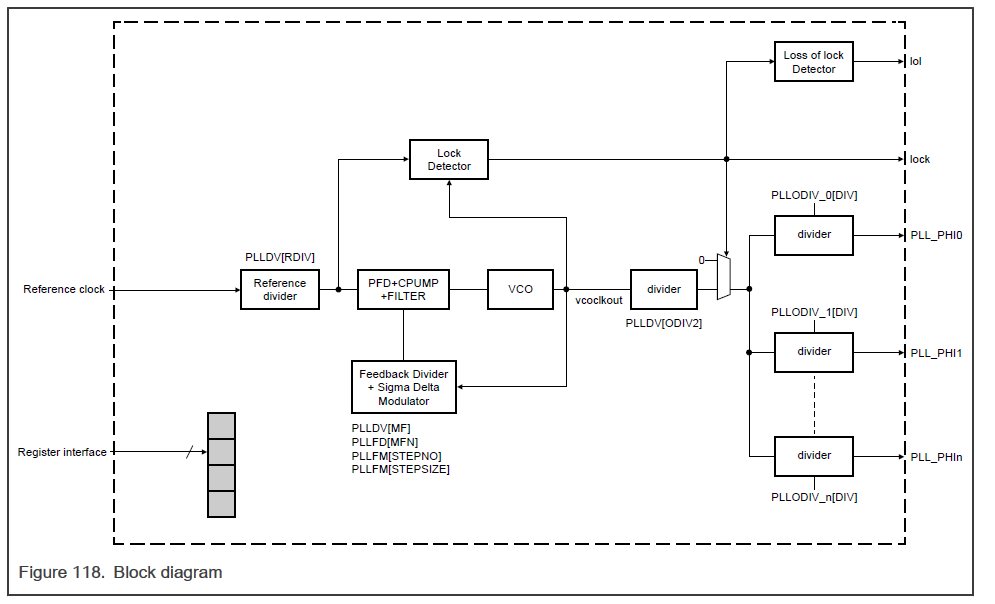

锁相环配置

锁相环输出预分频频率取决于锁相环增益PLLDIG.PLLDV[RDIV]和PLLDIG.PLLDV[MFI]配置。通过配置PLLDIG.PLLODIV_0[DIV]可以进一步划分锁相环压控振荡器时钟PLL_PHI0_CLK, PLLDIG.PLLODIV_1[DIV]用于PLL_PHI1_CLK(有关配置详细信息,请参阅“PLL数字接口(PLLDIG)”章节)。

PLL配置序列

在启用PLL之前,必须启用FXOSC_CLK并等待它稳定。FXOSC.STAT[OSC_STAT]必须被监控以确定FXOSC_CLK的状态。

要禁用锁相环,软件必须先禁用锁相环,然后才禁用FXOSC(如果需要)。

芯片时钟输出

该芯片支持两个CLKOUT_x引脚,用于查看一些内部时钟,如下所示:

•CLKOUT_STANDBY

-用于显示运行和待机模式下可用的时钟。

•CLKOUT_RUN

-仅用于显示运行模式时钟。

注意:当芯片进入待机模式时,CLKOUT_STANDBY寄存器被锁存,并按待机模式顺序重置。因此,需要在Standby模式退出时重新配置CLKOUT_STANDBY信号

CLKOUT_STANDBY可用于两个pad GPIO[12]和GPIO[138],但CLKOUT跨功能复位和standby仅支持GPIO[12]和OBE(输出缓冲区使能)由DCM GPR位控制。具体请参见DCMRWP1[3] bit。

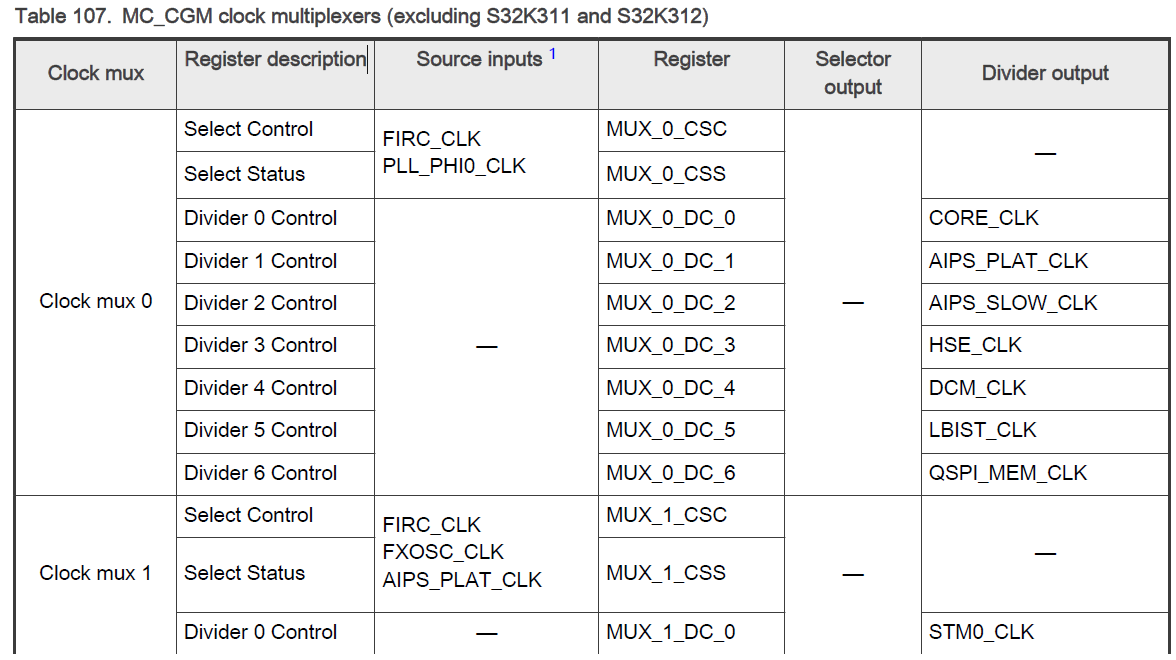

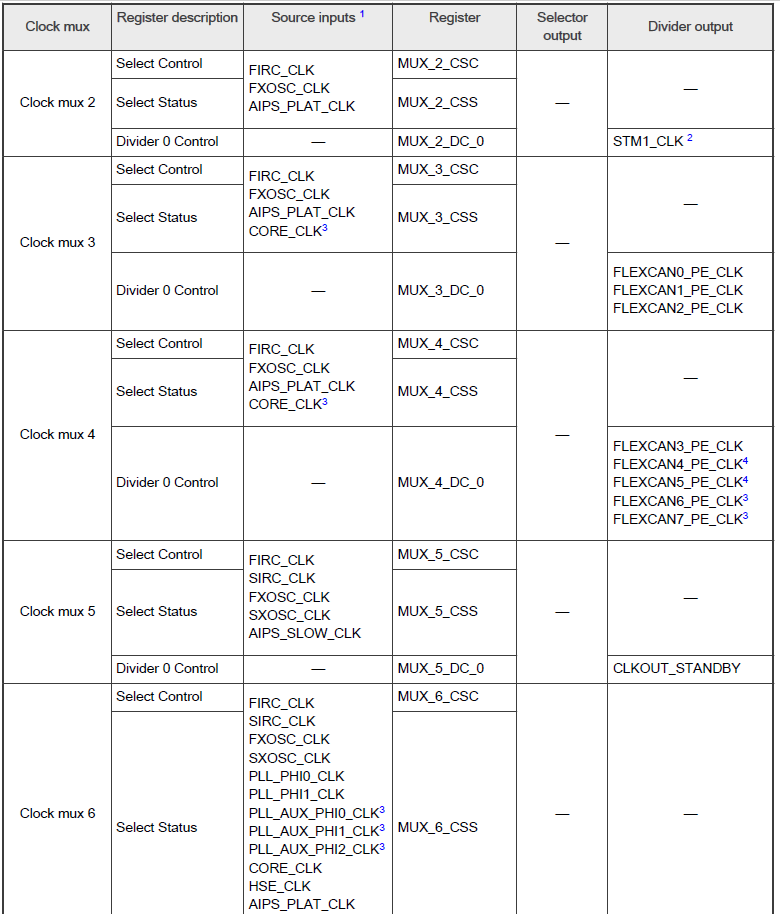

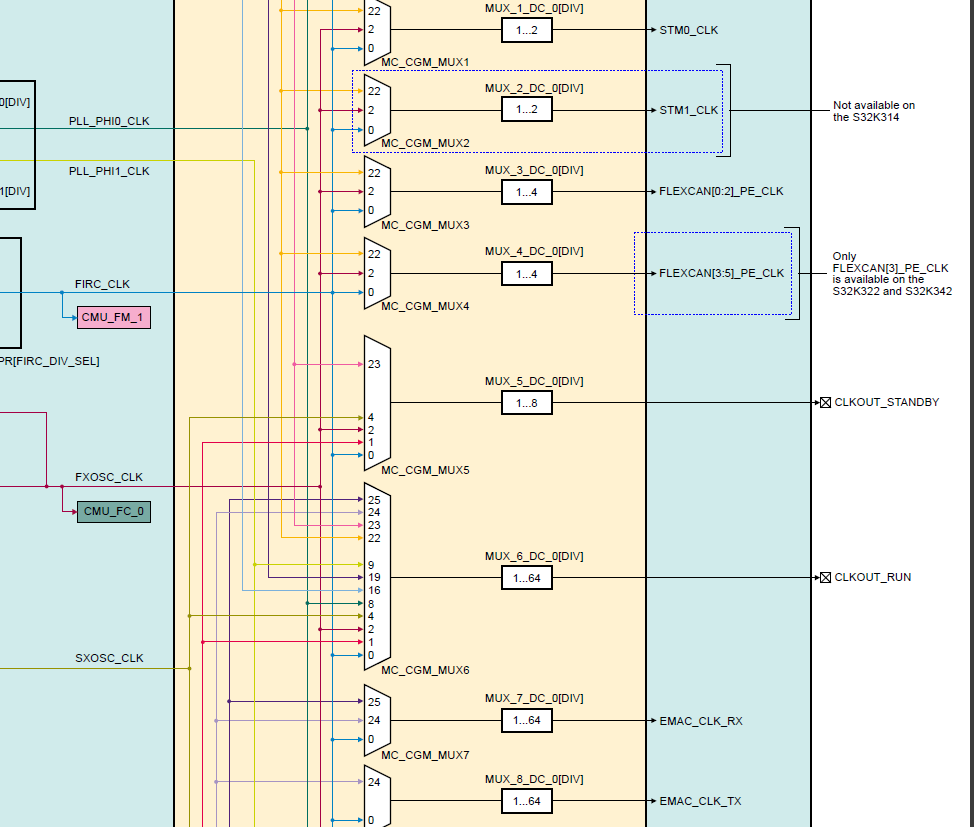

MC_CGM时钟生成模块

MC_CGM控制芯片的时钟功能。有关MC_CGM时钟控制的详细信息,请参阅时钟生成模块(MC_CGM)章节。

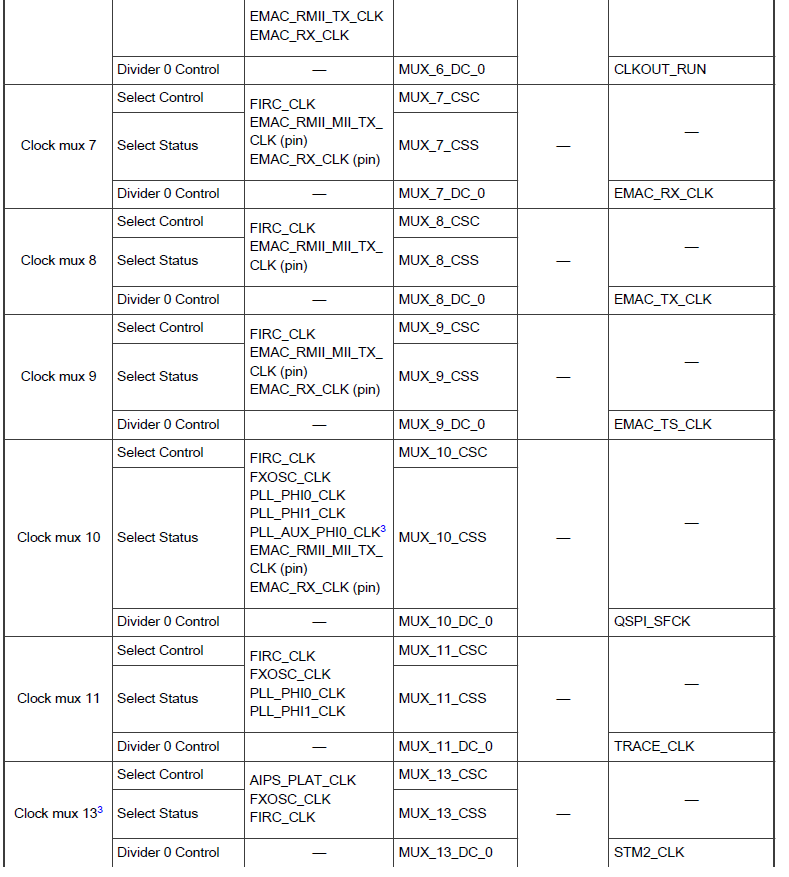

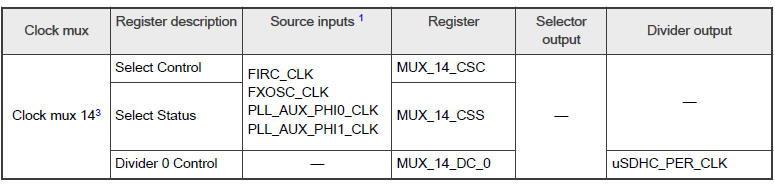

MC_CGM时钟多路复用器类型

在该芯片中,CLKOUT_RUN、CLKOUT_STANDBY和TRACE_CLK多路复用器是软件控制的多路复用器。其余的是硬件控制的多路复用器(有关软件和硬件多路复用器的详细信息,请参阅“时钟生成模块(MC_CGM)”章节)。

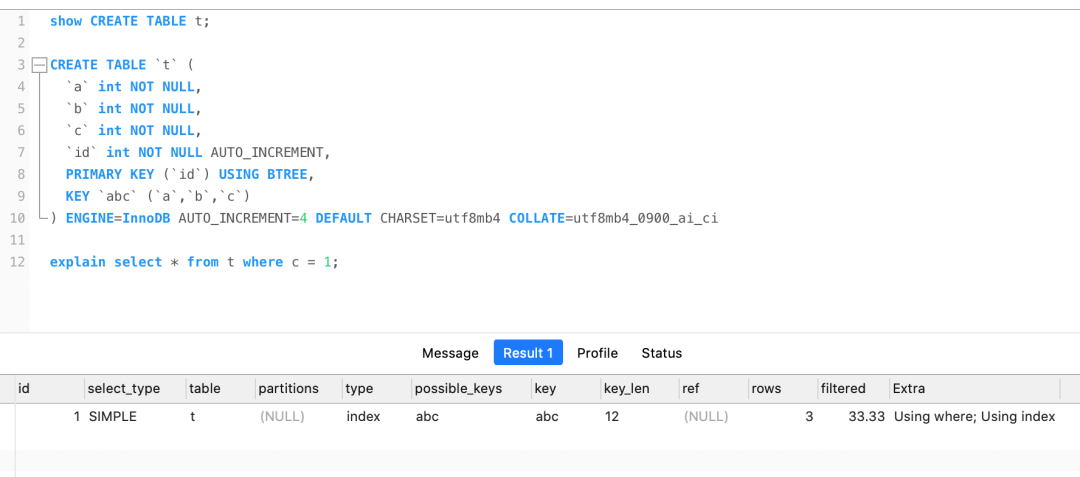

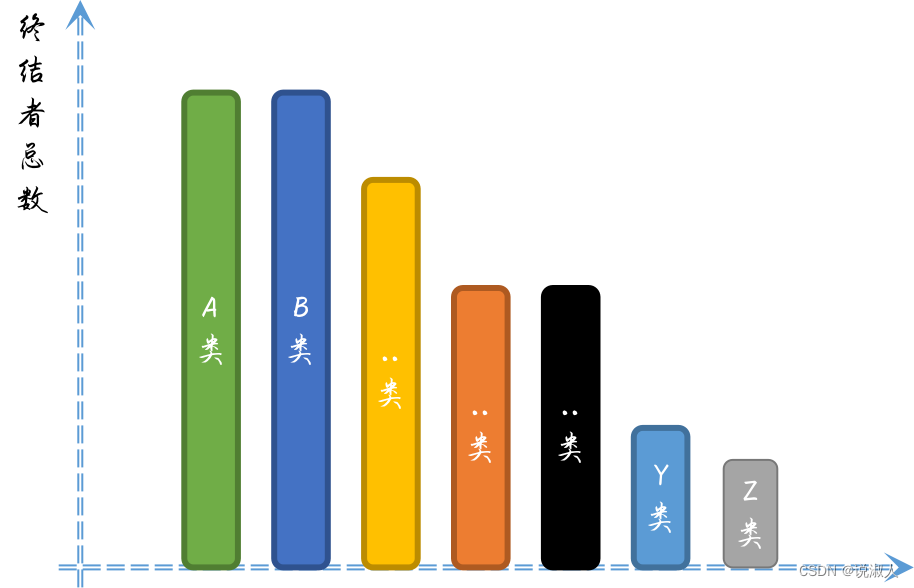

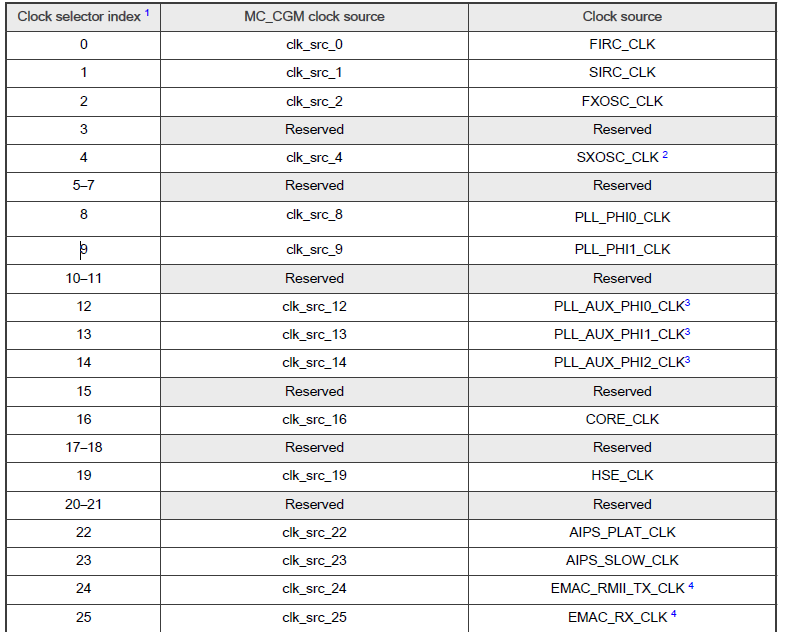

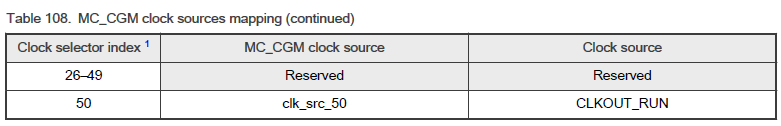

MC_CGM时钟源映射

1.所有未显示的时钟选择器索引都被保留。

2.S32K311的“SXOSC_CLK”不可用。

3.PLL_AUX_PHIn_CLK仅支持S32K388和S32K358。

4.S32K311和S32K312不支持EMAC_RMII_TX_CLK和EMAC_RX_CLK

时钟细节

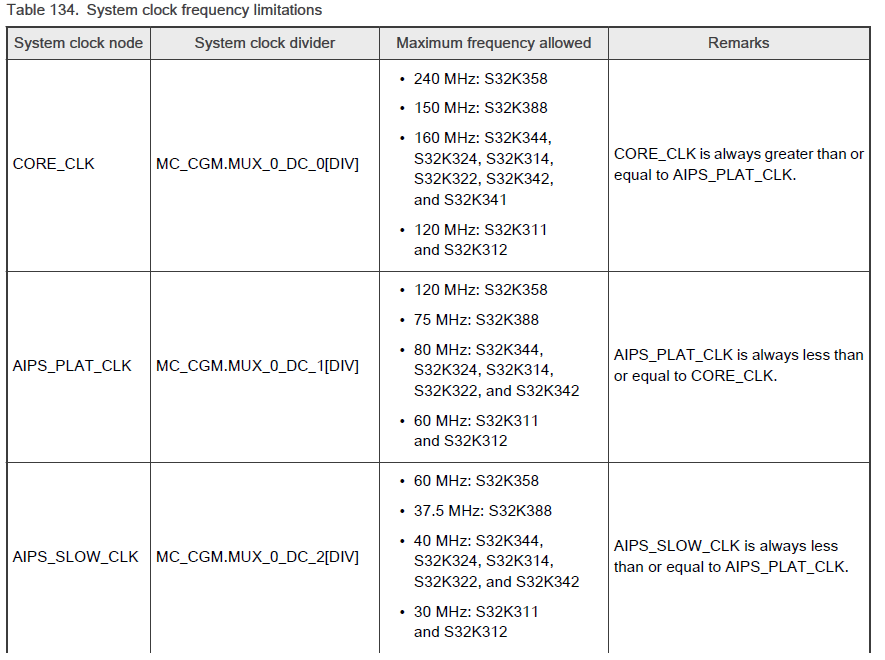

系统时钟频率限制

参考使用case

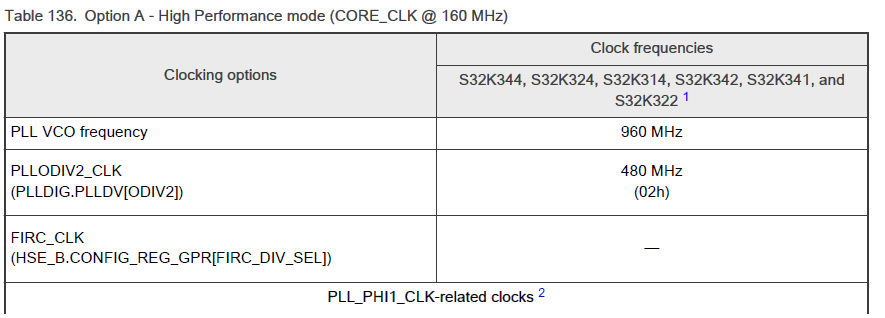

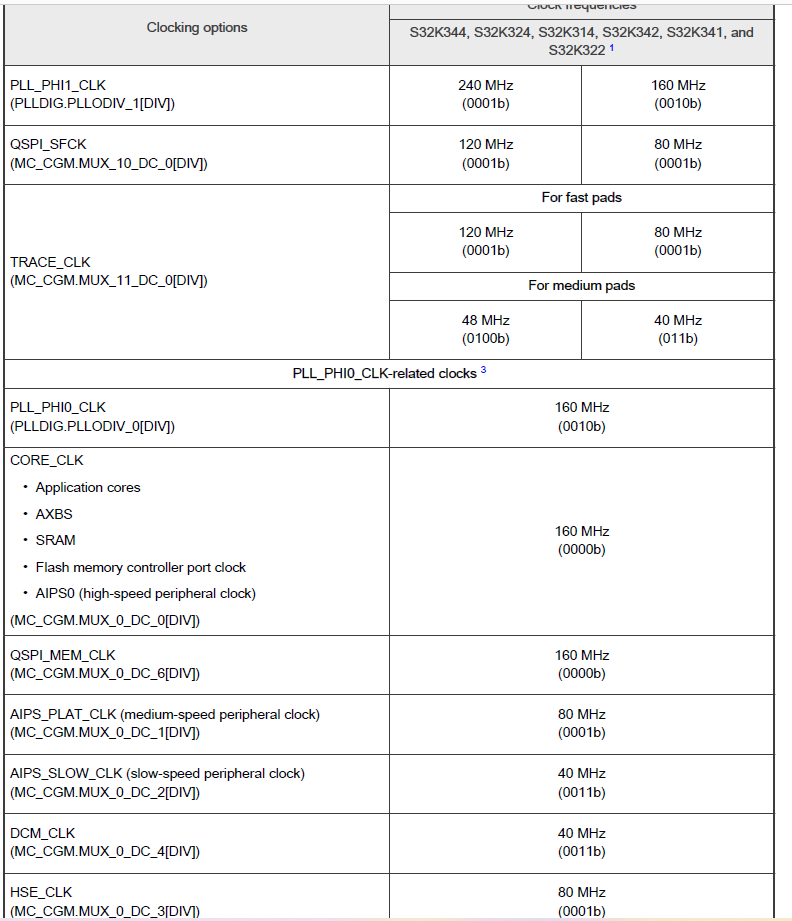

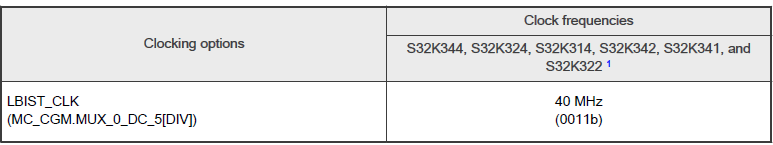

高性能模式(CORE_CLK @ 160 MHz)

1.该表不适用于S32K311和S32K312。

2.MC_CGM.MUX_10_CSC[SELCTL]和MC_CGM.MUX_11_CSC[SELCTL]必须等于1001b。

3.MC_CGM.MUX_0_CSC[SELCTL]必须等于1000b。

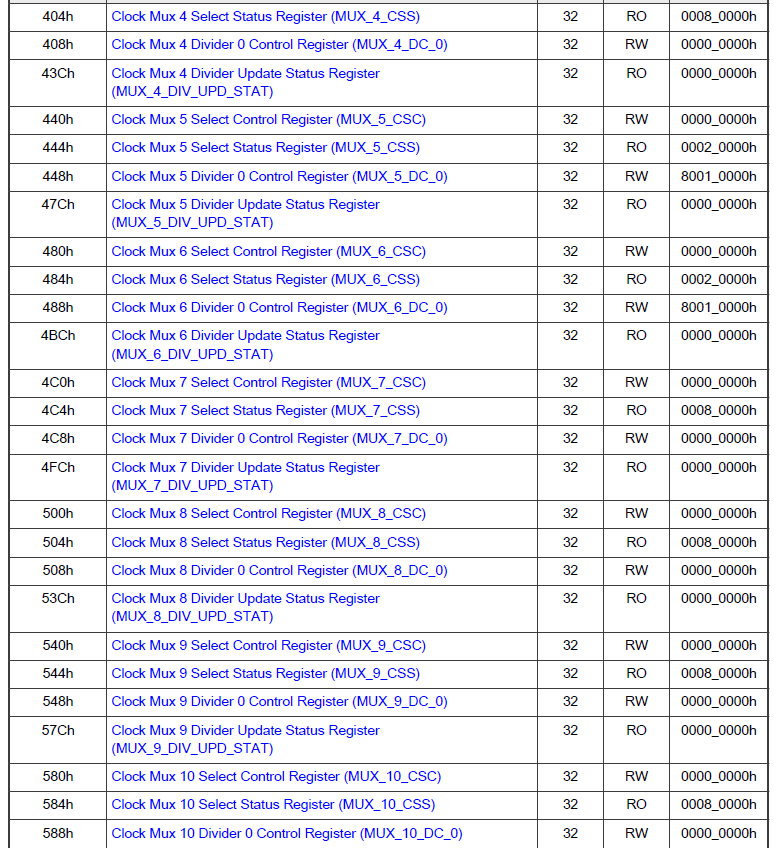

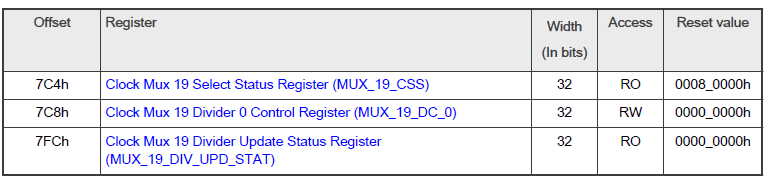

MC_CGM register descriptions

MC_CGM memory map

Clock Mux 0 Select Control Register (MUX_0_CSC)

该寄存器为0号时钟mux提供了时钟源选择控制。Clock mux 0实现硬件控制时钟切换,确保时钟切换以正常的方式发生(没有故障)。

此寄存器仅在破坏性复位时复位。

对该寄存器中所有pcfs相关字段的更新必须是原子写入,这意味着单个写入必须更新CLK_SW、RAMPDOWN和RAMPUP字段。即使您希望触发RAMPUP或RAMPDOWN进程,也必须将RAMPUP和RAMPDOWN位设置在一起,否则将无法执行所需的PCFS序列。

SELCTL-时钟源选择0000b - FIRC 1000b - PLL_PHI0_CLK

SAFE_SW-将1写入该位向FIRC发出安全时钟切换请求。在请求安全时钟切换操作后,该位将自动清除,并在状态寄存器中设置相应的位。

CLK_SW-对该位写入1将对时钟mux 0发出时钟切换请求。在请求时钟切换操作后,该位将自动清除,并在状态寄存器中设置相应的位。

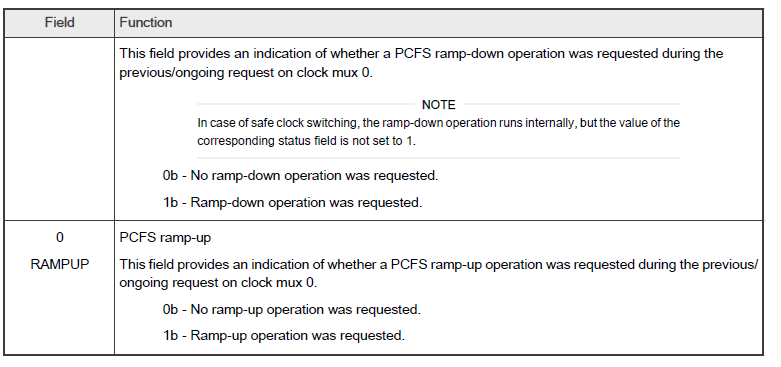

RAMPDOWN-pcf缓降

将1写入该位将使PCFS斜率下降请求为mux 0计时。在请求PCFS斜率下降操作后,该位将被自动清除,并在状态寄存器中设置相应的位。

RAMPUP-pcf缓升

向这个位写入1会产生PCFS对时钟mux 0的递增请求。请求PCFS递增操作后,将自动清除该位,并在状态寄存器中设置相应的位。

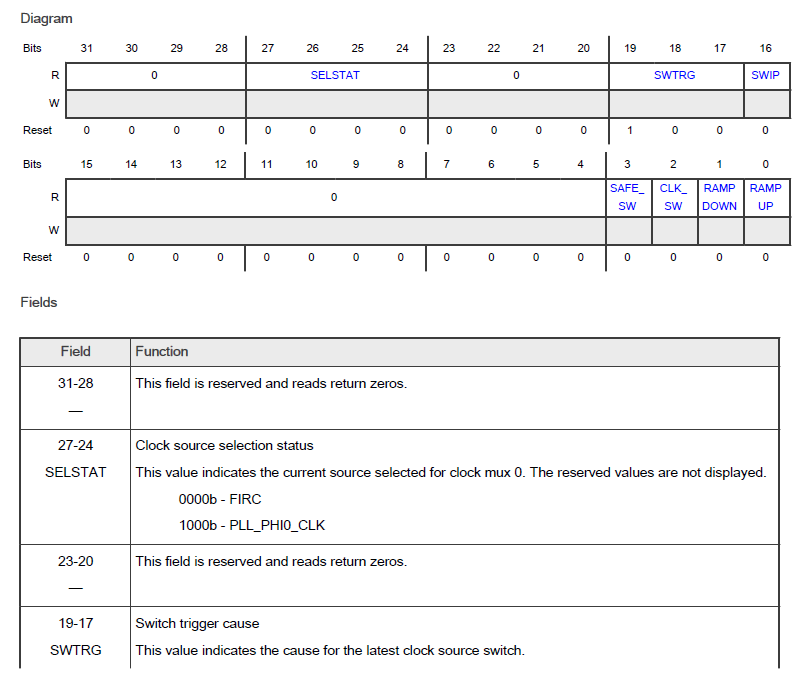

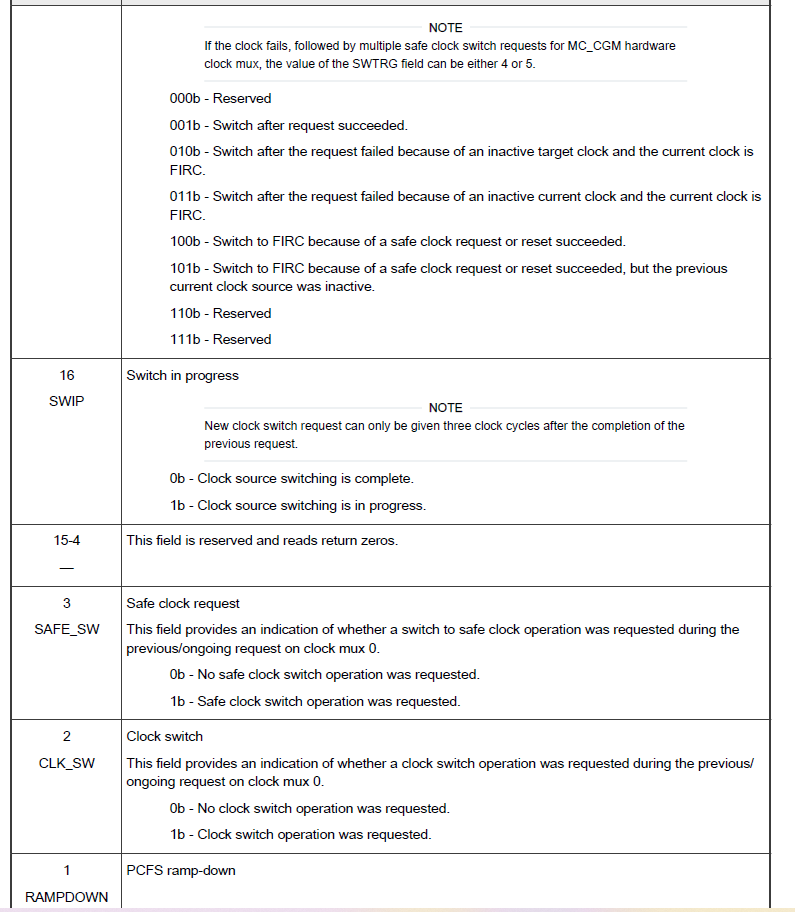

Clock Mux 0 Select Status Register (MUX_0_CSS)

该寄存器为0号时钟mux提供当前的时钟源选择状态。

此寄存器仅在破坏性复位时复位。

Clock Mux 0 Divider 0-6 Control Register (MUX_0_DC_0-6)

该寄存器为时钟mux 0控制时钟分压器0-6。

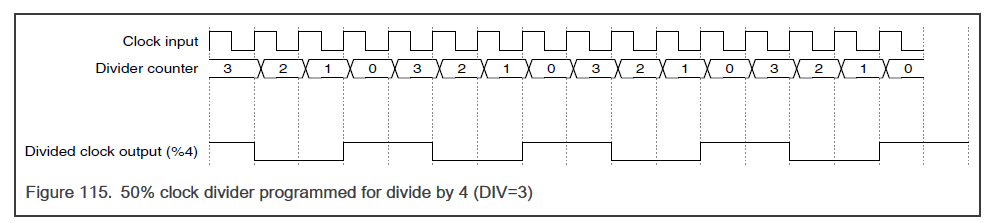

这个分频器是50%占空比的分频器。

关于50%占空比分频器,解释如下:

50%占空比分频器产生一个真正的分压器时钟。除法因子总是整数,但不限于偶数。分频时钟的上升沿始终与分频源时钟的上升沿同步,但下降沿与上升沿或下降沿同步,这取决于分频因子是偶数还是奇数。如果输入时钟占空比为50%,则分频输出时钟保持相同的50%占空比。

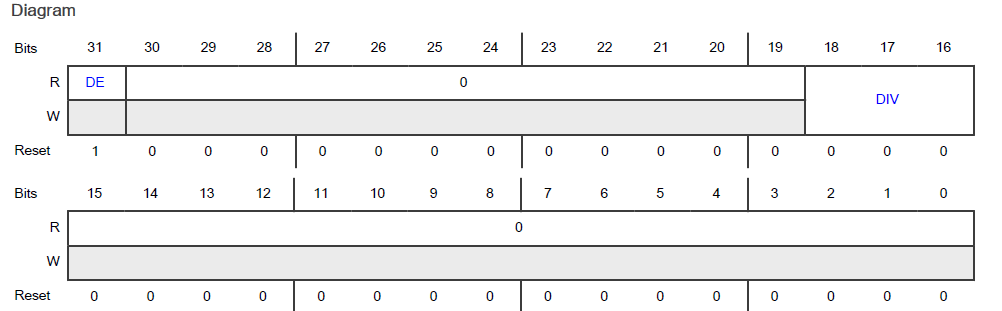

寄存器:

DE-分频使能

DIV-实际分频因子为DIV+1

Clock Mux 0 Divider Trigger Control Register (MUX_0_DIV_TRIG_CTRL)

该寄存器选择在写入相应的除法器配置寄存器时立即更新与时钟mux0相关的除法器(称为Immediate divider update),还是仅在写入MC_CGM_MUX_0_DIV_TRIG寄存器时更新(称为Common trigger divider update)。当配置了公共触发器更新时,该寄存器还使用片上AXBS控制中止握手协议的启动。当需要改变时钟分压器之间的除法值比例时,需要软件配置与片上AXBS握手的HHEN字段。

HHEN:选择是否终止握手协议 0B-没有启动停止握手协议。

TCTL:配置分频触发方式,0b-立即更新 1b-共同更新

分频时钟图参考:

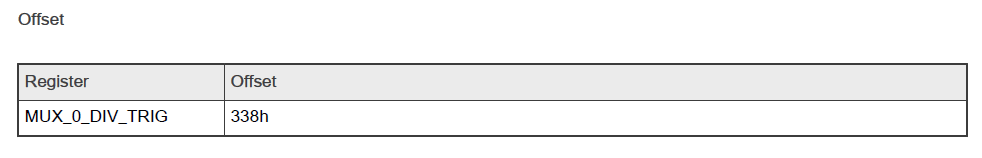

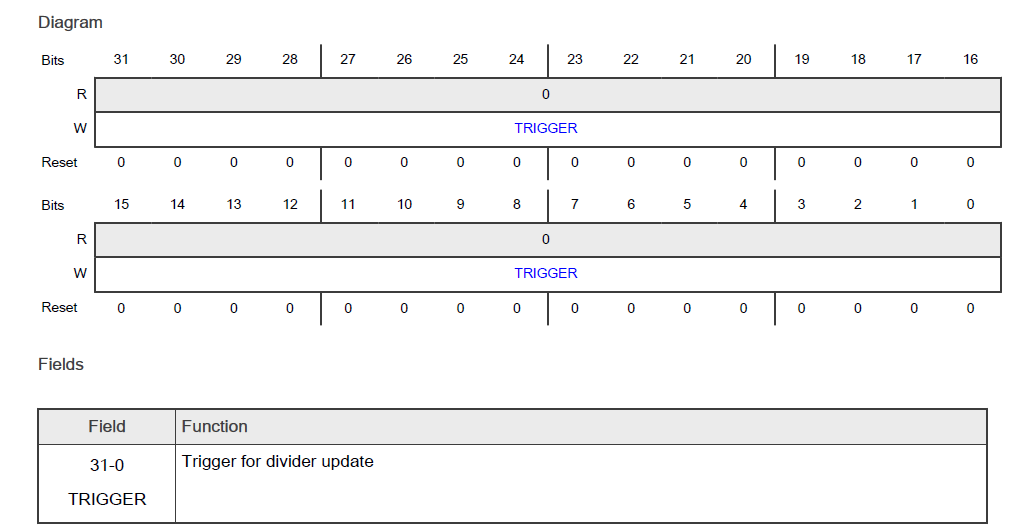

Clock Mux 0 Divider Trigger Register (MUX_0_DIV_TRIG)

当上面的Trigger配置为Common时,向该寄存器写入任何值都会触发除法器。

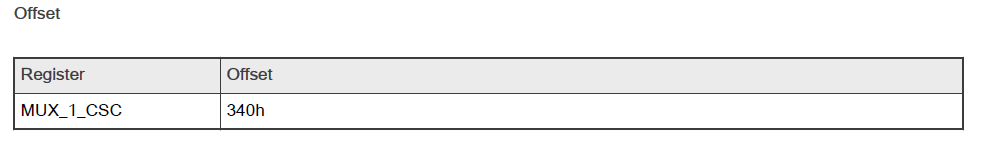

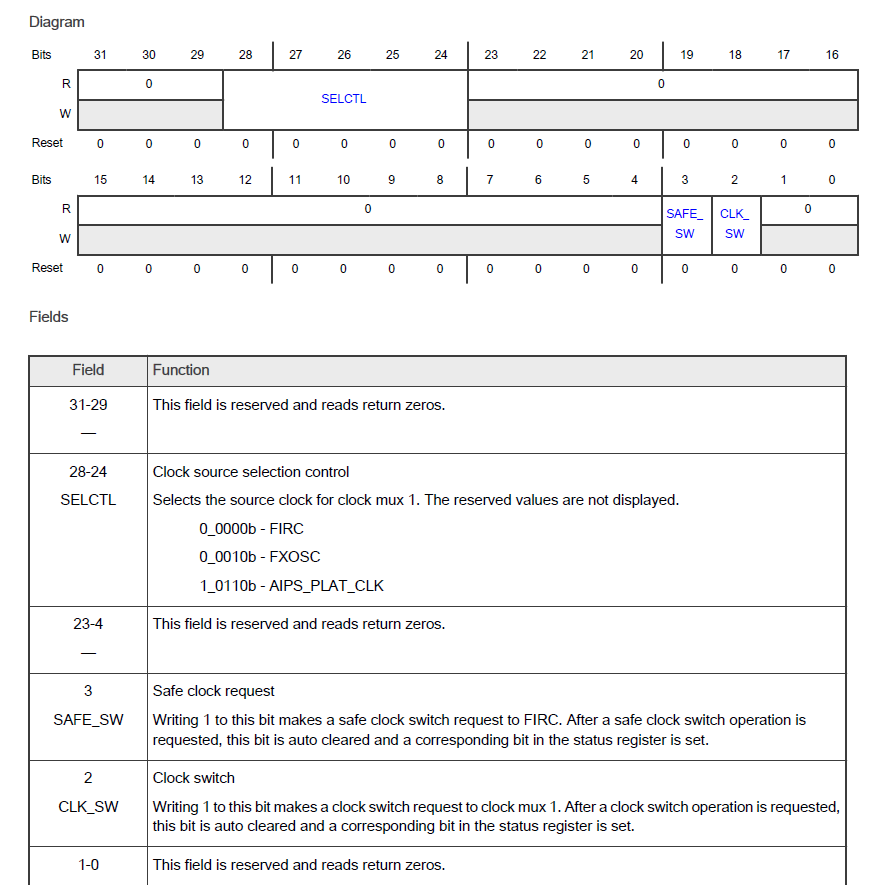

Clock Mux 1 Select Control Register (MUX_1_CSC)

该寄存器为时钟mux 1提供了时钟源选择控制。时钟mux 1实现硬件控制时钟切换,确保时钟切换以正常的方式发生(没有故障)。

SELCTL:选择时钟源 0_0000b - FIRC 0_0010b - FXOSC 1_0110b - AIPS_PLAT_CLK

SAFE_SW-将1写入该位向FIRC发出安全时钟切换请求。在请求安全时钟切换操作后,该位将自动清除,并在状态寄存器中设置相应的位。

CLK_SW-对该位写入1将对时钟mux 0发出时钟切换请求。在请求时钟切换操作后,该位将自动清除,并在状态寄存器中设置相应的位。

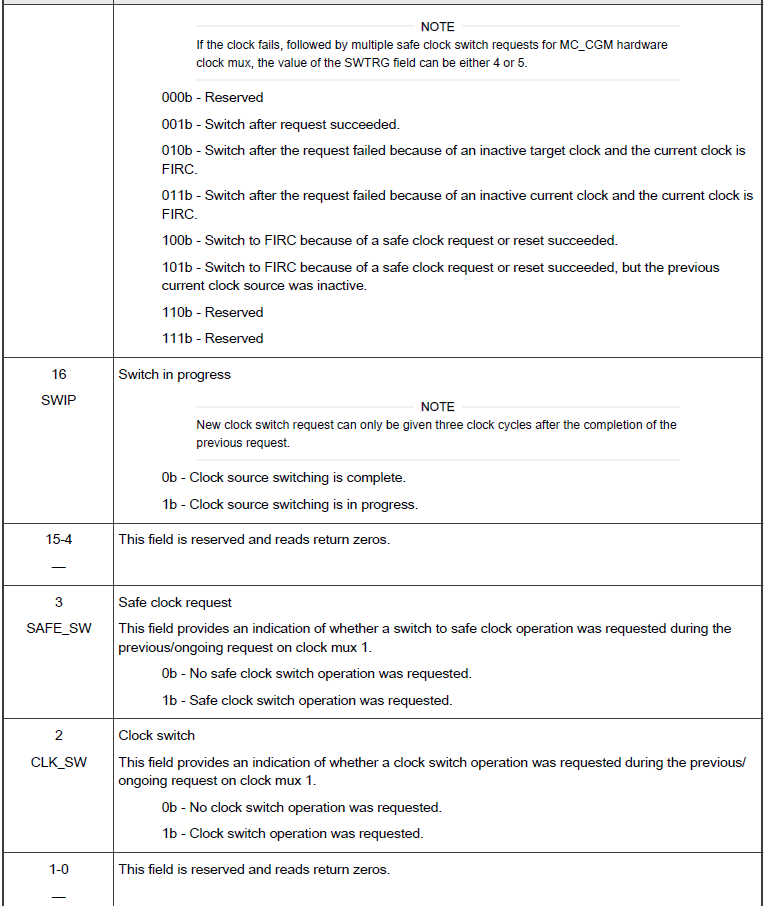

Clock Mux 1 Select Status Register (MUX_1_CSS)

反馈MUX1时钟状态

SWIP:反馈时钟切换状态

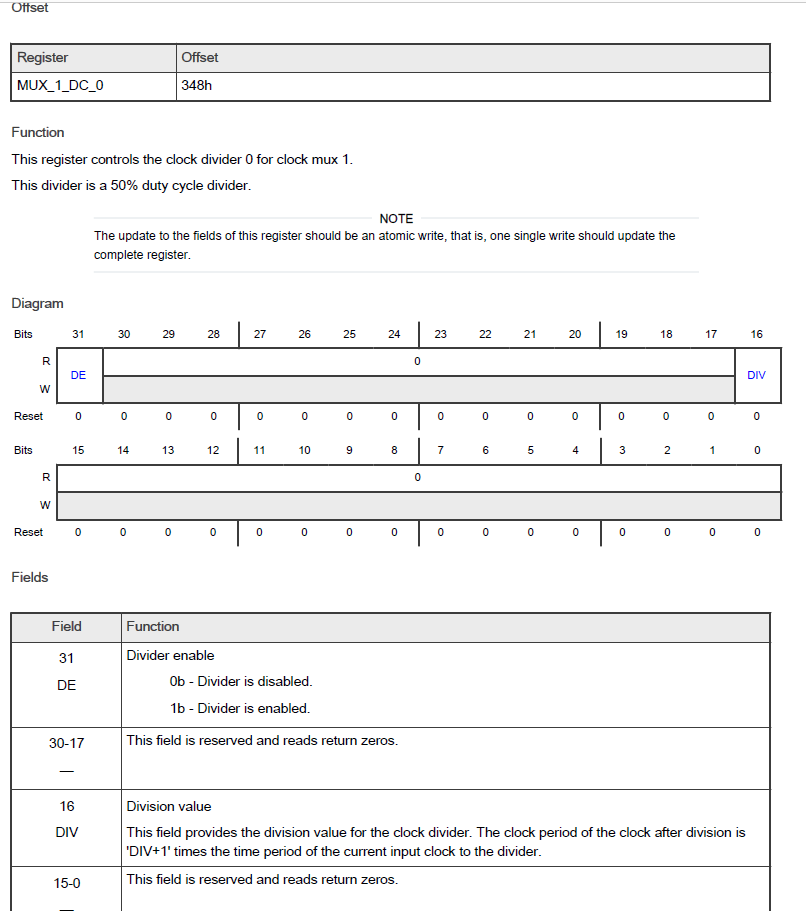

Clock Mux 1 Divider 0 Control Register (MUX_1_DC_0)

Mux1时钟分频

其他Mux时钟和上面的类似,只是输出时钟不同,分频图如下:

Fast Internal RC Oscillator (FIRC)

FIRC数字接口控制内部48 MHz RC振荡器系统。

FIRC register descriptions

FIRC memory map

Status Register (Status_Register)

Standby Enable Register (STDBY_ENABLE)

Configuration REG_GPR (CONFIG_REG_GPR)

Slow Internal RC Oscillator (SIRC)

SIRC数字接口控制内部芯片上32 KHz RC振荡器系统。

SIRC register descriptions

SIRC memory map

Status Register (SR)

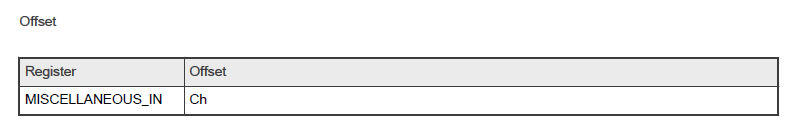

Miscellaneous input (MISCELLANEOUS_IN)

Fast Crystal Oscillator Digital Controller (FXOSC)

对于S32K344/S32K324/S32K314:对于Bypass模式应用,当FXOSC处于关闭/禁用状态时,EXTAL引脚应该被拉低。

•初始化FXOSC时:当FXOSC为Bypass模式时,只有使能FXOSC后,才能使能外部时钟源。

•禁用FXOSC功能时:当FXOSC功能在Bypass模式下使用时,必须外部时钟源已经处于非激活状态,才能禁用FXOSC功能。

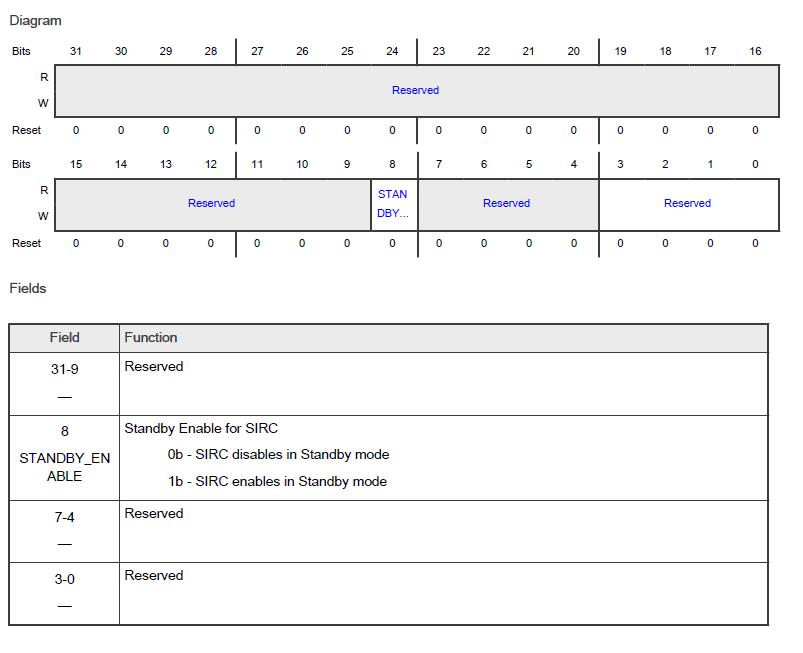

Functional description

Power-Down模式是FXOSC在任何重置后的默认条件:POR、破坏性或功能

FXOSC memory map

FXOSC base address: 402D_4000h

FXOSC Control Register (CTRL)

OSC_BYP:绕过内部振荡器。

COMP_EN:Crystal mode为1,Single-Input Bypass设置为0

EOCV:指定计数结束。

振荡器计数器在除4的晶体时钟上运行,并计数到EOCV 128。这个计数周期确保外部振荡器时钟信号在系统选择FXOSC作为源之前是稳定的。

注意:必须将EOCV设置为适当的值,以允许时钟和占空比稳定下来,并确保OSC_STAT在晶体启动时间内得到设置。

-在crystal模式下,EOCV值必须使用初始化FXOSC中的公式根据晶体规格计算到合适的值。

-在Single-Input Bypass模式下,EOCV值无关紧要。FXOSC保持计数器复位。

• 修改EOCV前,必须禁用FXOSC

GM_SEL:选择由FXOSC放大器应用的跨导。此设置取决于晶振规格。

•在crystal模式下,FXOSC将不能在零跨导(GM_SEL = 0000b)下工作。

ALC_D-是否启用自动电平控制

OSCON-是否使能FXOSC

Oscillator Status Register (STAT)

指示FXOSC状态是否稳定

Slow Crystal Oscillator Digital Controller (SXOSC)

•在功能振荡器模式下产生32 KHz时钟输出

•包含一个状态寄存器,当晶体稳定时间完成时,状态寄存器的值变为1

•包含一个可以下电的振荡器

操作模式

Crystal mode

在此模式下晶振生成时钟

Bypass mode

在这种模式下,晶振从extal和xtal端口中移除,extal由旁路时钟驱动,xtal不连接。

SXOSC register descriptions

SXOSC memory map

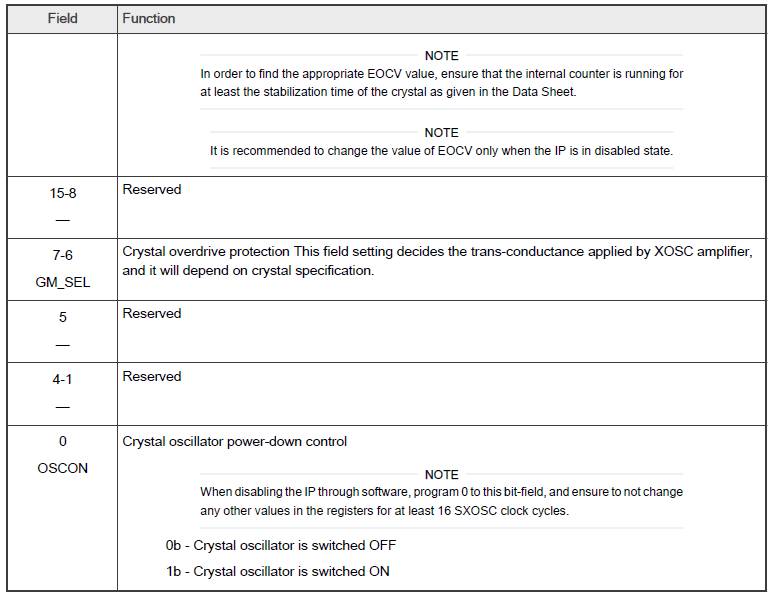

Oscillator Control Register (SXOSC_CTRL)

CURR_PRG_SF-这些位指定电平移位电流的可编程性。

CURR_PRG_COMP-这些位指定比较器电流的可编程性。

EOCV-这些位指定计数值的结束。当振荡器稳定计数器被打开时,这个值被用于比较。这个计数周期确保外部振荡器时钟信号在被系统选择之前是稳定的。振荡器计数器运行在晶振时钟除以4,计数值到EOCV * 128。

GM_SEL-晶振超速保护。该电场设置决定了XOSC放大器所应用的跨导,它将取决于晶体规格

OSCON- 0b -晶体振荡器关闭 1b -晶体振荡器处于ON状态

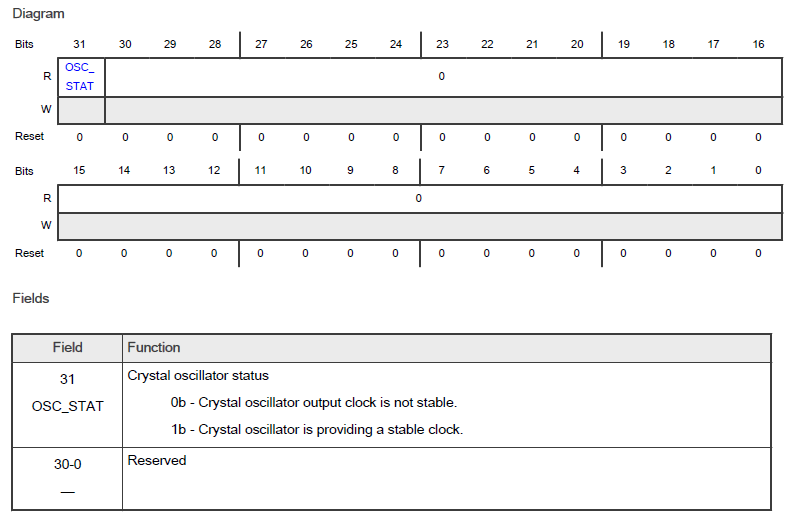

Oscillator Status Register (SXOSC_STAT)

指示SXOSC状态是否稳定

PLL Digital Interface (PLLDIG)

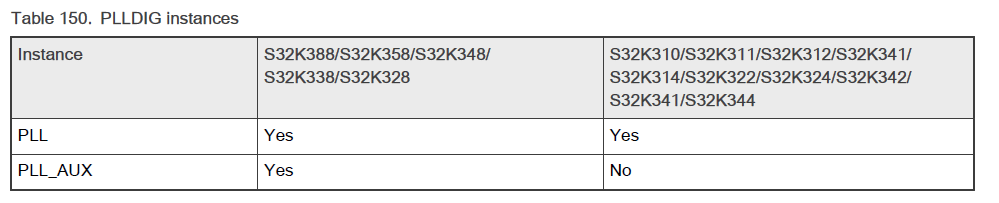

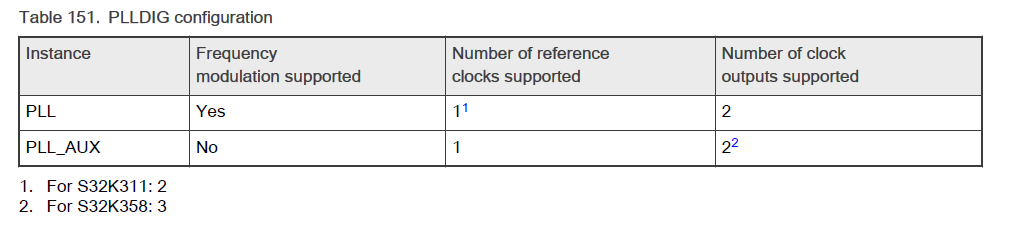

该芯片最多有2个PLLDIG模块,S32K324只有一个

PLLODIV_0和PLLODIV_1寄存器只支持word访问。写入这些寄存器时,必须保留保留字段的默认值。

PLLDIG仅支持向下扩展调制高达160 MHz的PLL PHI时钟输出。

工作模式

输入时钟频率

输入时钟为外部晶振频率,8-40M

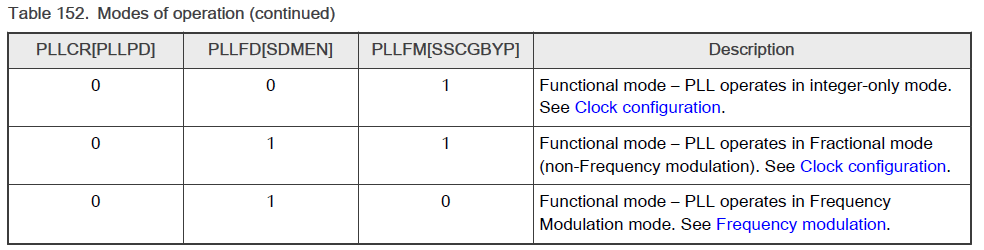

Clock configuration时钟配置

各个模式下fpll_VCO的计算方式

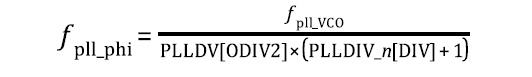

fpll_phi频率计算:

举例如下:

输入晶振为16M,配置为integer-only mode,PLLDV[RDIV]配置为2,PLLDV[MFI]配置为120,PLLDV[ODIV2]配置为1,PLLDIV_0[DIV]配置为5,则:

fpll_VCO = 16M/2 * 120=960M

fpll_phi_0 = 960M/(1*(5+1)) = 160M

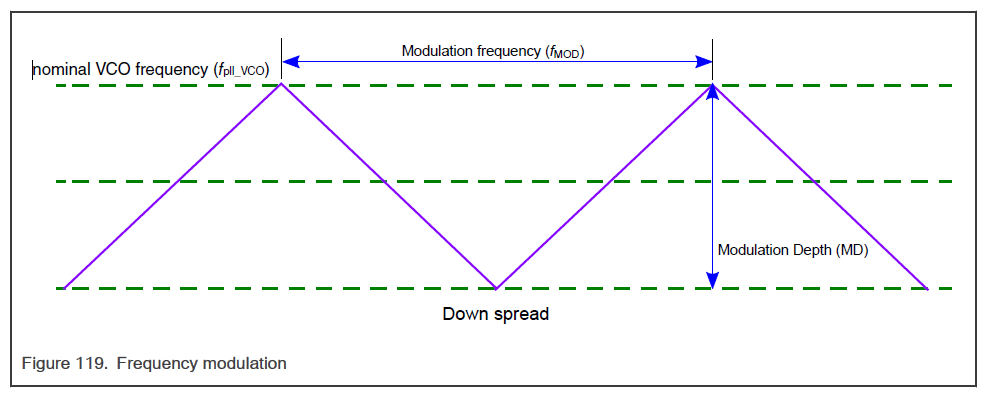

频率调制

在调频模式下,锁相环产生一个调频时钟。

将1写入PLLFM[SPREADCTL]以选择向下扩展调制。下图显示了own-spread调制的示例。

调频编程

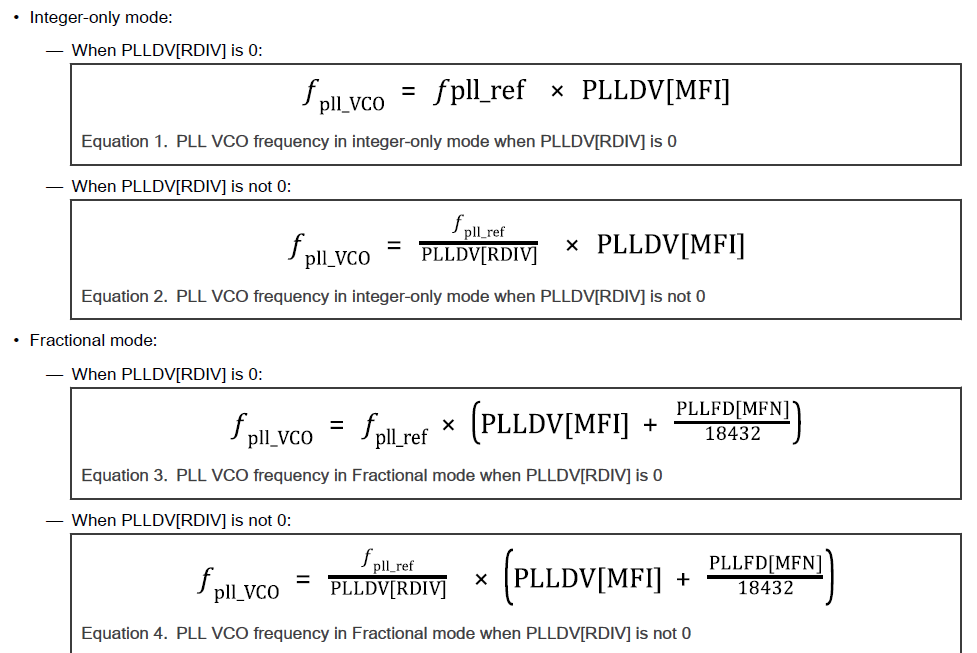

调制深度和调制频率编程使用步长(PLLFM[STEPNO])和步长(PLLFM[STEPSIZE])。下表显示了为调频编程锁相环时计算过程中使用的变量

使用下面的公式配置锁相环用于调频。

只有满足公式9才可以实现调频

必须将0写入PLLFM[SSCGBYP],将1写入PLLFD[SDMEN]才能启用调频

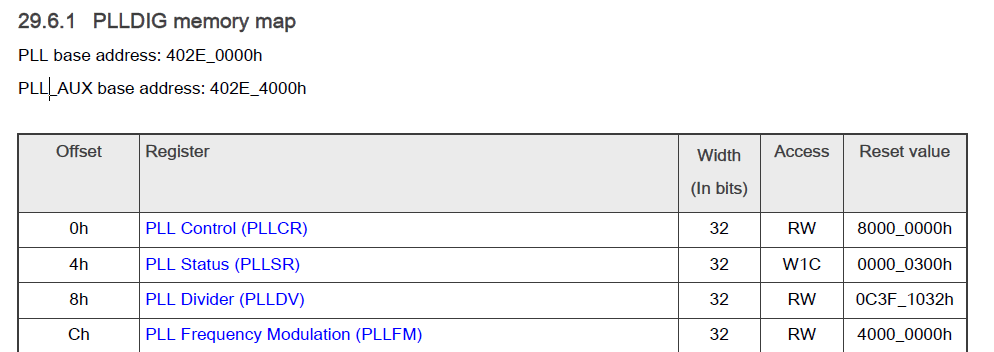

PLLDIG register descriptions

PLL寄存器描述

PLL Control (PLLCR)

PLLPD:为1时禁止PLL

PLL Status (PLLSR)

LOL:PLL失锁状态,1为检测到失锁

LOCK:指示PLL是否Lock,1为locked

PLL Divider (PLLDV)

ODIV2:fpll_VCO分频因子

RDIV:输入时钟预分频因子

MFI:设置锁相环反馈回路中分频器的值,用来超频

PLL Frequency Modulation (PLLFM)

频率调制配置

SSCGBYP:屏蔽频率调制,为1时屏蔽

SPREADCTL:表示调制扩散到标称频率以下。这个字段必须写1

STEPSIZE:调频模式下,调制深度和频率的步长

STEPNO:提供在频率调制模式中实现调制深度的Step数

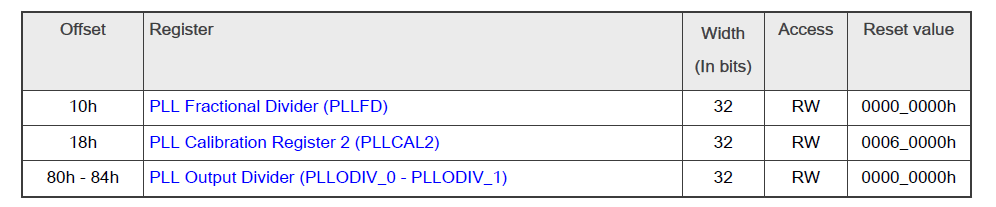

PLL Fractional Divider (PLLFD)

开启和配置调频

SDMEN:启用分数模式。

SDM2:当您处于分数模式(SDMEN = 1)时,将1写入该字段。

SDM3:当您处于分数模式(SDMEN = 1)时,将1写入该字段。

MFN:设置分数环除法因子的分子。必须将小于18432的值写入该字段。禁用分数模式时,必须写入000_0000_0000_0000b。

PLL Calibration Register 2 (PLLCAL2)

ULKCTL:定义实现解锁所需的精度。

如果参考周期窗口中的VCO时钟周期数超出此字段定义的周期数,则锁定计数器决定解锁。

00b -解锁范围=期望值±9(当PLLFM[SSCGBYP] = 1时推荐)解锁范围=期望值±9(当PLLFM[SSCGBYP] = 1时推荐)

01b -解锁范围=期望值±17(当PLLFM[SSCGBYP] = 0时推荐)解锁范围=期望值±17(当PLLFM[SSCGBYP] = 0时推荐)

10b -解锁范围=期望值±33

11b -解锁范围=期望值±5

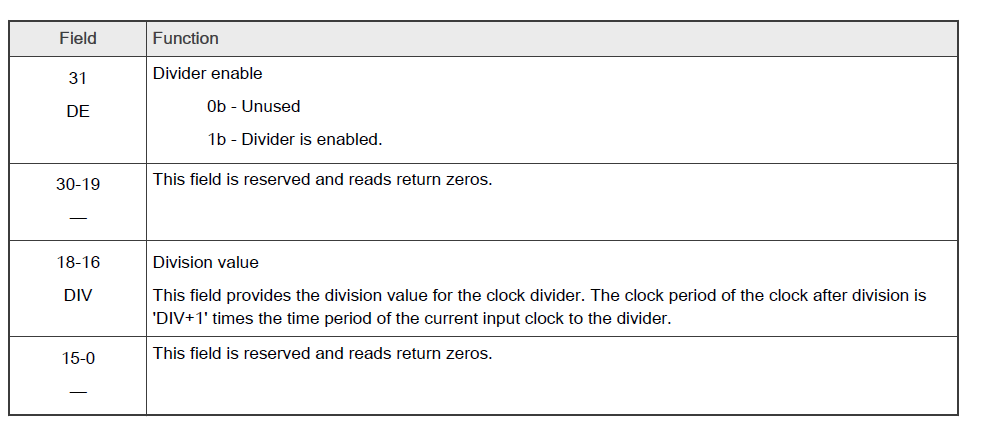

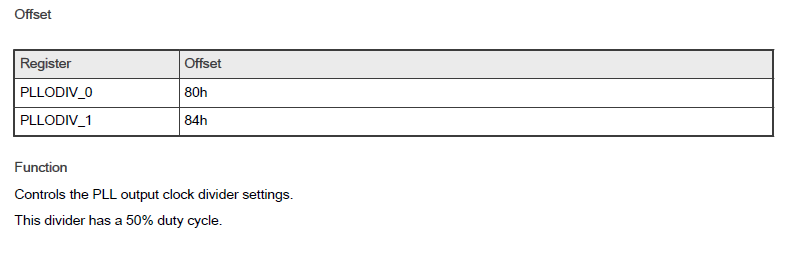

PLL Output Divider (PLLODIV_0 - PLLODIV_1)

DE:使能分频

DIV:分频因子,实际分频值为DIV+1

Real Time Clock (RTC)

该芯片包含一个RTC(实时时钟)定时器和API(自主周期性中断)定时器实例,两者都可以执行32位比较。

RTC始终处于ON状态中,因此可在RUN模式和STANDBY模式下使用。RTC和API定时器都可以在低功耗模式下产生中断和唤醒。

RTC支持1μs的分辨率,具有高速内部振荡器时钟(1/48MHz (FIRC) * 48 (RTC计数器)= 1μs)

该芯片支持通过时钟源SIRC和SXOSC进行功能复位的无缝RTC操作

API能够在不停止计时器的情况下独立地更改计时器比较值(APIVAL)

API还可以与Comparator模块结合使用。在STANDBY模式配置中,API被配置为生成一个START / NEXT类型的信号来通知Comparator模块必须进行“比较”

实时时钟(RTC)是一种自由运行的计数器,用于计时应用。RTC可以配置为在预定义的时间间隔内产生中断,而不受操作模式(运行模式或低功耗模式)的影响。如果在低功耗模式下,达到RTC间隔,RTC首先生成唤醒,然后断言中断请求。RTC还支持一个API函数,用于生成定期唤醒请求以退出低功耗模式或中断请求。

特点

32位计数器

可选的时钟源

可选512预分频器和可选32预分频器来运行32位计数器。

RTC中断使能中断。

计数器在所有操作模式下运行。

当计数器被软件禁止并复位到RTC模块时RTC counter复位

自主周期性中断支持包括:

- 32位比较值支持唤醒间隔/中断范围

- API逻辑有一个单独的enable来支持在RTC运行时更改比较值

- API中断使能中断

- 可在所有模式下运行

- API比较值可以在RTC运行时修改

可选中断RTC匹配,API匹配,和RTC翻转。

功能描述

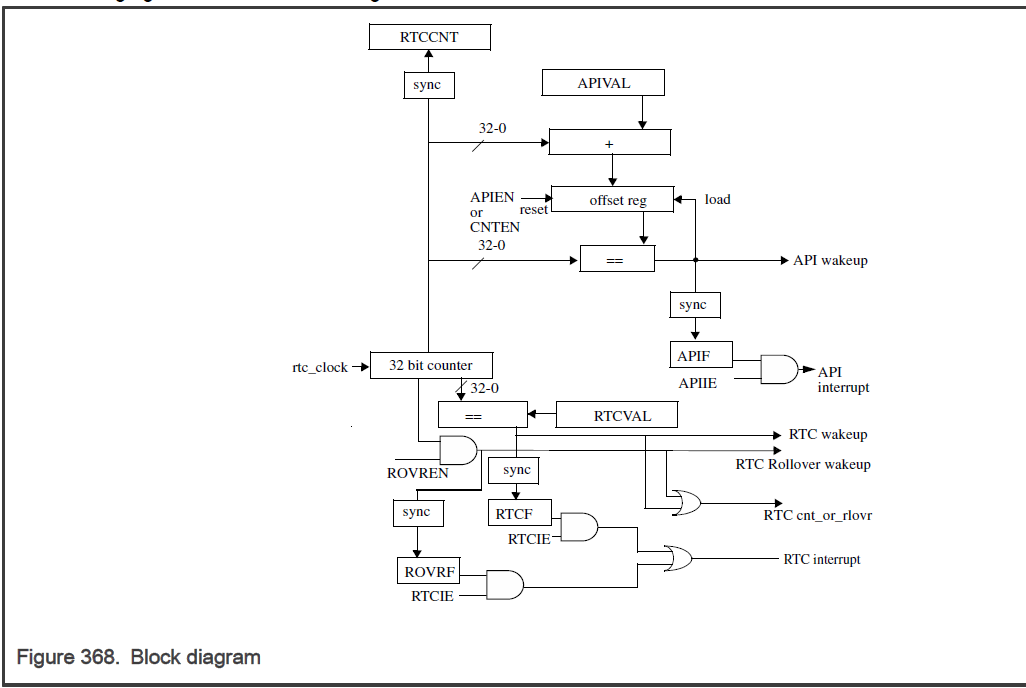

RTC

RTC由一个32位的CNTEN位启用的空闲运行计数器组成(当CNTEN为负时,异步重置计数器并在启用时同步启用计数器)。禁用CNTEN后,RTCVAL, APIVAL,需要再次写入所需的功能。计数器的值可以通过RTC计数器寄存器(RTCCNT)寄存器读取。请注意,由于时钟同步,RTC计数器寄存器(RTCCNT)的值可能代表以前的计数器值。计数器和读取值之间的差值取决于计数器时钟和总线时钟的比值。两者之间的最大可能差异是6个计数值

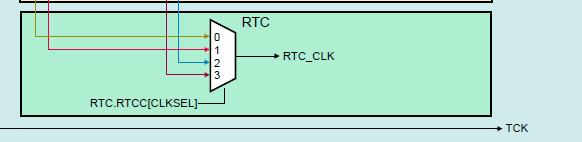

计数器的时钟源是通过CLKSEL字段选择的,该字段为RTC/API提供了四个时钟选项。4个时钟源分别为:时钟源0、时钟源1、时钟源2和时钟源3。时钟多路复用器的输出可以被512和32的组合所除,从而为不同的时钟源提供不同的计数周期。注意,当切换RTC/API时钟源时,CNTEN位应该被禁用。

当计数器位31-0的RTC计数器寄存器(RTCCNT)计数器值与RTCVAL字段中的32位值匹配时,将设置RTCF中断标志位(在正确的时钟同步之后)。如果设置了RTCIE中断使能位,则产生RTC中断请求。RTC比较值寄存器(RTCVAL)只有在INV_RTC位为清零时才能写入寄存器。最初INV_RTC=0,因此RTC比较值寄存器(RTCVAL)可以写入一次,因此INV_RTC得到设置。这个位现在只能通过启用RTC计数器来清除。

在计数器被启用后,RTC比较值寄存器(RTCVAL)可以在任何时候写入,直到RTC再次被禁用。RTC比较值寄存器(RTCVAL)首先同步到RTC时钟域,因此,如果RTC比较值寄存器(RTCVAL)在接下来的2-3个RTC时钟中由于之前的RTCVAL而发生计数器匹配时更新,RTCF标志将被设置。但是,如果RTC比较值寄存器(RTCVAL)在没有计数器匹配之前更新,则在计数器匹配新的RTC比较值寄存器(RTCVAL)时设置RTCF标志。

如果在低功耗模式下发生匹配,则RTC首先生成唤醒请求强制唤醒到运行模式,然后设置RTCF标志。

如果RTC比较值寄存器(RTCVAL)在计数器匹配后更新,新的RTC比较值寄存器(RTCVAL)值不应该在接下来的6个RTC计数器值之内

当RTC计数器从0xFFFF_FFFF到0x0000_0000时会触发一个翻转唤醒或中断。翻转标志通过设置ROVREN位使能。如果使能RTCIE,将为RTC计数器翻转生成中断请求。如果系统处于低功耗模式,RTC计数器翻转与此位导致从低功耗模式唤醒

翻转唤醒和RTC唤醒都在禁用CNTEN时异步解除断言。

所有标志和计数器值都与总线时钟同步。假设通过CLKSEL选择的Bus时钟和RTC时钟的关系如下:

总线时钟>= (1.5 * RTC时钟)/(div_factor)

•如果DIV32EN和DIV512EN都被禁用,则div_factor = 1

•如果DIV32EN=1和DIV512EN=0,则div_factor = 32

•如果DIV32EN=0和DIV512EN=1,则div_factor = 512

•如果DIV32EN和DIV512EN都使能,则div_factor = 512 * 32 = 16384

在使用RTC唤醒作为唤醒源的情况下,在启用所需的唤醒并确保在总线时钟禁用和唤醒事件之间有足够的时间间隔(少数总线时钟或RTC时钟周期,以较慢者为准)后,应禁用总线时钟。

API功能描述

通过设置APIEN位使能自动中断功能。32位APIVAL字段选择触发中断和/或唤醒事件的时间间隔。由于RTC是一个自由运行的计数器,APIVAL被添加到当前计数中以计算偏移量。当计数器达到偏移计数时,将生成中断和/或唤醒请求。然后重新计算偏移值,并在达到新值时再次重新触发新请求。只有当CNTEN和APIEN位被设置且APIVAL不为零时,API功能才会被启用。APIVAL也可以随时更新。APIVAL更新后,根据前一个值生成第一个API中断。从第二个中断开始,使用新的APIVAL生成API中断。

当比较达到时,APIF中断位被设置(在正确的时钟同步之后)。如果设置了APIIE中断使能位,则会生成API中断请求。如果在低功耗模式下有匹配,那么API首先生成一个唤醒请求,强制唤醒进入正常操作,然后设置APIF标志。

当CNTEN被禁止时,API功能重置,尽管唤醒API没有异步地用CNTEN去断言。如果APIEN在计数器匹配时被禁用,则偏移APIF可以失效。

工作模式

功能模式

RTC有两种功能运行模式,正常运行和低功耗模式。在正常操作中,所有RTC寄存器都可以读或写。RTC/API和相关的中断是可选启用的。在低功耗模式下,总线接口被禁用。RTC/API已启用(如果在进入低功耗模式之前启用)。

Debug mode

在进入调试模式时,如果设置了FRZEN,则RTC计数器冻结在最后一个有效计数上。在退出调试模式时,计数器从冻结值继续。

RTC register descriptions

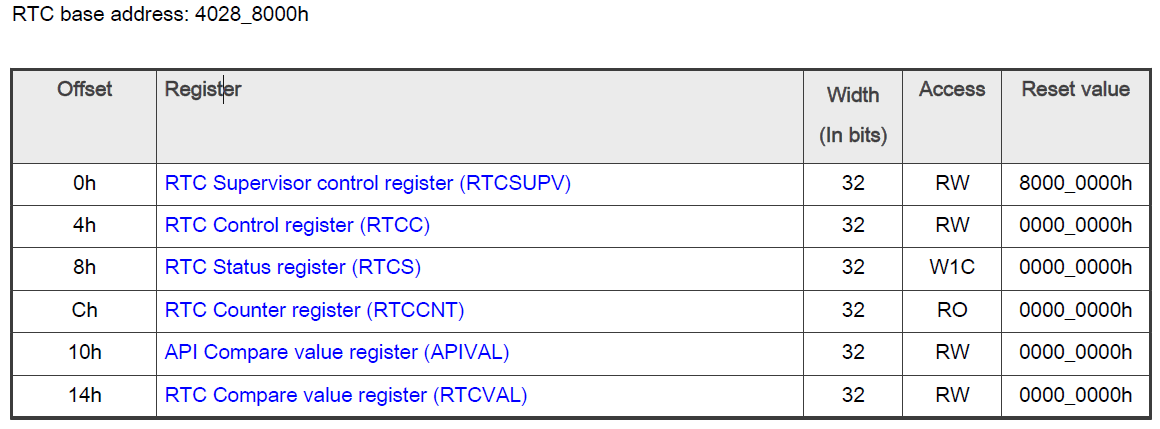

RTC memory map

RTC Supervisor control register (RTCSUPV)

RTCSUPV寄存器包含SUPV位,决定其他寄存器是在supervisor模式还是用户模式下可访问。

只能在Supervisor模式下访问这个寄存器,并且必须只向寄存器的SUPV字段写入一个值c

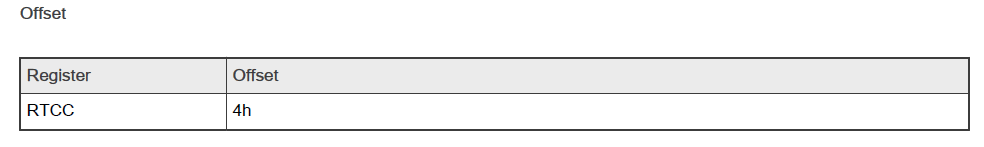

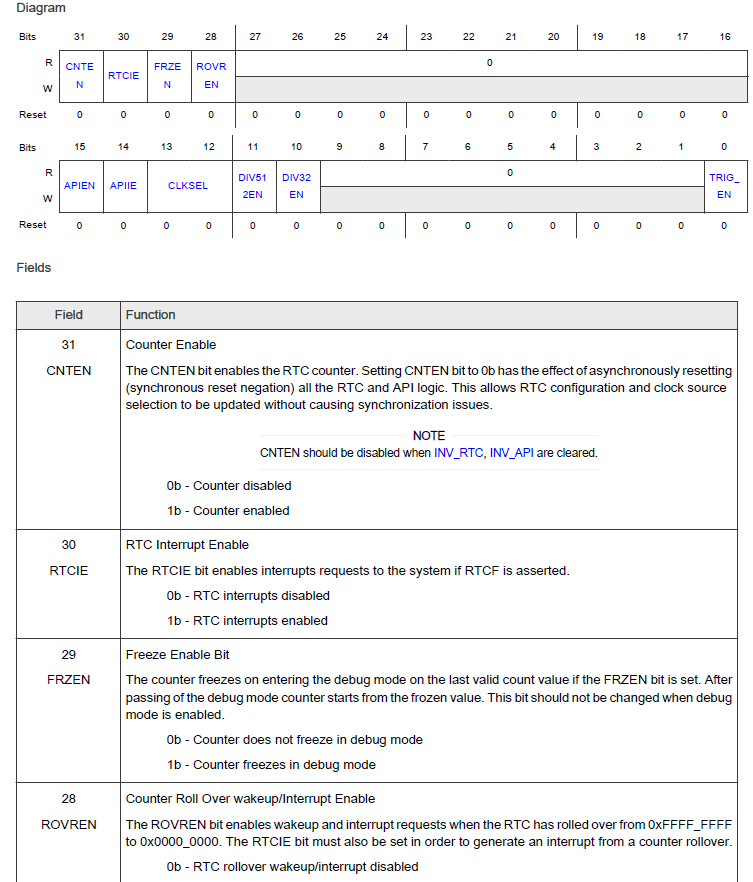

RTC Control register (RTCC)

CNTEN:计数器使能。当INV_RTC, INV_API被清除时,CNTEN应该被禁用。

RTCIE:RTC中断使能

FRZEN:如果设置了FRZEN位,计数器在进入调试模式时冻结最后一个有效计数值。调试模式通过后计数器从冻结值开始。当启用调试模式时,不应更改此位

ROVREN:当RTC从0xFFFF_FFFF滚到0x0000_0000时,ROVREN位启用唤醒和中断请求。还必须设置RTCIE位以便从计数器翻转生成中断。

APIEN:APIEN位使能自主周期中断功能。将此位设置为0b,异步禁用RTC的API唤醒输出。

APIIE:APIIE位允许在断言APIF时中断对系统的请求。

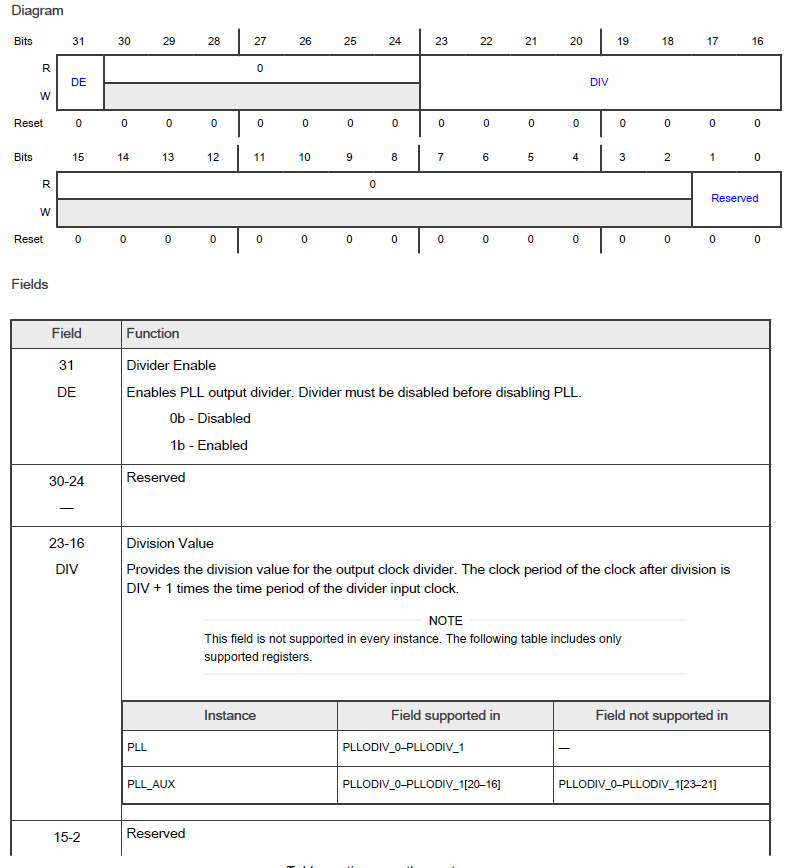

CLKSEL:CLKSEL[1:0]位为RTC选择时钟源。CLKSEL只能在CNTEN为0时更新。在选择振荡器作为RTC时钟源之前,用户应确保振荡器处于启用状态。0:SXOSC_CLK 1:SIRC_CLK 2:FIRC_CLK 3:FXOSC_CLK

DIV512EN:DIV512EN位使能512时钟分压器。只有当CNTEN为0时,才能更新DIV512EN。

DIV32EN:DIV32EN位使能32时钟分压器。只有当CNTEN为0时,才能更新DIV32EN。

TRIG_EN:当设置此位(TRIG_EN)时,将在下一个RTC时钟上取消断言wakeup_api(当总线时钟被禁用时,ACMP需要)。

RTC Status register (RTCS)

如果清除和设置同时发生,W1C优先于RTCF、APIF和ROVRF位的设置。

RTCF:RTCF位表示RTC计数器已经达到与RTCVAL (RTC比较值寄存器)匹配的计数器值。通过向RTCF写入1来清除RTCF。将0写入RTCF没有效果。

INV_RTC:当一个值被写入RTCVAL寄存器并且同步过程正在进行时,这个位返回值1。在此同步期间,任何再次写入RTCVAL寄存器的尝试都将被忽略。只有设置了CNTEN,同步才会完成。

INV_API:当一个值被写入APIVAL寄存器并且同步过程正在进行时,这个位返回值1。在此同步期间,任何再次写入APIVAL寄存器的尝试都将被忽略。只有设置了CNTEN,同步才会完成。

APIF:APIF位表示RTC计数器已达到与API偏移值匹配的计数器值。通过向APIF写入1来清除APIF。将0写入APIF没有效果

ROVRF:ROVRF位表示RTC已经从0xFFFF_FFFF滚到0x0000_0000。通过向ROVRF写入1来清除ROVRF。

RTC Counter register (RTCCNT)

RTCCNT:RTC计数器值,由于时钟同步,RTCCNT值可能代表以前的计数器值。

API Compare value register (APIVAL)

APIVAL偏移位与RTC计数器位进行比较,如果出现匹配,则发起中断/唤醒请求。

APIVAL:APIVAL位被添加到当前计数中以计算偏移量。APIVAL偏移位与RTC计数器位进行比较,如果出现匹配,则断言中断/唤醒请求。

RTC Compare value register (RTCVAL)

RTCVAL位与RTC计数器位进行比较,如果出现匹配,则设置RTCF。RTCVAL的最小值为4。