vivado工程转换到quartus下联合modelsim仿真_内有小猪卖的博客-CSDN博客

这个博客是用单独的modelsim仿真,而下面的流程是使用quartus自带的modelsim-altera仿真。

版本为:quartus ii 13.1 64-bit

以fpga实现数码管和流水灯编码为例。数码管为1时,流水灯状态1234567->1234567;数码管为2时,流水灯状态1234567->7654321。事先建立一个空文件(test_nixie_tube)用来存放工程,注意路径不要有中文。

目录

一、建立工程

1、准备源码和仿真文件

2、新建工程

3、加载源文件

4、选择器件

5、仿真器配置

6、工程信息

二、配置工程

7、设置顶层文件

8、建立仿真文件

9、配置仿真工具路径

三、编译仿真

10、编译

11、仿真

参考文章

一、建立工程

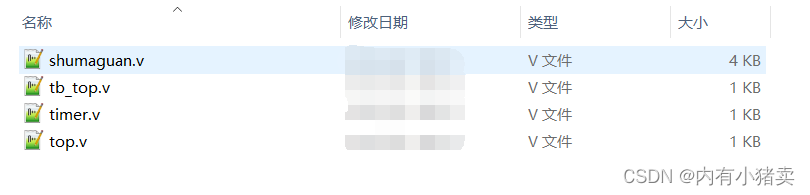

1、准备源码和仿真文件

源文件 + 仿真文件(tb_top)

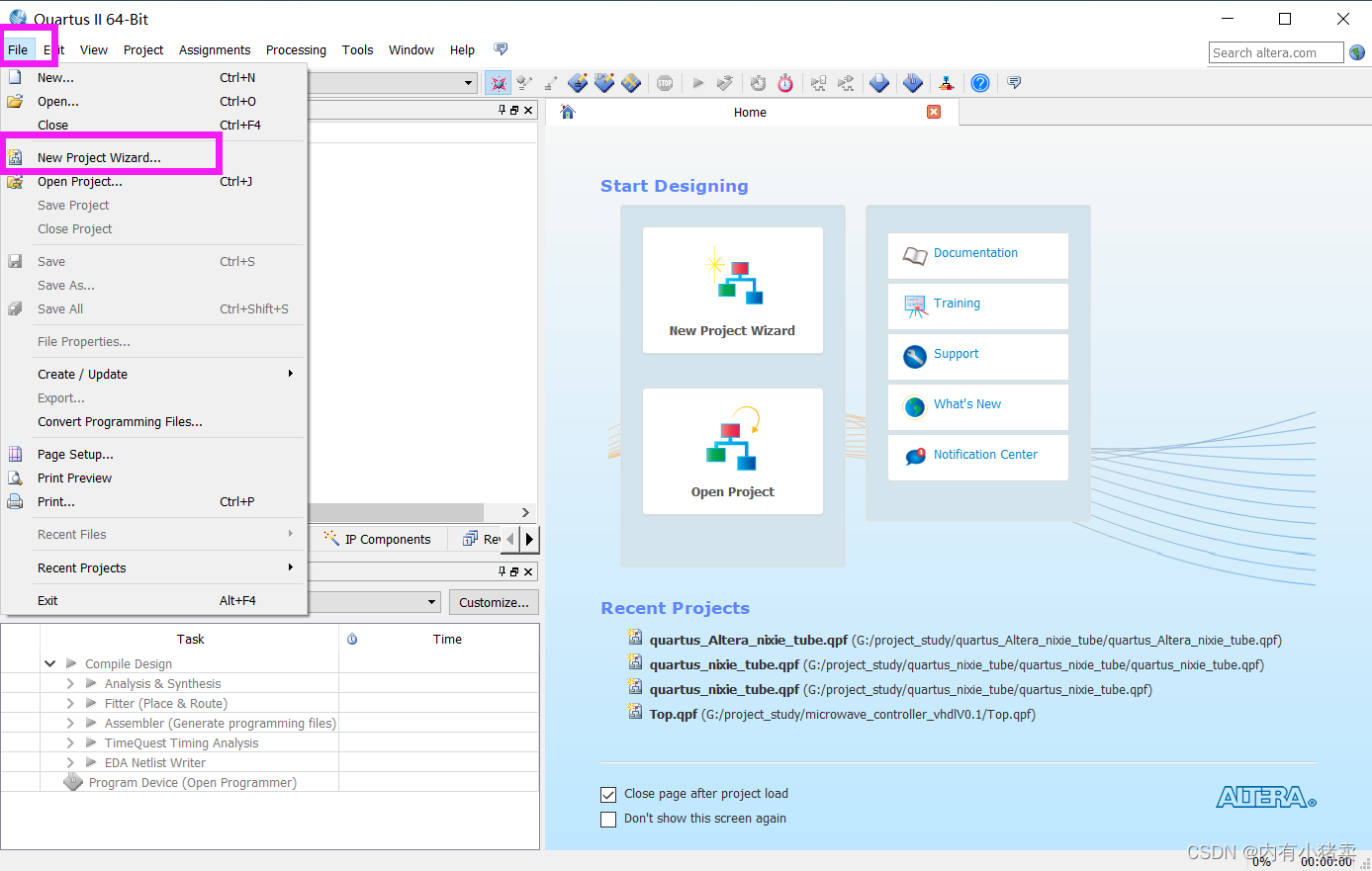

2、新建工程

2.1 打开quartus II,点击file ---> New Project Wizard

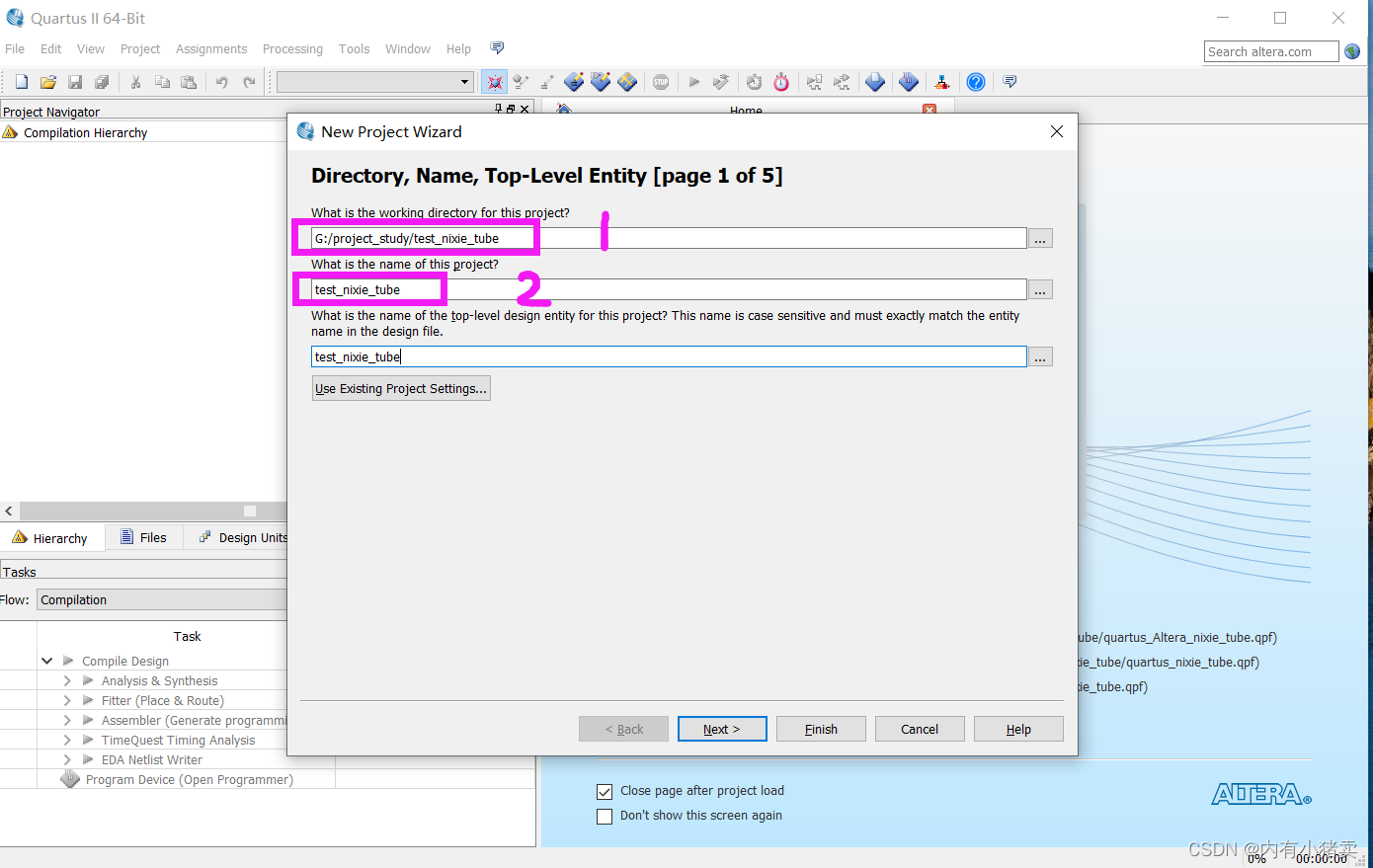

1是我们事先建好的工程文件,2是工程名。为了方便这俩名字可以设置相同。

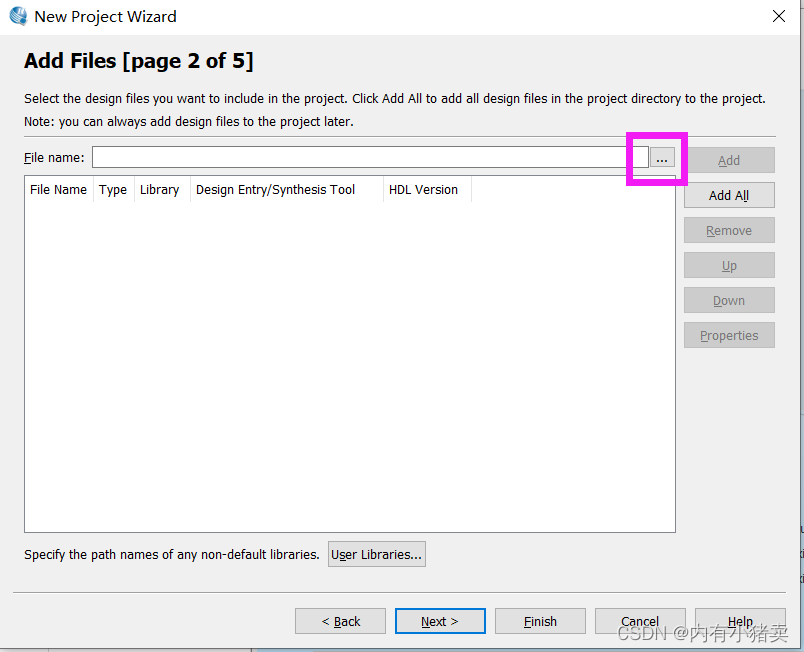

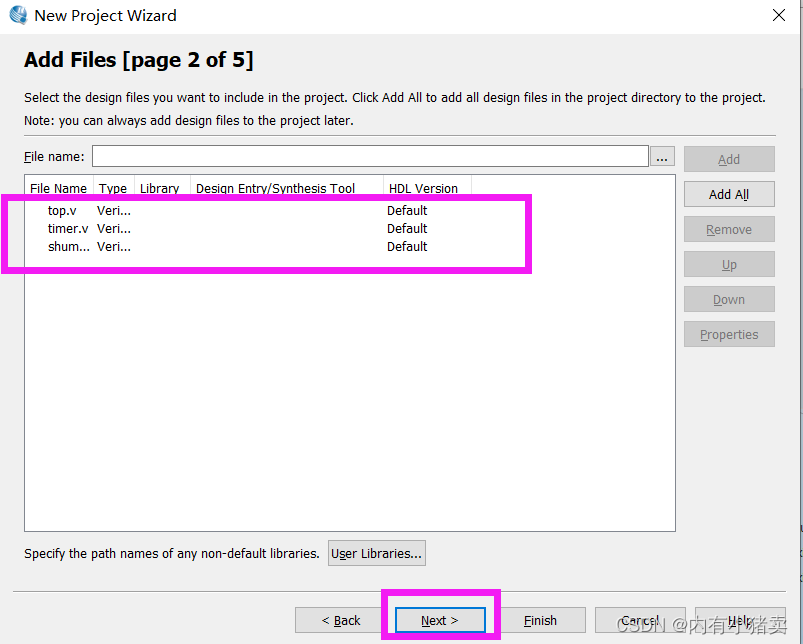

3、加载源文件

上一步配置好了点 next,然后点“...”选择我们写好的源文件。

添加了3个源文件后,点击“next”。

4、选择器件

器件这块按需求选择。

5、仿真器配置

仿真器选择Modelsim-Altera,格式选择Verilog HDL。下面点击"next"

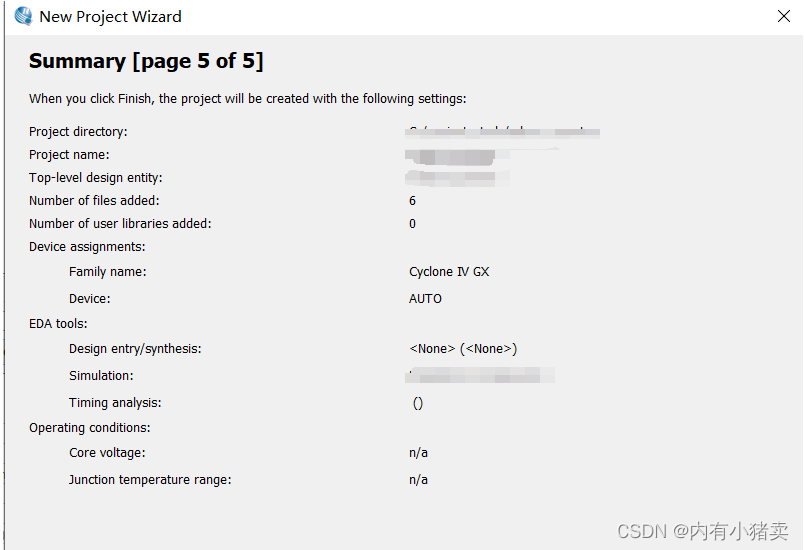

6、工程信息

下一个窗口是工程信息,直接点击“finish”。

到此工程就建好了。

二、配置工程

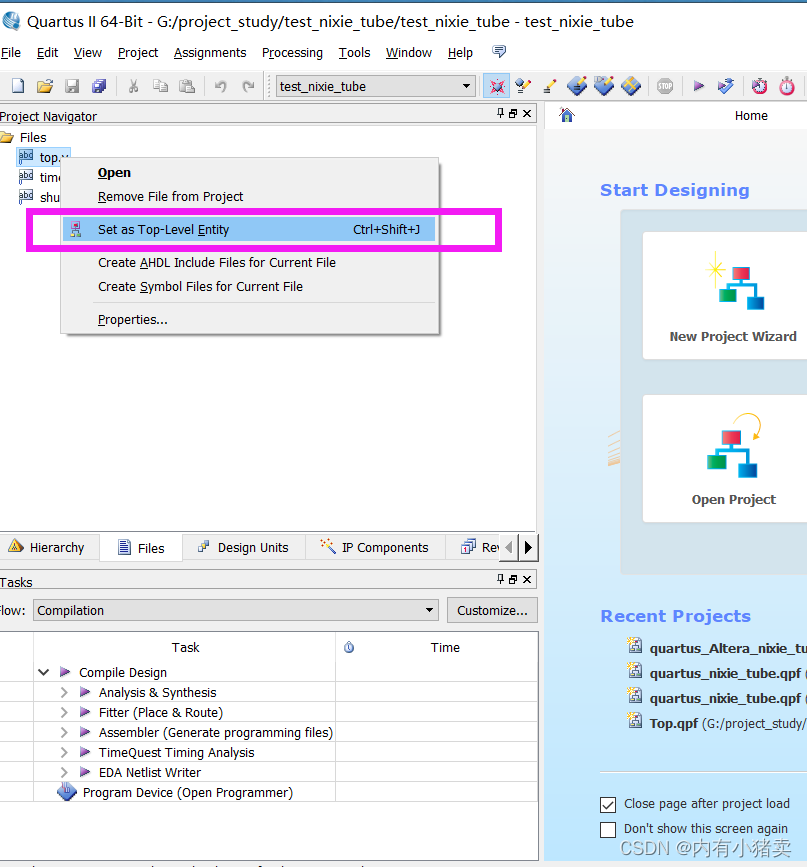

7、设置顶层文件

先设置顶层top,告诉编译器哪个是顶层文件,否则会报错如下。

12007 Top-level design entity "your_project" is undefined

Quartus II 64-Bit Analysis & synthesis was unsuccessful. 1 error,0 warnings

293001 Quartus II Full compilation was unsuccessful. 3 errors,0 warnings

然后点这个三角,编译文件。

编译成功

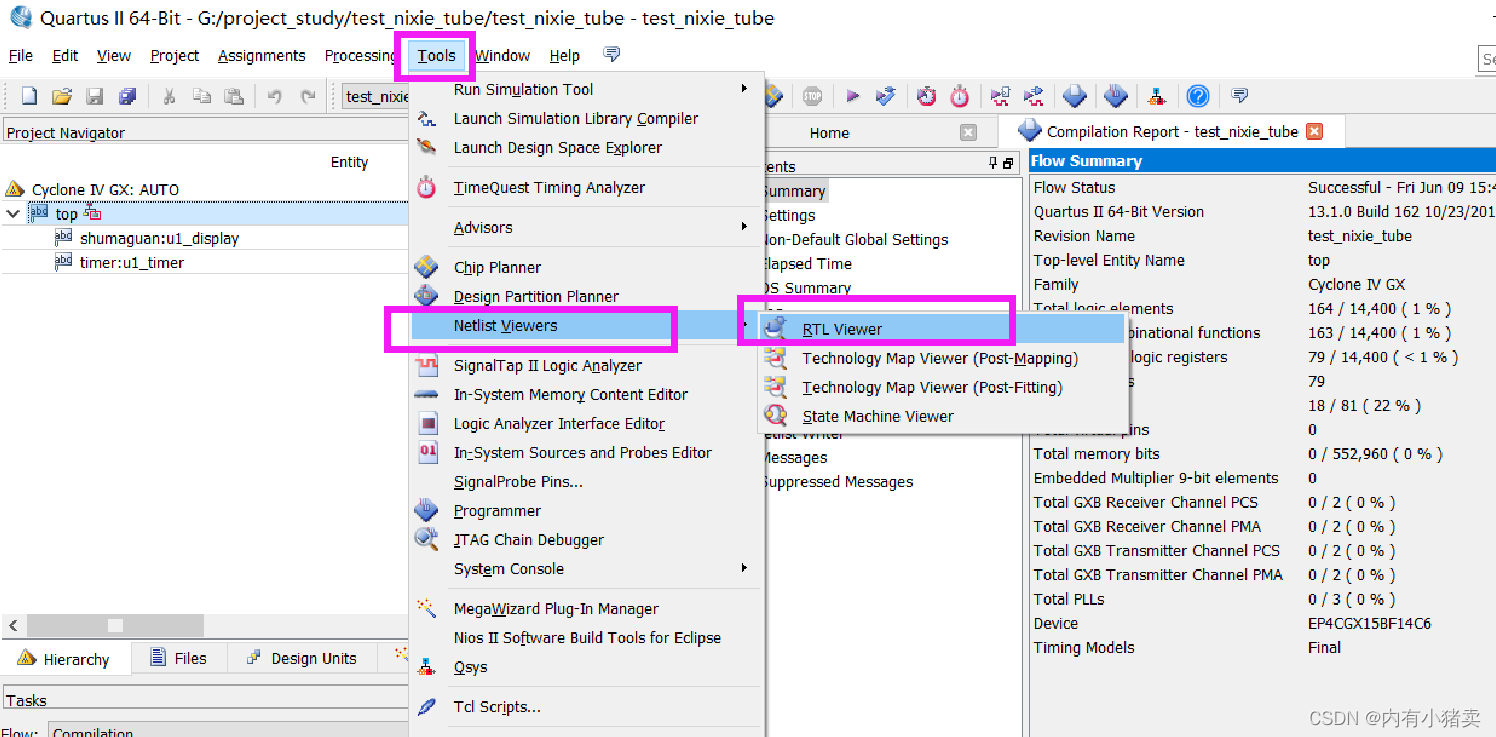

查看rtl图(选做)

就可以看到了。

8、建立仿真文件

我们已经有一个仿真文件了,可以直接选仿真文件加载。因为我准备的基于vivado平台的,稍微有点不一样。比如quartus的仿真文件是.vt,而vivado的仿真文件是.v,这俩都是基于vivado平台的。

为了保险起见,我们还是新建一个仿真文件,然后把之前的仿真内容复制过去。

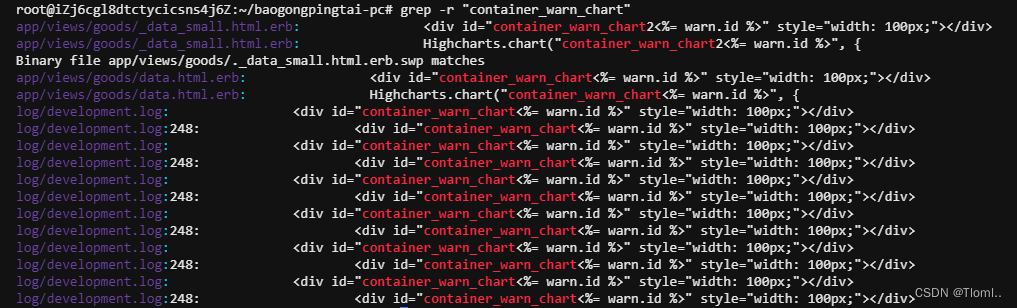

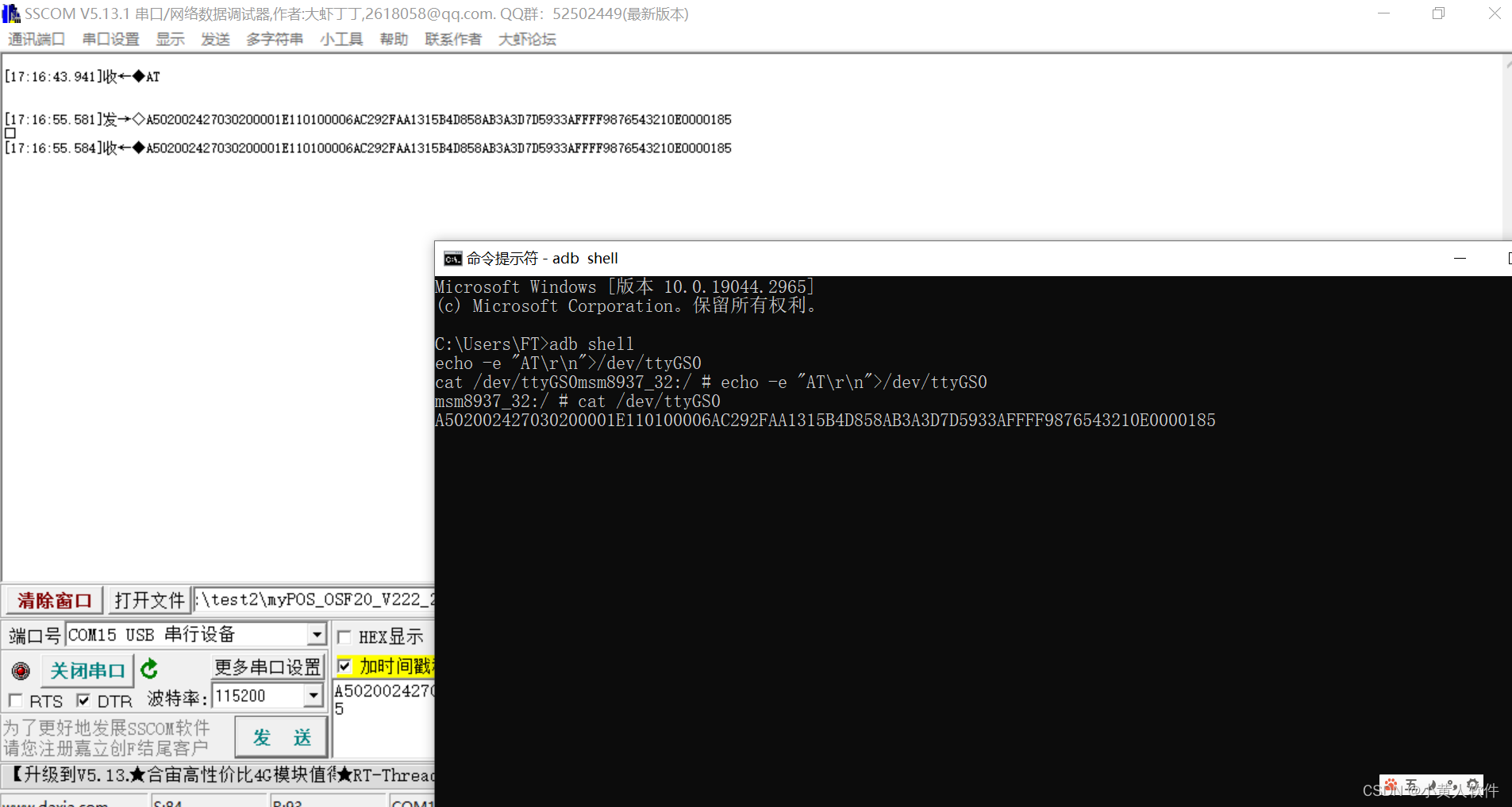

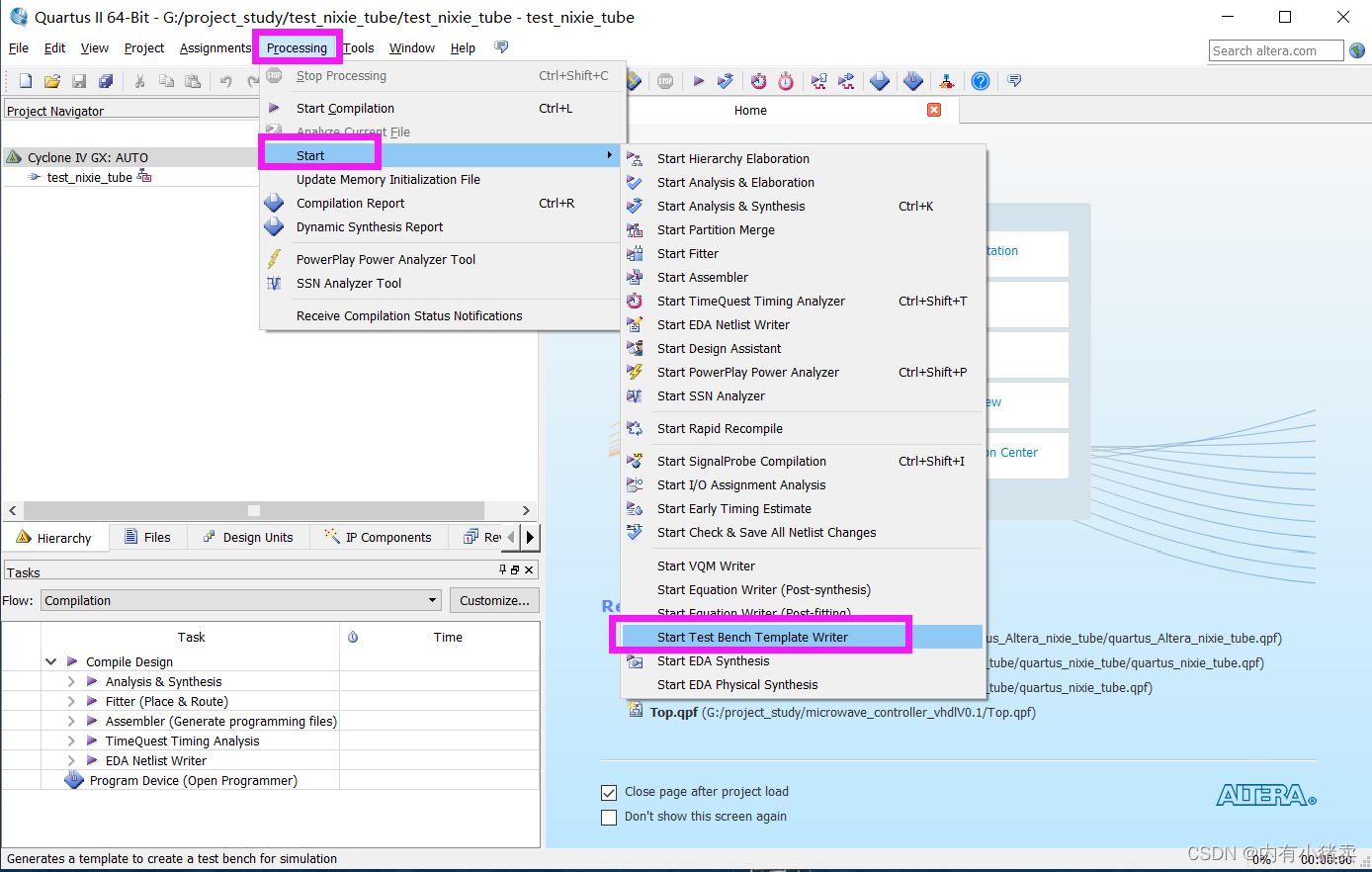

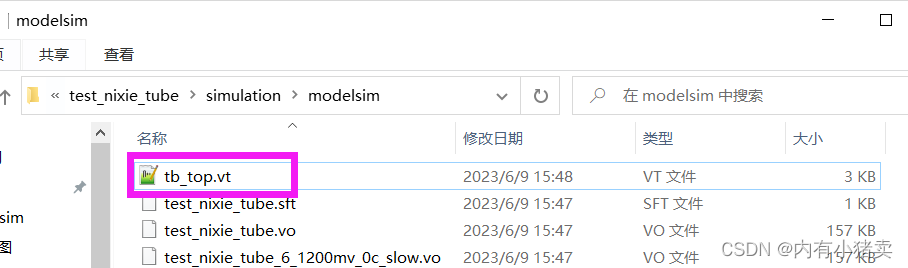

点击processing -----> start ------>start Test Bench Template Writer 新建一个仿真文件,我们去这个工程路径的simulation---->modelsim文件夹下找到.vt文件,然后编辑它。

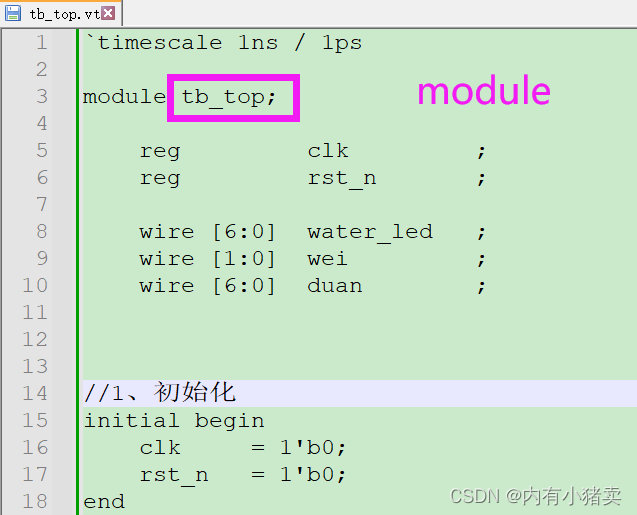

为了不和源码的顶层文件重名,将vt文件名改成tb_top;并将之前准备好的仿真文件内容复制过来。

为了方便,仿真文件的module名也改成tb_top,然后保存。

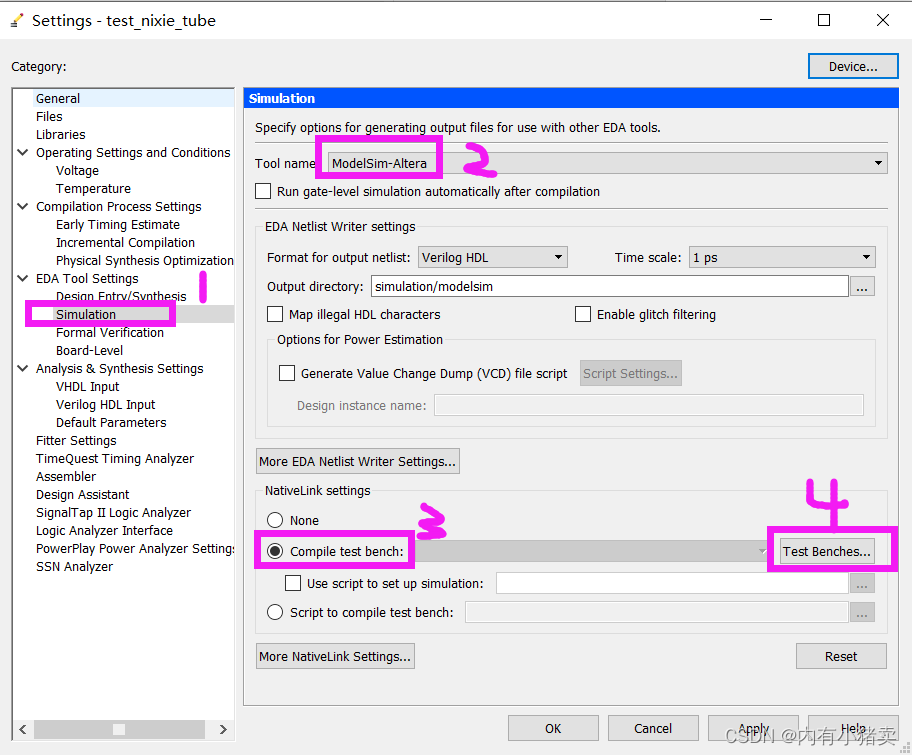

9、配置仿真工具路径

打开配置菜单,找到 project Navigator ----> top 右键点击setting

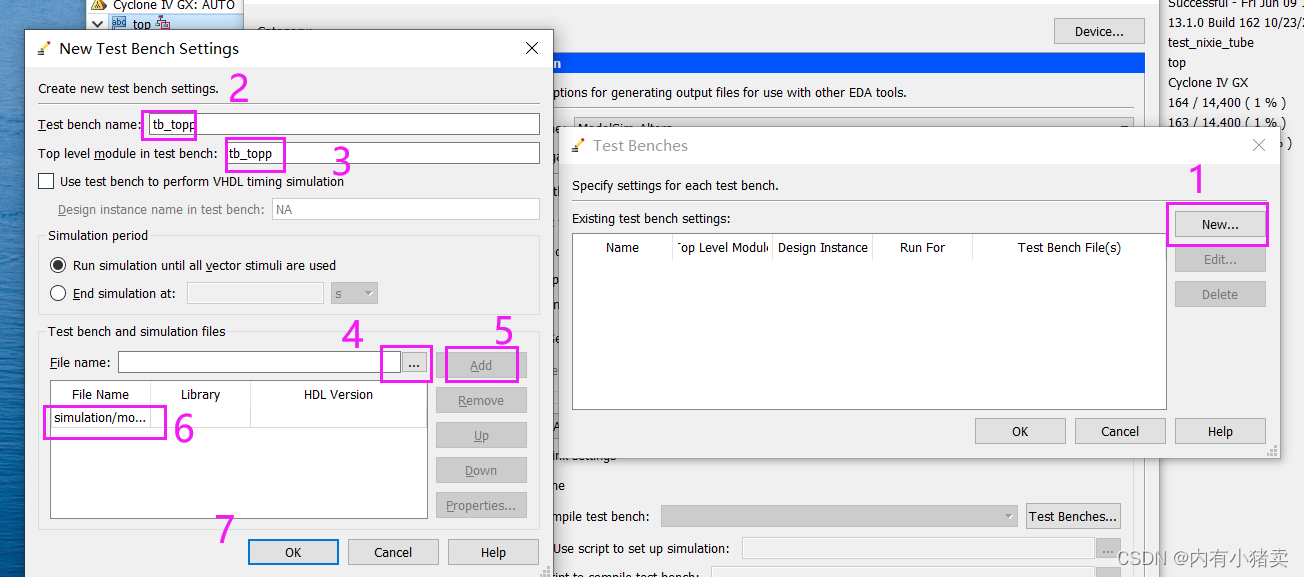

然后进入配置tb文件

数字1:新建仿真信息

数字2:tb文件名

数字3:tb文件中module名,所以这俩设置一样就很方便。

数字4:选择仿真文件

数字5:点击add 添加文件

数字6:表示加载了tb文件,然后点击ok

后面一路点击ok,大概3个ok。

三、编译仿真

10、编译

加载仿真文件后,再编译一次。

编译成功之后依次点击就行。

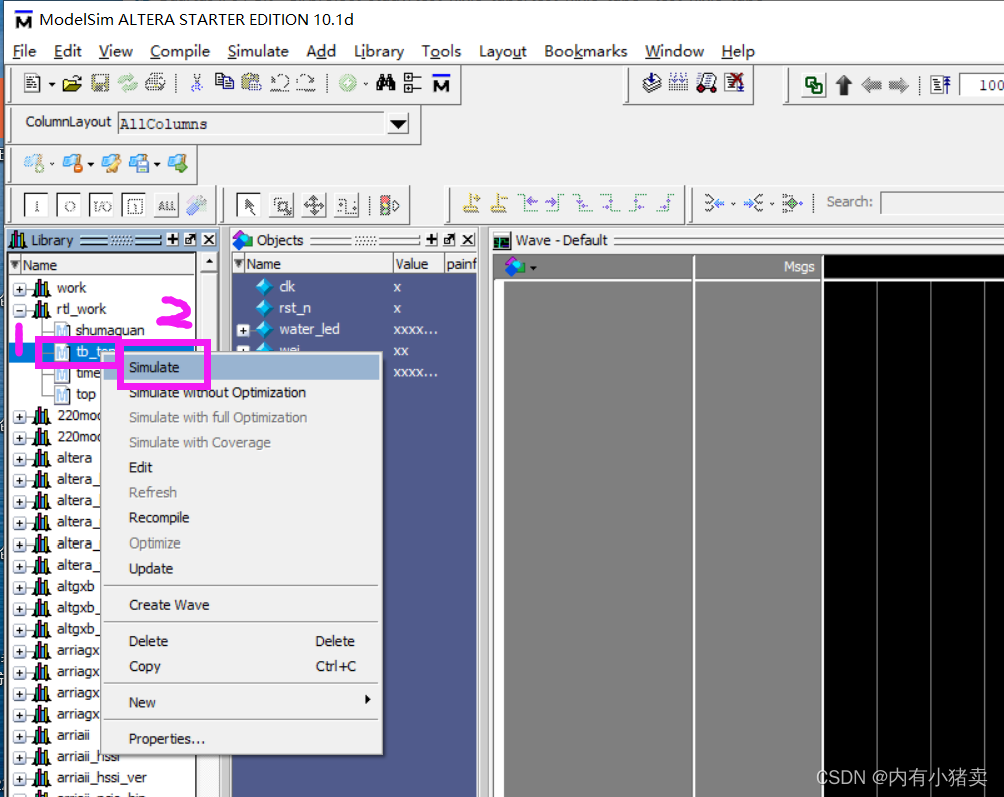

11、仿真

如果没有直接弹出来,找到仿真文件tb_top,然后点simulate。

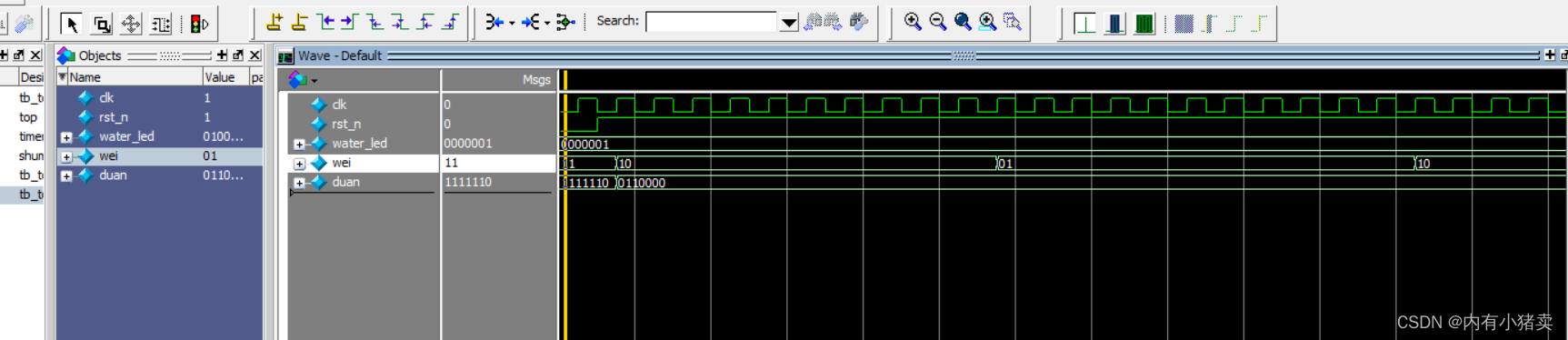

6、先执行数字6,在深蓝色部分,把端口拖拽放到右侧灰色地方

1、重新运行程序restart

2、点击run,运行仿真波形

3、comtinue run:

让仿真波形继续跑,因为会跑一段就停止,如果想让波形继续跑,就需要点击。

4、re-run :让波形重新跑

5、取消编译和仿真

5右边的stop按钮是停止仿真

正确显示波形

参考文章

Quartus同Modelsim的联合仿真_quartus 18.0与modelsim或modelsim altera进行波形联合仿真_1个程序源的博客-CSDN博客

【FPGA】TestBench中关于@eachvec_xiao_-_zhu的博客-CSDN博客

https://www.cnblogs.com/lsjjob/p/5127974.html