GS2972视频输出调试

- 一、外同步模式

- 1.1 GS2972的硬件初始化

- 1.2 GS2972的驱动时序

- 1.3 GS2972的驱动RTL代码

- 1.4 GS2972输出彩条

- 1.5 GS2972驱动易出bug

- 二、数据内嵌同步模式

- 2.1 GS2972的硬件初始化

- 2.2 GS2972的驱动时序

- 2.3 GS2972的驱动RTL代码

- 2.4 GS2972输出彩条

- 2.5 GS2972驱动易出bug

一、外同步模式

1.1 GS2972的硬件初始化

GS2972是HD-SDI/3G-SDI视频、音频串化器。其使用非常简单,但是要想把该芯片驱动起来,真心不容易。需要了解相关视频标准、传输标准、显示标准,协议较多,版本较多,彻底了解并非一件简单的事情。笔者经过大量阅读,将驱动GS2972过程总结如下。后续,作者会陆续记录视频相关标准的学习。

GS2972的使用简单地说就是FPGA向GS2972写入行同步、场同步、数据使能,并根据SMPTE292标准写入数据流即可。对就这么简单,说起来容易,可是真正要操作起来,并非简单事情。

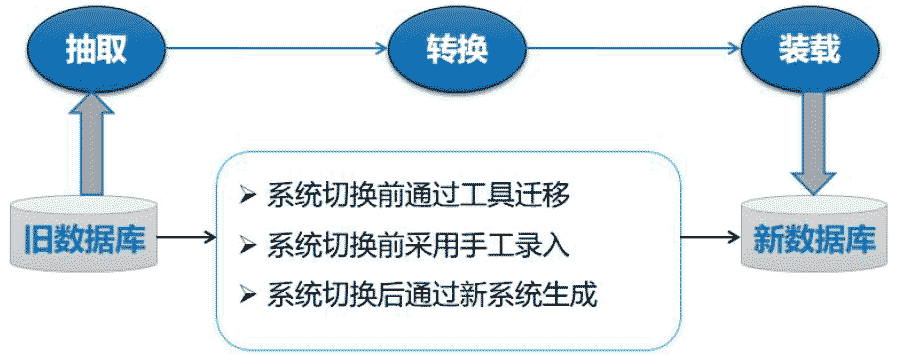

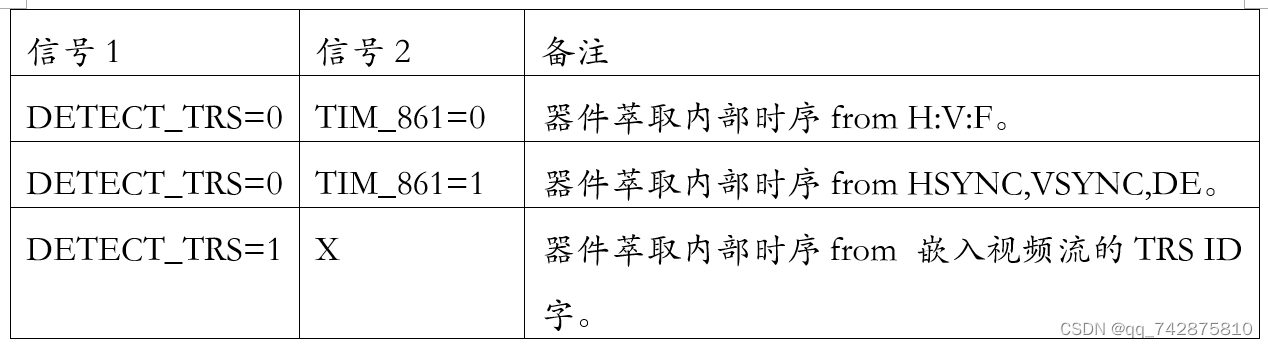

GS2972初始化为SMPTE模式,在SMPTE模式下芯片有两种视频数据组织形式,一种是芯片根据所给的视频数据自动检测并生成行场同步信号,还有一种是需要将写好的行场同步信号传给芯片。当DETECT_TRS位为高电平时,芯片从视频数据中检测生成行同步信号,场同步信号和数据使能信号。当DETECT_TRS位为低电平时需要通过H/H_SYNC、V/V_SYNC、F/DE管脚给芯片提供这三个信号。

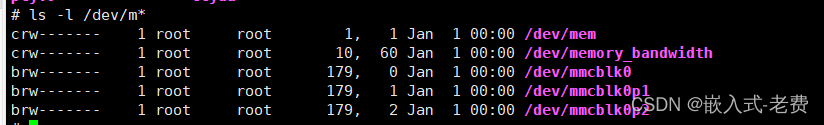

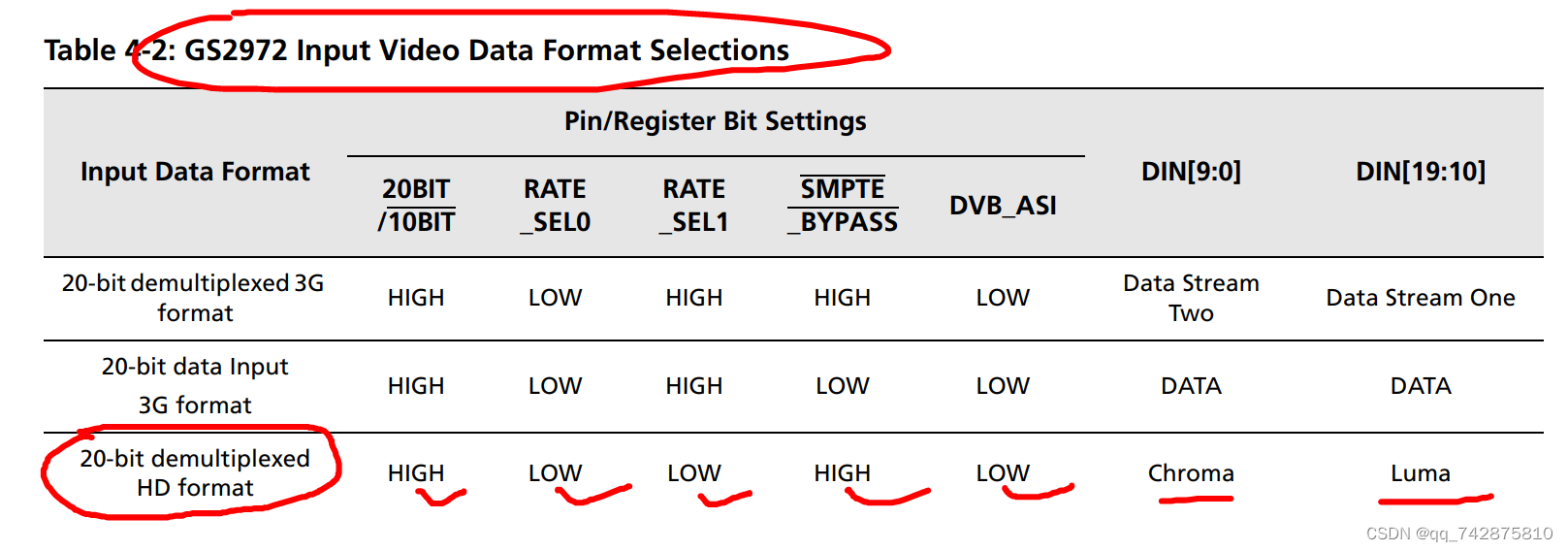

我们本次使用20bit非复用模式。硬件引脚上下拉如下图所示(下表第一行)

DETECT_TRS信号和TIM_861信号,笔者经过阅读数据手册,总结如下:

本次视频传输,我们使用CEA-861时序驱动VSYNC 、SYNC 、DE信号控制显示器显示,输出1920*1080@50Hz视频信号。

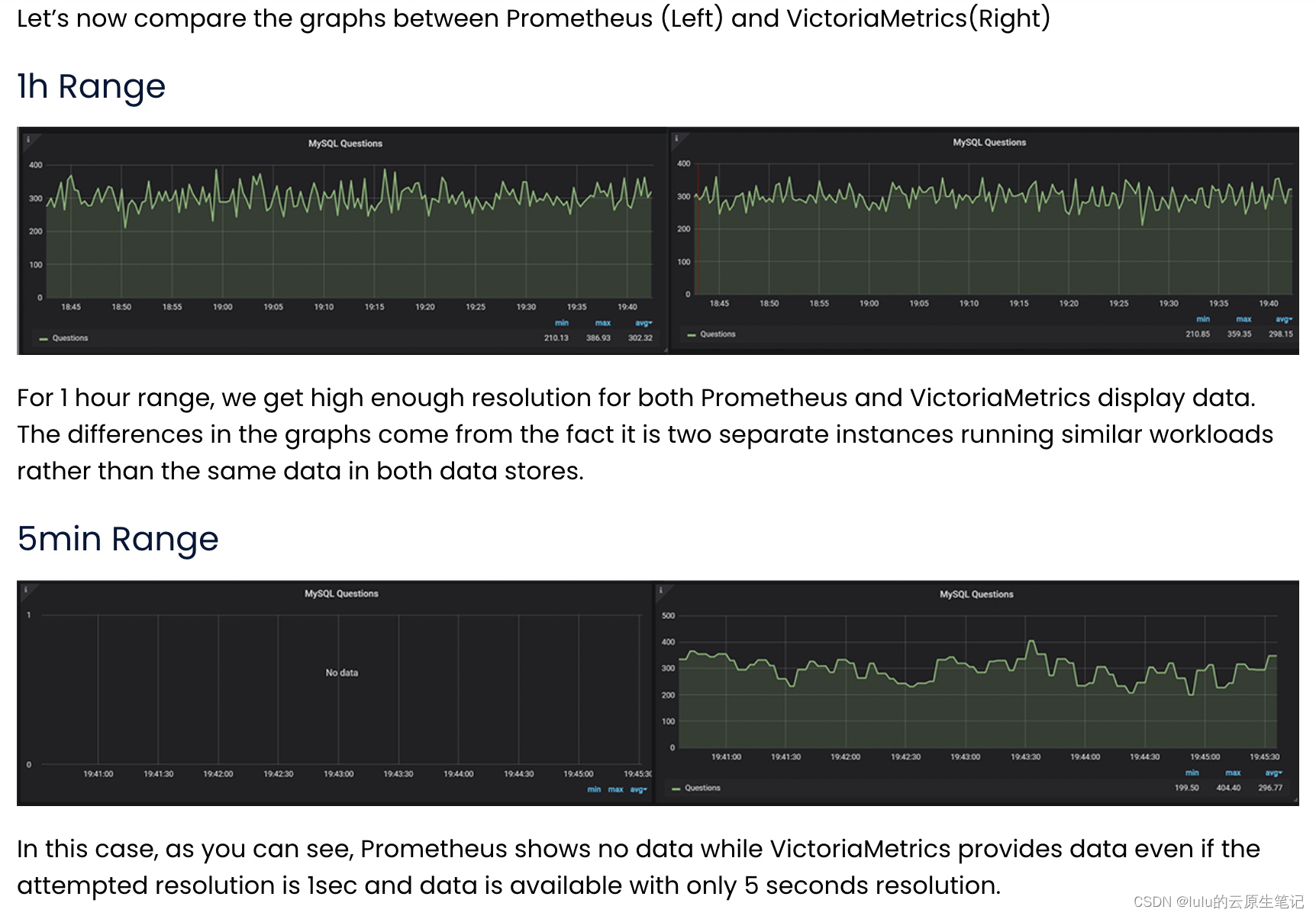

1.2 GS2972的驱动时序

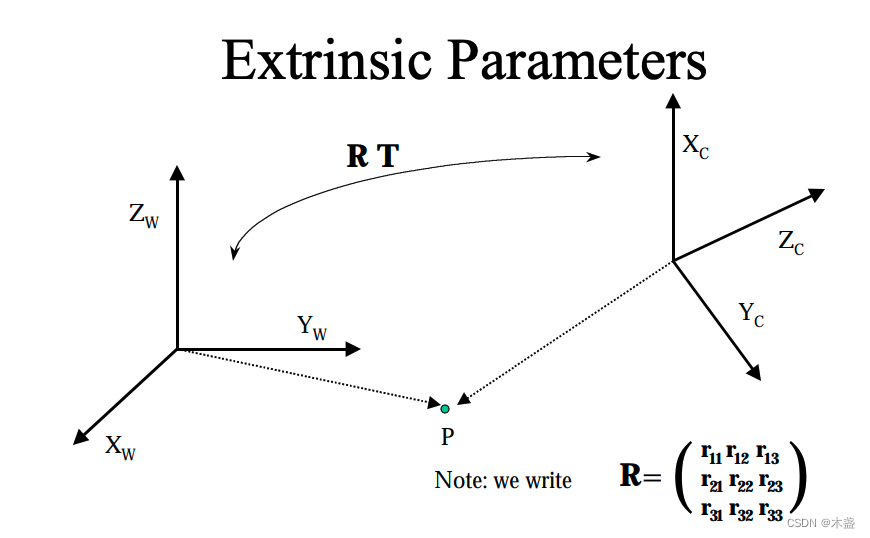

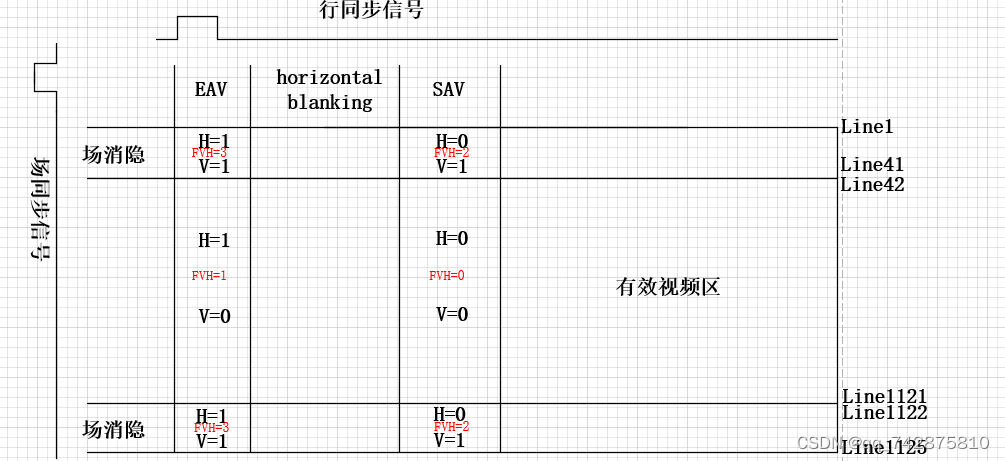

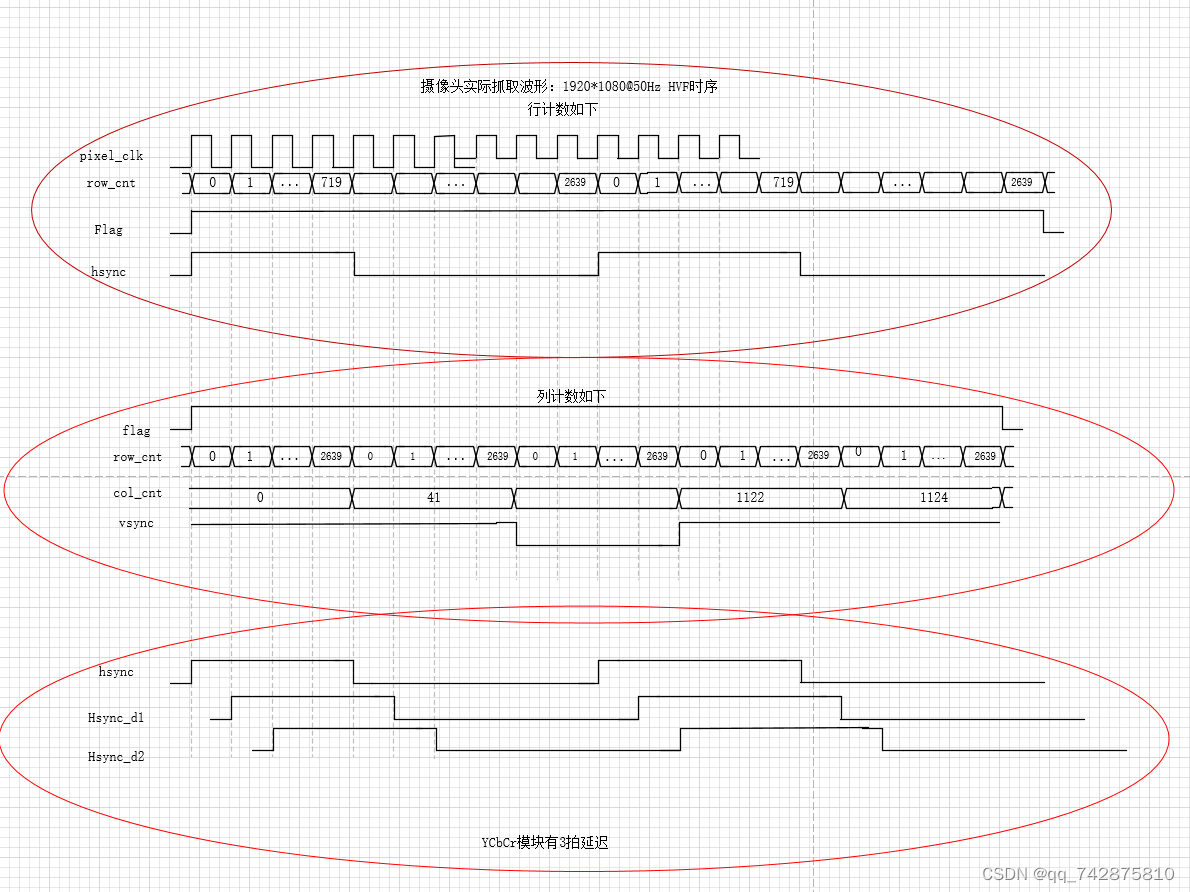

读者需要对这个时序彻底理解,脑子里必须有下面这幅图,否则,是理解不了上述时序的。

1.结合上下时序图可知,line1-line41为场消隐,line1122-line1125为场消隐,共45行场消隐。

2.在消隐期间data_enable为低,在有效像素期间,data_enalbe为高。

3.此处的行场同步并非,我理解的在行同步时,行同步拉高,在场同步时场同步拉高。而是拉高固定的时钟周期。

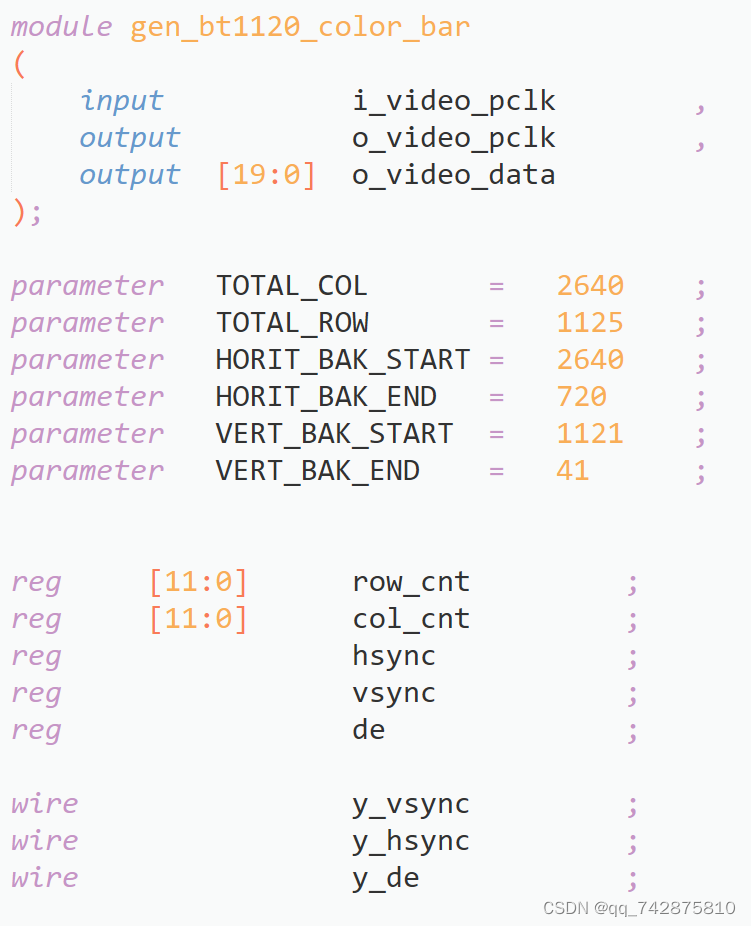

1.3 GS2972的驱动RTL代码

1.4 GS2972输出彩条

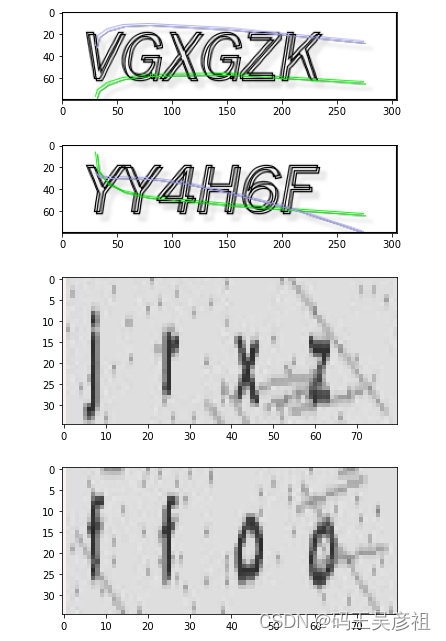

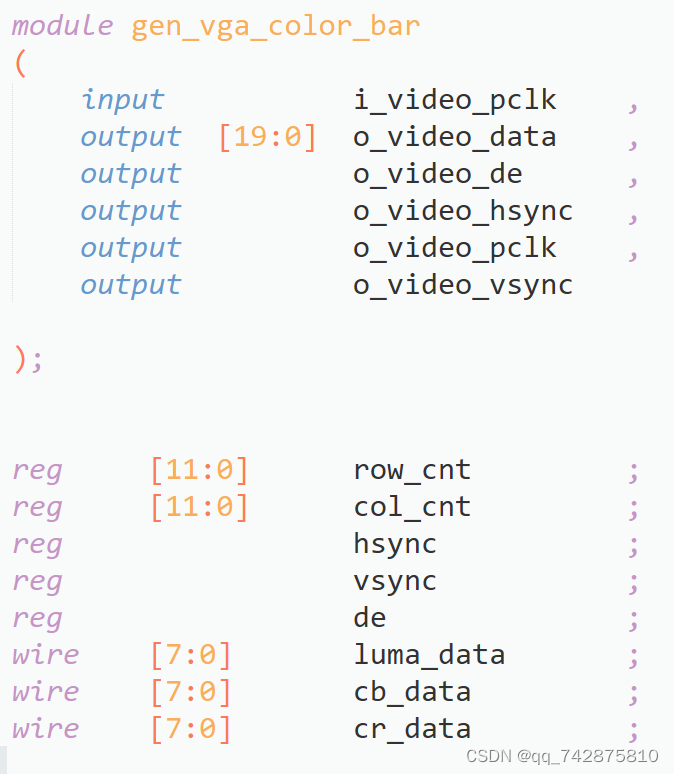

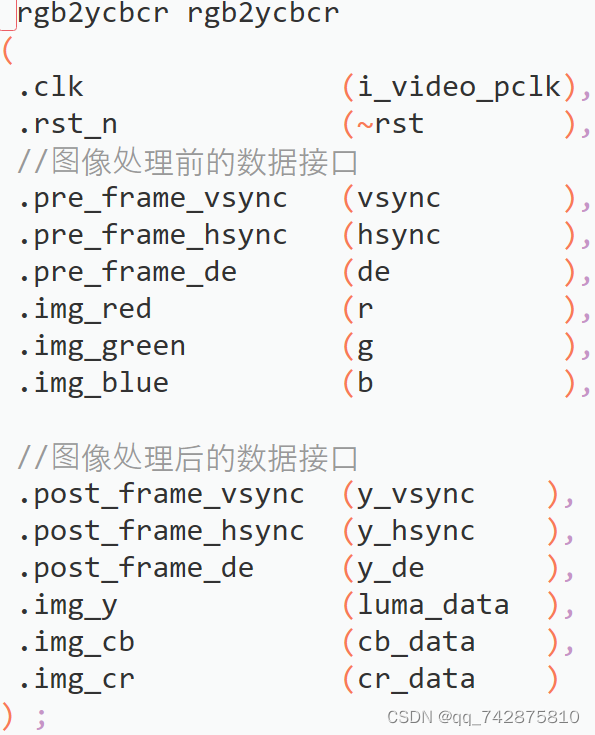

在输出彩条时需要将RGB888信号转换为YUV信号,输出4:2:2视频格式。转换有xilinx的IP也可以自己书写代码。

xilinx IP:RGB to YCbCr color space

自己写转换代码如下:

1.5 GS2972驱动易出bug

- 笔者在第一次驱动GS2972时,一开始搞不懂CEA-861驱动时序,折腾了好几天,最后阅读大量文章后才理解了。

- 写错驱动时序后,由于SDI是YUV视频格式,笔者直接将相机进来的视频Y=3’hff,Cb=3’b000,Cr=3’b000,显示满屏绿色。抓取了CEA-861时序,确认与我书写时序一致,增加rgb2ycbcr转换模块。

- 笔者第一次写的rgb2ycbcr代码如下。

assign img_y = de ? img_y1 : 8’d0;

assign img_cb = de ? img_cb : 8’d0;

assign img_cr = de ? img_cr : 8’d0;

结果输出彩条闪一下就黑屏了。最后改为下面代码正常。

assign img_y = img_y1 ;

assign img_cb = img_cb ;

assign img_cr = img_cr ;

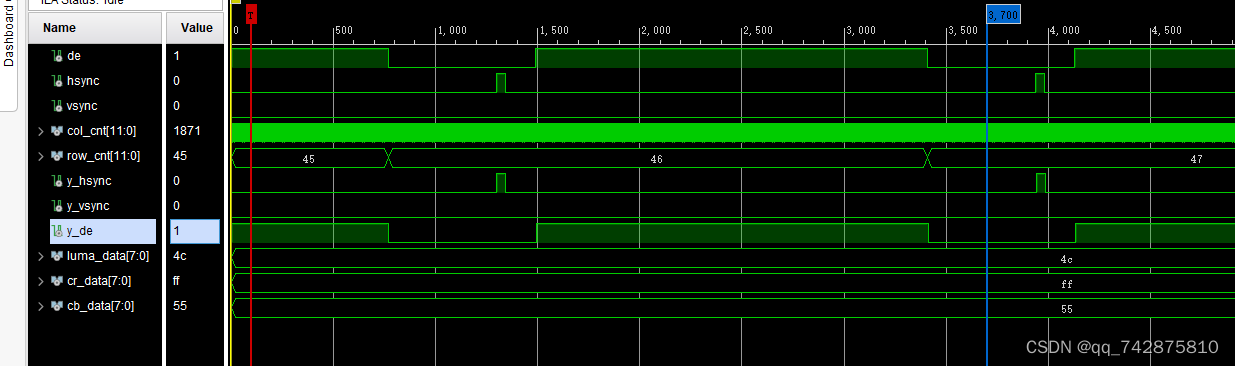

由此可以断定,无论是否数据有效,不能随意给YCbCr数据。正确的波形如下,即在DE为0期间,Y数据和CbCr数据依然有效,不能给0。

由此可以看到,在DE为低电平期间,YCbCr数据也不能随意给,笔者在DE为低电平期间给0,结果输出彩条时有时无。

二、数据内嵌同步模式

2.1 GS2972的硬件初始化

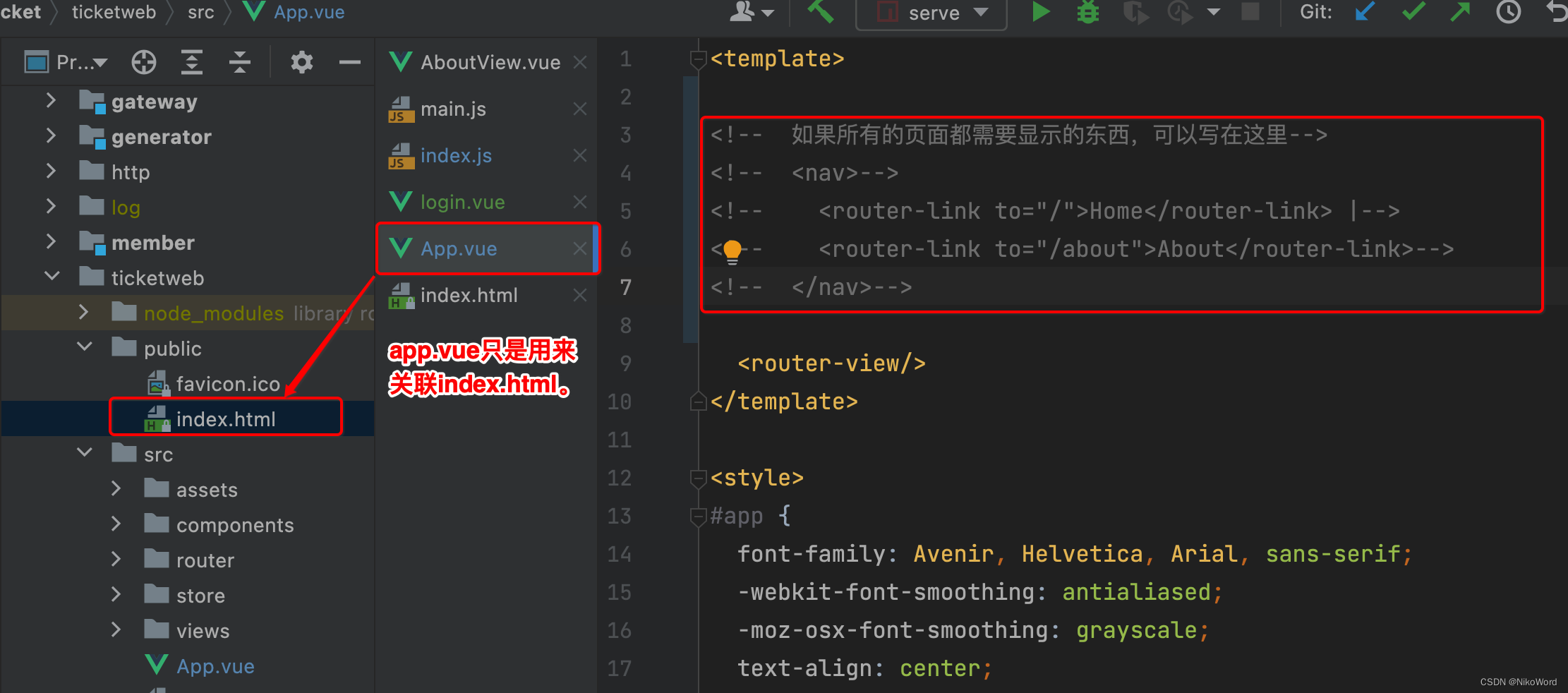

初始化硬件依然为20bit非复用模式,与外同步不同的是使用数据内嵌同步,将TIM_861设置为低电平。

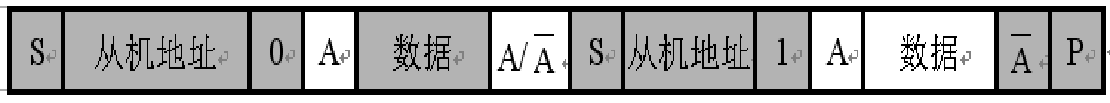

2.2 GS2972的驱动时序

2.3 GS2972的驱动RTL代码

由接口代码可以看出,同步信号已经做到数据内部了。

2.4 GS2972输出彩条

2.5 GS2972驱动易出bug

笔者在第一次写代码的时候将消隐区的数据给0,导致输出彩条出现闪烁现象,即一会是黑屏一会是彩条,最后将消隐区的数据改为YCbCr数据后正确。