基本分页存储管理

背景

固定分区带来的是内部内存碎片难以利用

而动态分配带来的外部内存碎片难以利用

而基本分页存储管理解决了这个问题,将一个进程分散地装入不同分区,避免了紧凑的处理

思想

将一个进程(43MB)装入内存,一个分页大小为10MB,则分成5份即可,通过减少分页大小,减少内部碎片

概念梳理

内存空间分为一个个大小相等的分区

分区 = 页框 = 页帧 = 内存块 = 物理块

页框号 = 内存块号 = 页帧号 = 物理块号

用户进程的地址空间分为一个个与页框等大的区域,称为页或页面,每个页也有页号

操作系统以页框为单位为各个进程分配内存空间,进程每个页面分别放入一个页框中,各个页面不必按照顺序存放

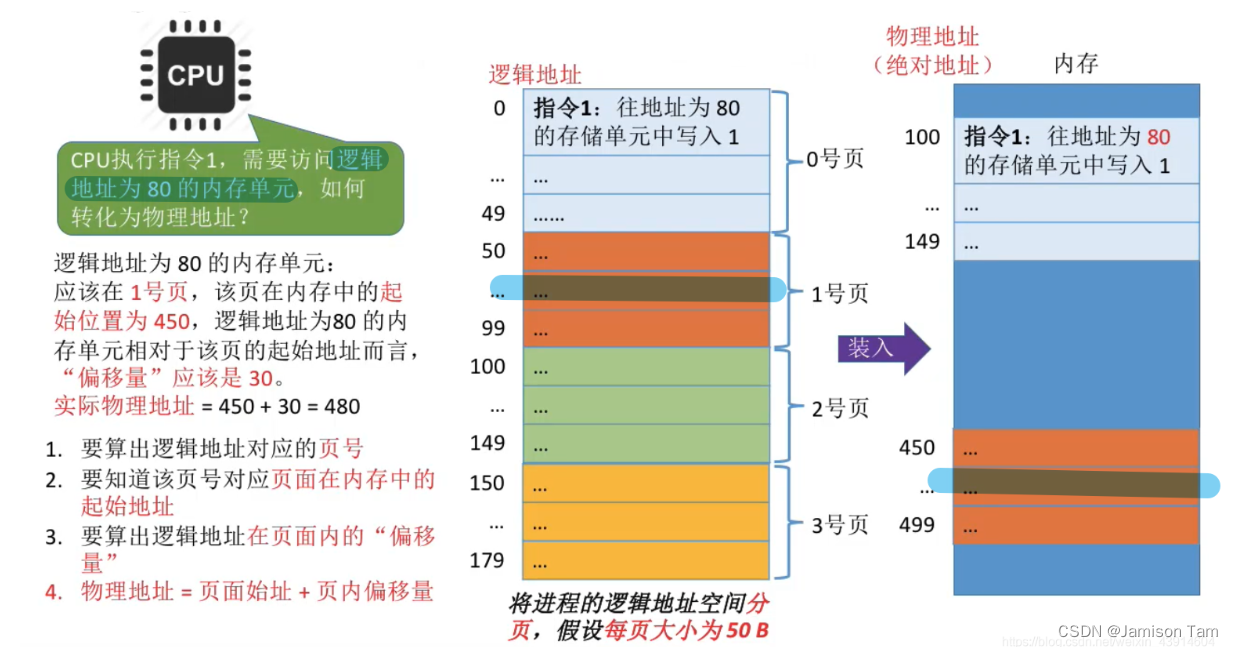

地址转换

程序内指令指向的地址都是逻辑地址,当执行时需要转换为物理地址,根据页号和逻辑地址,推算出内存单元在分页内的逻辑地址,再加上对应分页的起始地址的物理地址即可

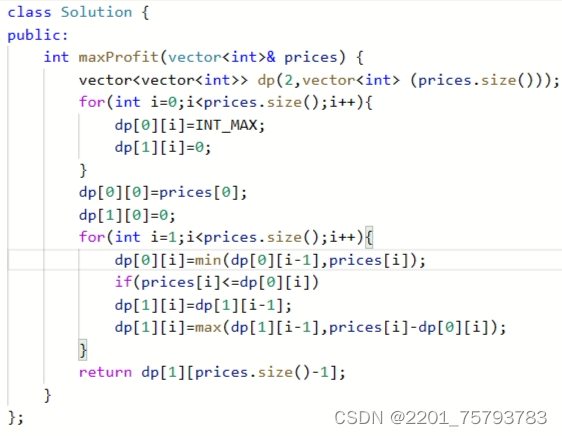

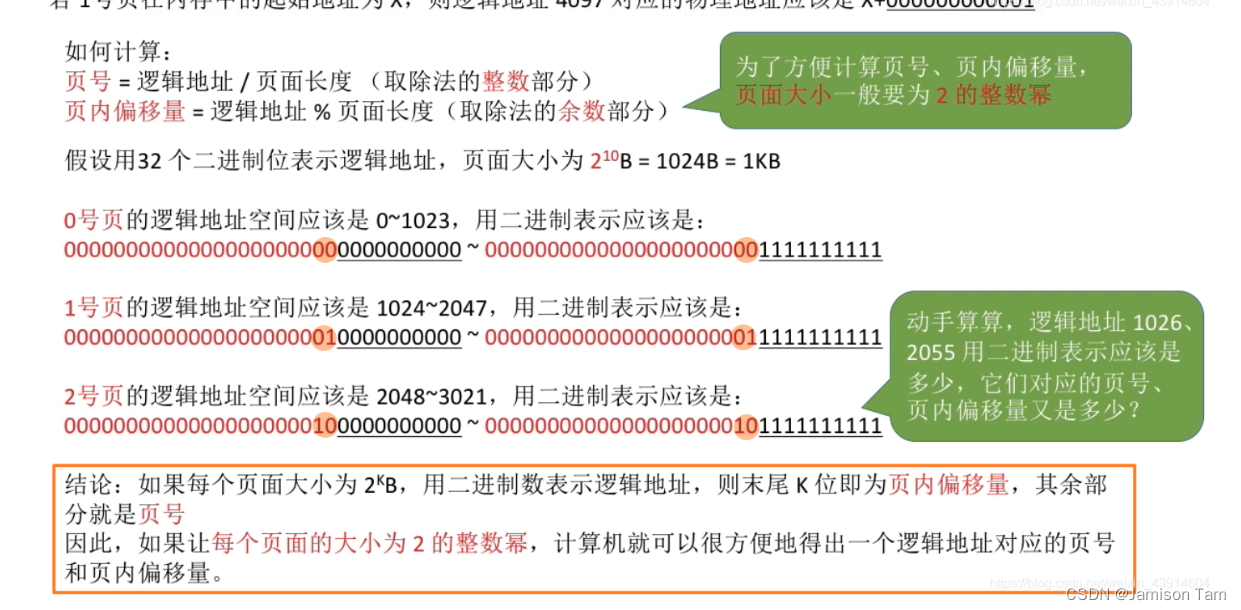

页号 = 逻辑地址 / 页面长度

页内偏移量 = 逻辑地址 % 页面长度

分页存储的逻辑结构

页号+页内偏移量

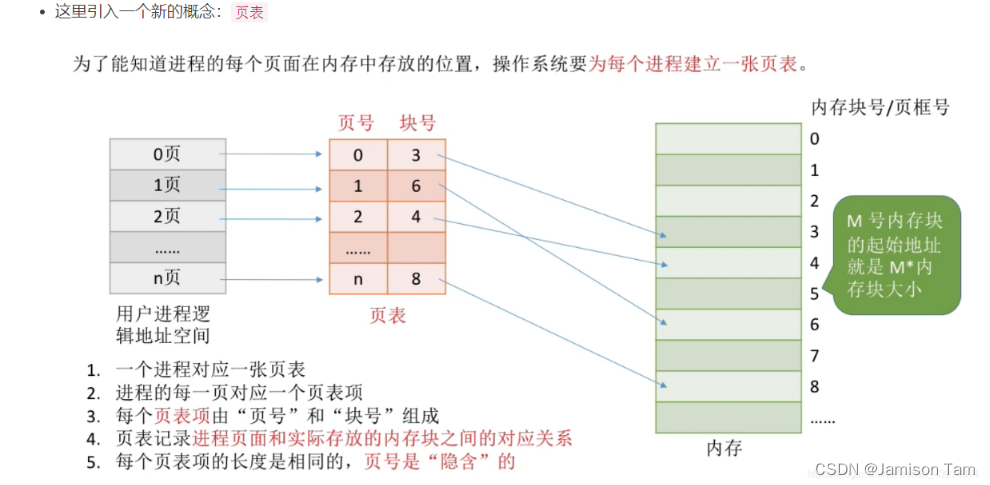

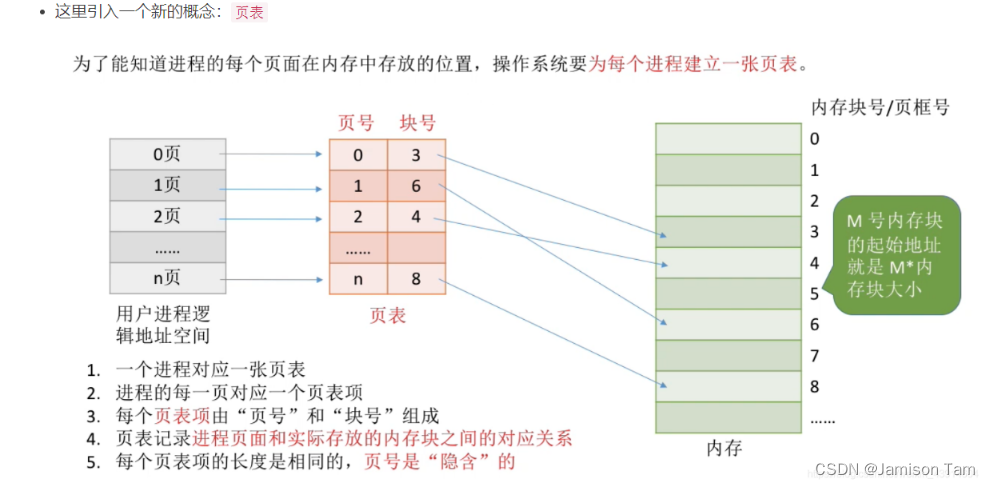

系统为了得知进程的每个页面在内存中的存放位置,建立一张页表

一个进程对应一张页表

进程的每一页对应一个页表项

每个页表项由页号和内存块号组成

页表项长度相同,页号隐含

页表寄存器

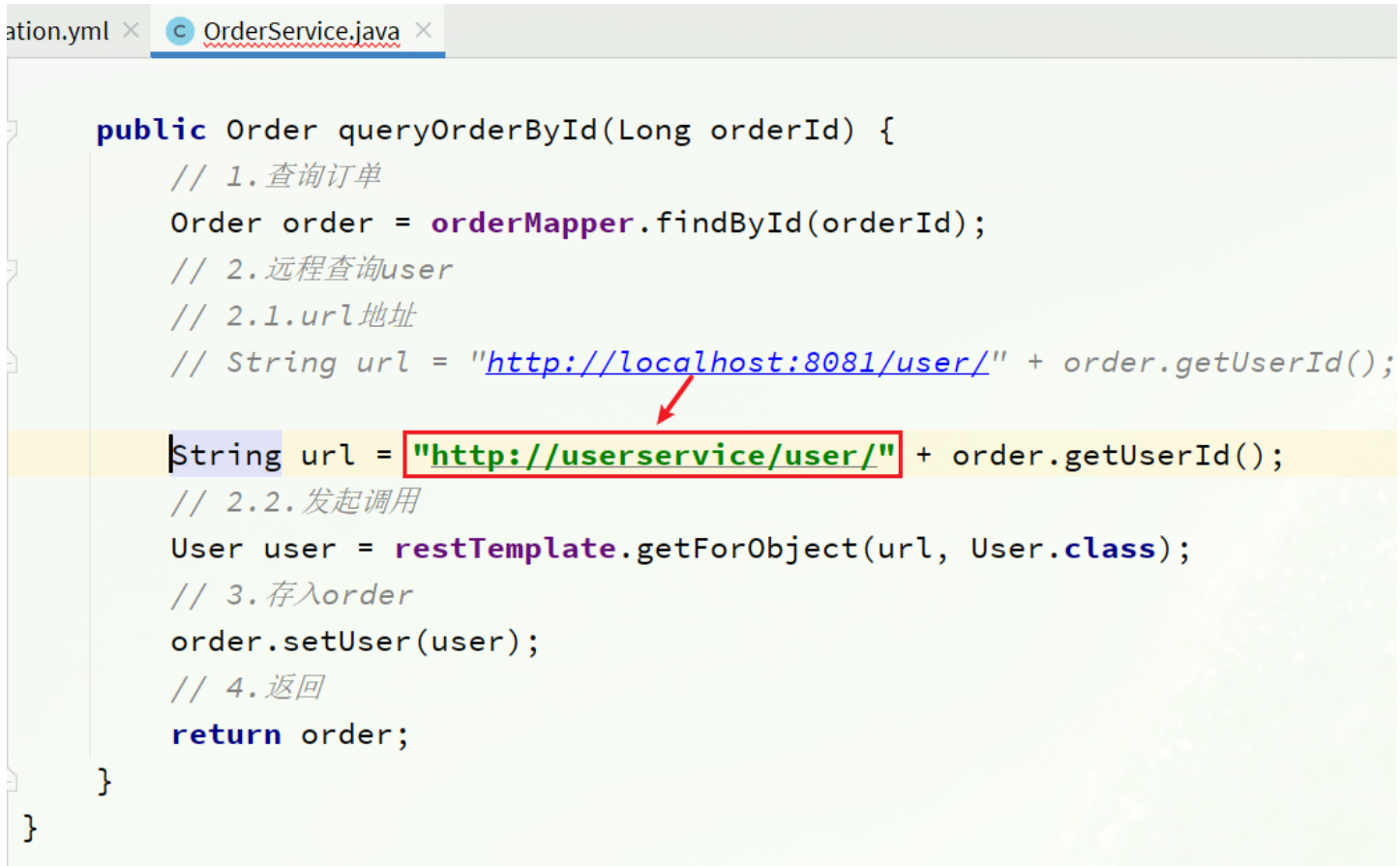

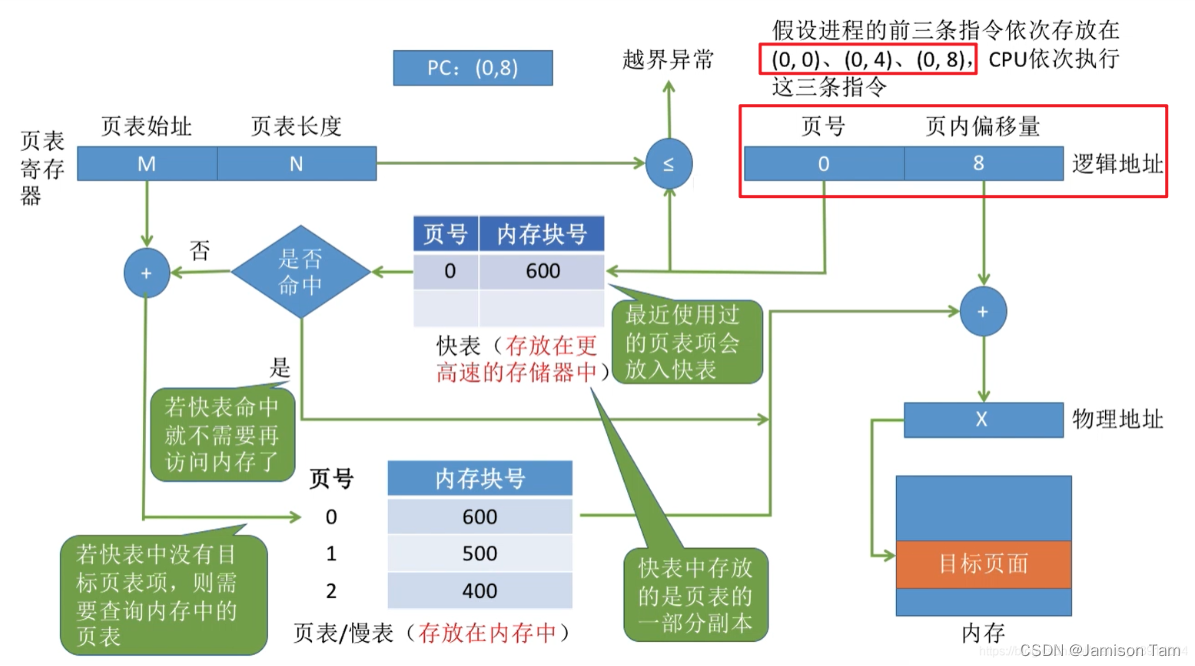

基本地址变换季候可以借助页表将逻辑地址转换为物理地址,通常在系统中设置一个页表寄存器PTR, 存放页表在内存中的起始地址F和页表长度M

进程未执行时,页表的始址和页表长度都放在PCB中,当进程被调度后,操作系统内核会把它们放到页表寄存器中

根据指令的逻辑地址,计算出页号和页内偏移量

判断页号是否越界

查询页表中对应的页表项,确定内存块号

用内存块号和页内偏移量得出实际物理地址

整体过程和前面推导的一致,而这部分地址转换工作就是通常基本地址转换结构完成

快表

优化基本地址转换结构

又称联想寄存器TLB,是一种访问速度比内存快很多的高速缓冲存储器,用来存放当前访问的若干页表项,加速地址转换,内存中的页表常称为慢表

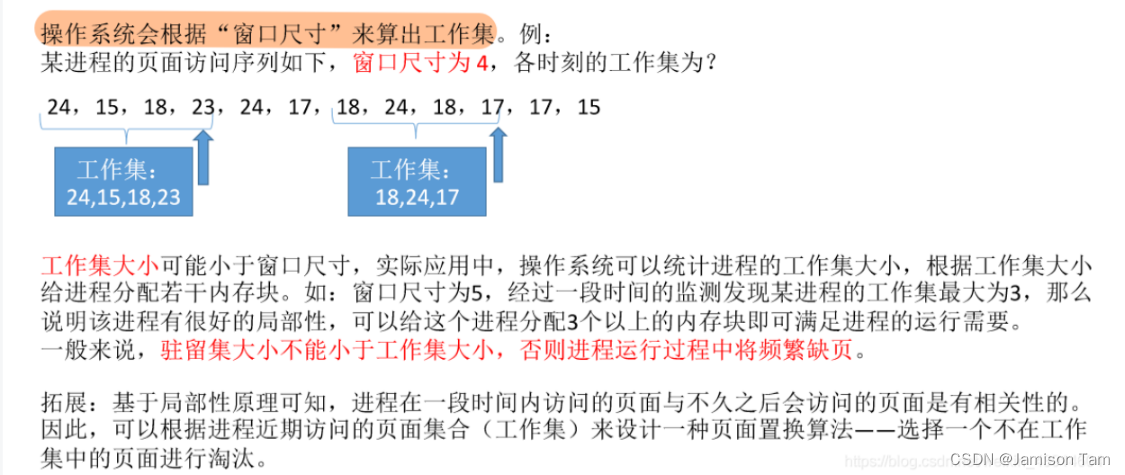

局部性原理

时空局部性

指令a刚被执行了,则不久后很可能会被再次执行

空间局部性

存储单元a刚被访问了,则不久后很可能会被再次访问

cpu给出逻辑地址,算出页号和页内偏移量,将页号和快表中的页号进行比较

如果命中,则直接取出内存块号,产生一次访存

否则再查询内存中的页表,产生两次访存

二级页表

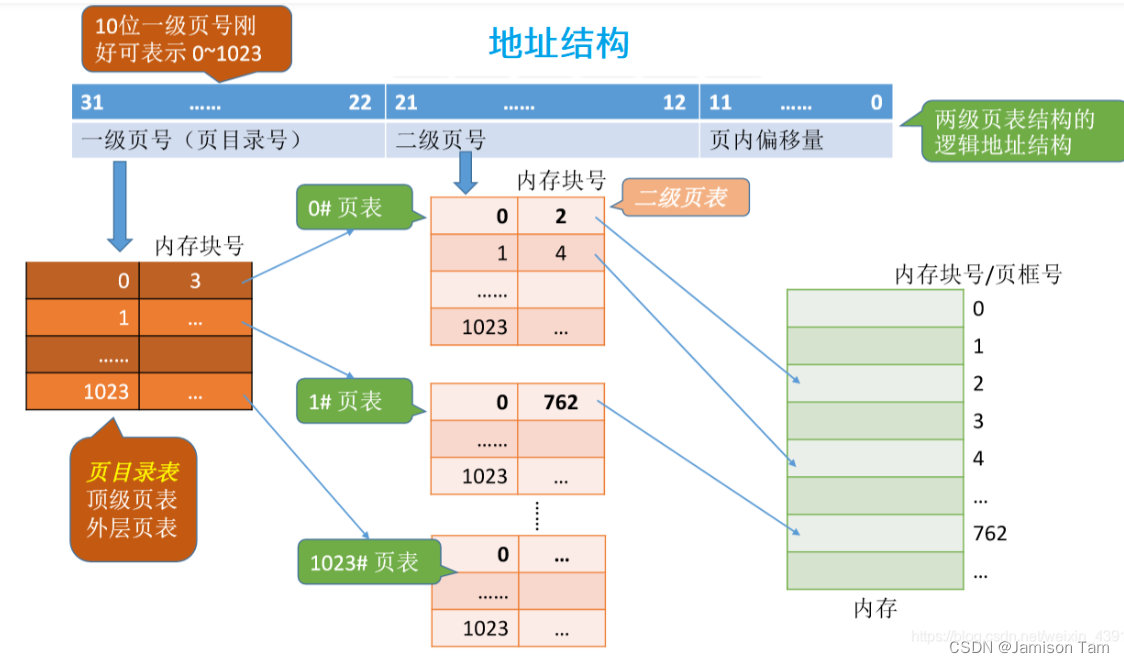

由于单级页表,需要的页表非常大,且使用时需要页表项连续,即需要整个页表放入内存中

而由局部性原理可知,不是需要所有页表项放入内存中,因此我们需要建立另一张页表,记录各页面的存放位置,这样就解决了页表必须连续存放的问题,这个表称为页目录表,或称外层页表、顶层页表

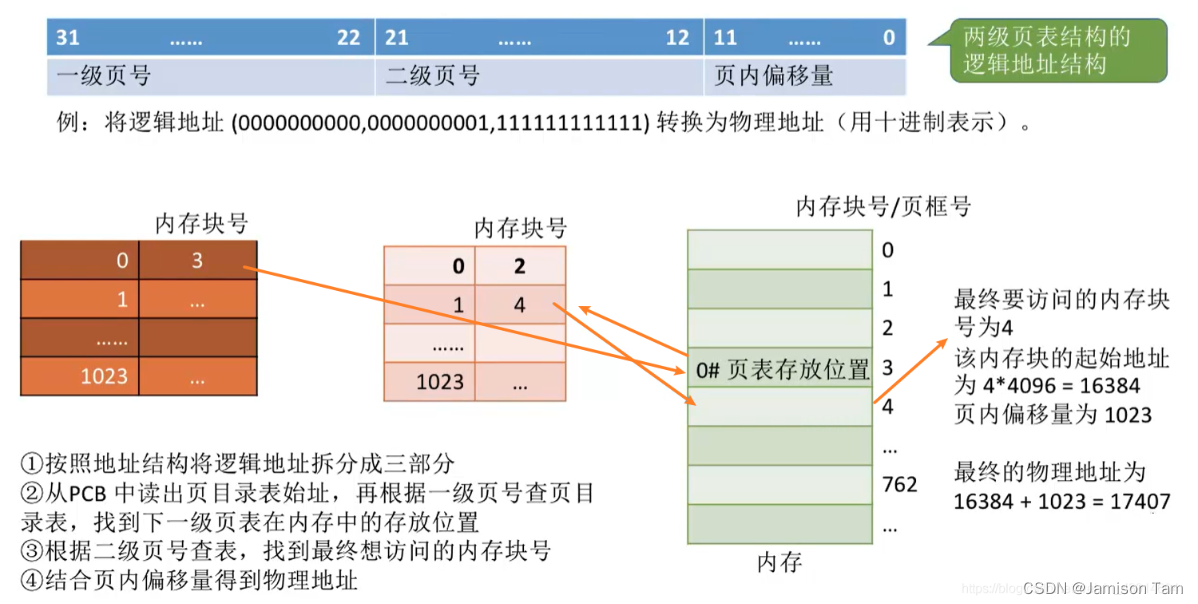

地址结构

对页表进行分组

地址转换

一级页号对应的内存号,存放着二级页表的地址,皆由二级页表和页内偏移量获取物理地址

而问题二,页表常驻内存问题,可通过虚拟存储解决,需要时才调入内存

多级页表机制,各级页表大小不能超过一个页面

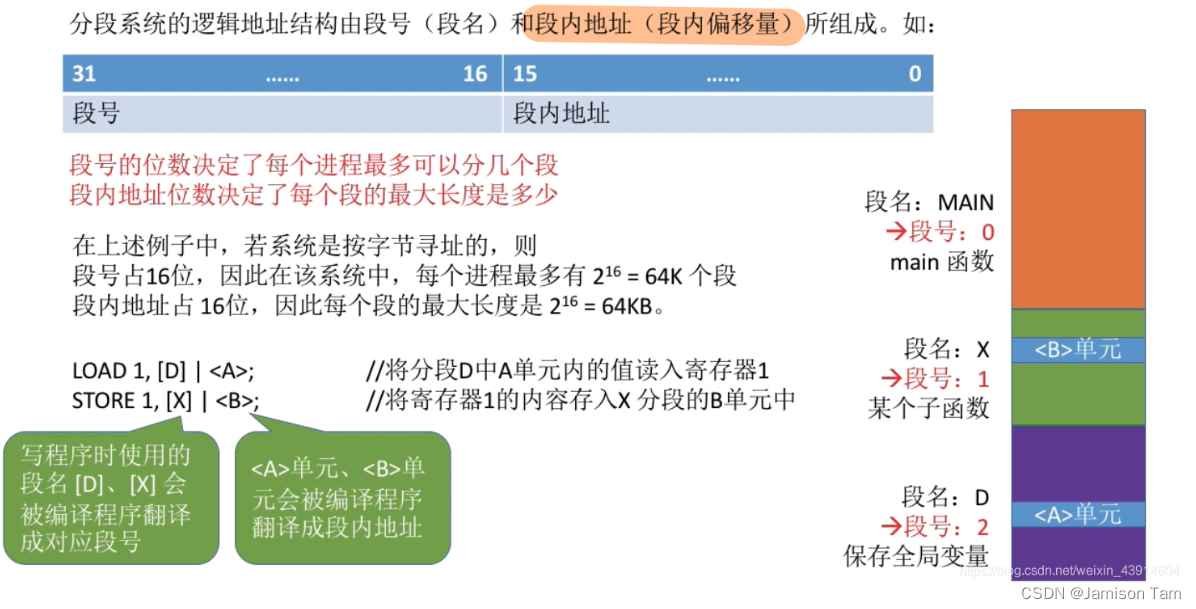

基本分段管理

根据自身逻辑关系划分为若干个段,每个段都有段名,每个段在内存中占据连续空间,各段间可不连续

逻辑结构

段号+段内地址

每个段对应一个段表项,记录了该段在内存中的起始位置和段长度

参考分区的管理,自然也要引入段表

每个段对应一个段表项,记录了段长和基址(起始地址)

每个段表项的长度是相同的,段号同样是隐藏的

地址变换

与分页类似,都是通过逻辑地址得出段号和段内地址,通过段表寄存器,查询对应的段表获得获取段的基址和长度,最后定位到内存中的位置,期间包含对段内地址和段号的越界检查

分段与分页的对比

页是信息的物理单位,分页用于实现离散分配,提高内存利用率,分页仅仅是为了系统管理上面的需要,用户不可见

段是信息的逻辑单位,分段用于更好的满足用户需求,一个段包含着一组属于一个逻辑模块的信息。分段对用户可见,由用户显式给出段名

分页的用户进程的地址空间是一维的,一个记忆符表示一个地址

分段的用户进程的地址空间是二维的,通过段名和段内地址标记一个地址

分段比分页更容易实现信息的共享和保护

分段的共享和保护

不能被修改的代码被称为纯代码或可重入代码,可共享的

如管理缓冲区的代码,只是检查缓冲区是否可访问,只需让各进程的段表项指向同一段即可实现共享

页表项不支持是因为页很小,且不按逻辑分区,因此会出现该分区的一部分不能共享,一部分可共享

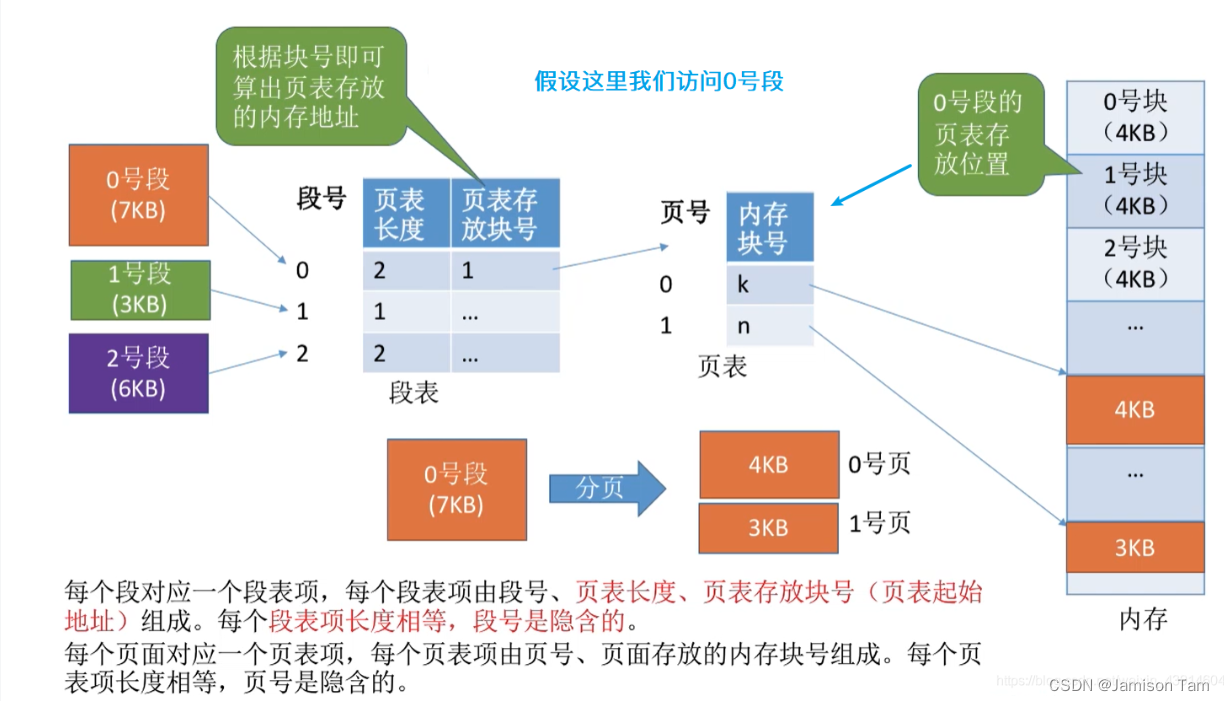

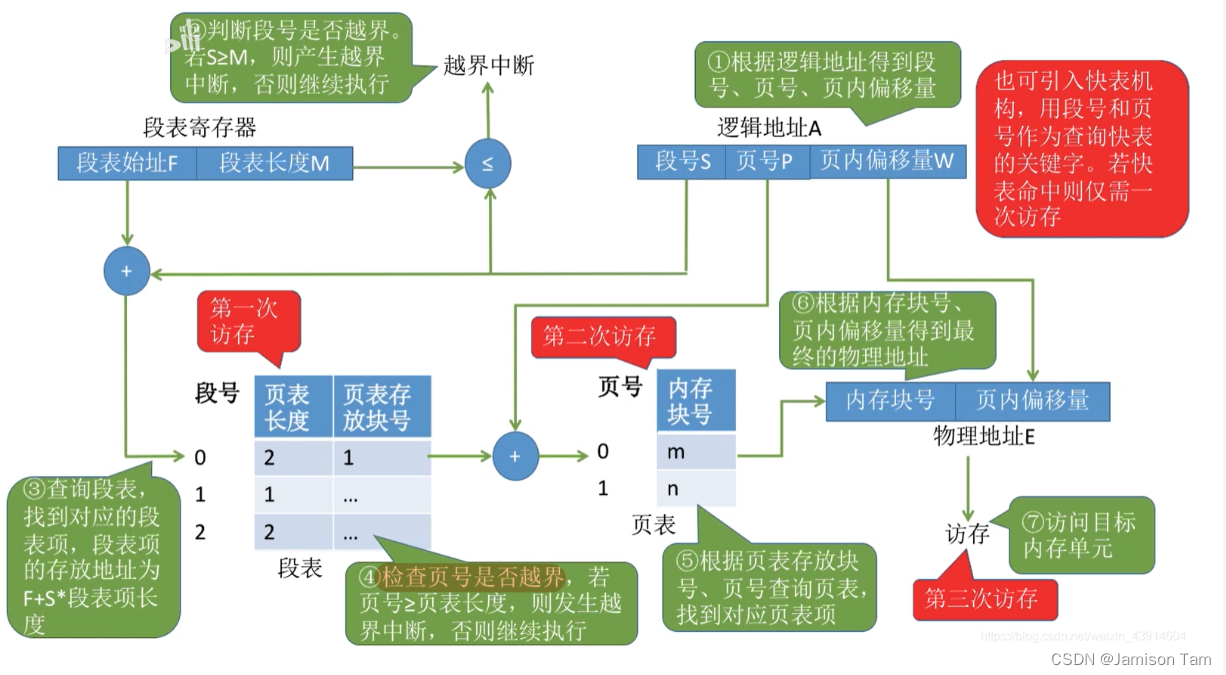

段页式存储管理

段页式即先分段,再分页

段和页的优缺点

分页有很高的内存空间利用率,不会产生外存碎片,只有少量页内碎片,不方便按照逻辑模块实现信息的共享和保护

分段很方便按照逻辑实现信息的共享和保护,但段长过大时,分配连续空间很不方便,且产生外部碎片

段页式逻辑结构

段号+页号+页内地址

地址转换

与段、页类似

![leetcode96--不同的二叉搜索树[java]](https://img-blog.csdnimg.cn/e8ded3d2aee344ec91f51996d9d2adde.png#pic_center)