写在前面的话:此系列文章为笔者学习计算机组成原理时的个人笔记,分享出来与大家学习交流。使用教材为唐朔飞第3版,笔记目录大体与教材相同。

网课

计算机组成原理(哈工大刘宏伟)135讲(全)高清_哔哩哔哩_bilibili

笔记

《计算机组成原理》唐朔飞 第5章 输入输出系统 - 学习笔记_友人帐_的博客-CSDN博客

《计算机组成原理》唐朔飞 第7章 指令系统 - 学习笔记_友人帐_的博客-CSDN博客

《计算机组成原理》唐朔飞 第8章 CPU的结构和功能 - 学习笔记_友人帐_的博客-CSDN博客

《计算机组成原理》唐朔飞 第9章 控制单元的功能 - 学习笔记_友人帐_的博客-CSDN博客

《计算机组成原理》唐朔飞 第10章 控制单元的设计 - 学习笔记_友人帐_的博客-CSDN博客

课后习题答案

计算机组成原理(第三版)唐朔飞-课后习题(完整版)_计算机组成原理唐朔飞第三版答案_蓝净云的博客-CSDN博客

哈尔滨工业大学计组实验

计算机组成原理实验一 运算器 预习报告_基本运算器实验_旅僧的博客-CSDN博客

计算机组成原理实验二 存储系统 预习报告_旅僧的博客-CSDN博客

计算机组成原理实验三 系统总线和具有基本输入输出功能的总线接口 预习报告_旅僧的博客-CSDN博客

计算机组成原理实验四 微程序控制器 实验报告_旅僧的博客-CSDN博客

第七章 指令系统

7.1 机器指令

7.1.1 指令的一般格式

1. 操作码

用来指明该指令所完成的操作,其位数反映了机器允许的指令条数。

(1)操作码的长度

-

长度固定:将操作码集中放在指令字的一个字段内。便于硬件设计,指令译码时间段,广泛用于字长较长的精简指令集计算机(RISC)中。

-

长度不固定:操作码分散在指令字的不同字段中。可以有效地压缩操作码的平均长度,在字长较短的微型计算机中广泛使用。

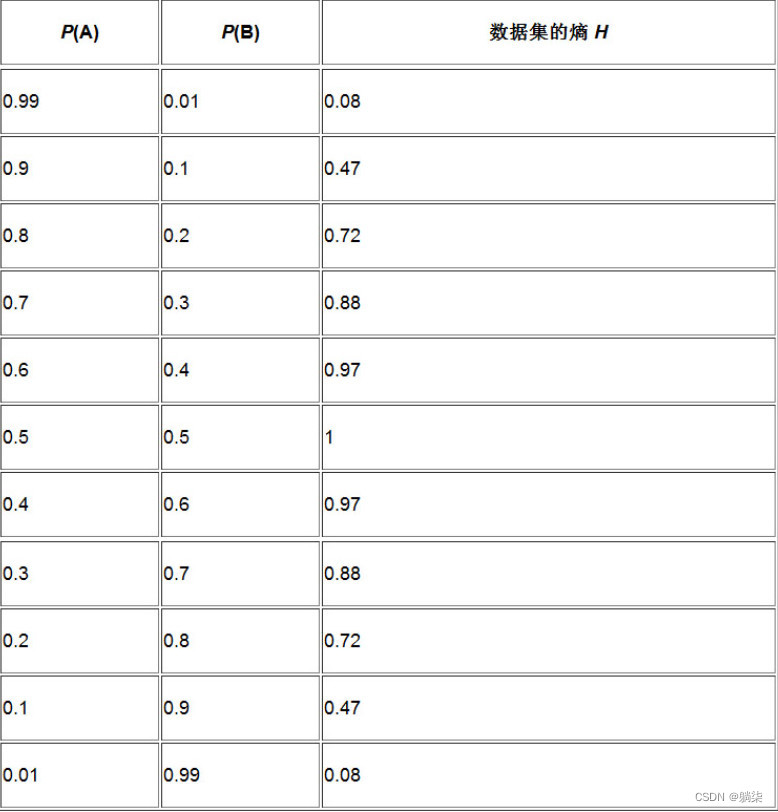

(2)扩展操作码技术

操作码长度不固定会增加指令译码和分析的难度,使控制器的设计复杂。通常采用扩展操作码技术,使操作码的长度随地址数的减少而增加,不同地址数的指令可以具有不同长度的操作码,从而在满足需要的前提下,有效地缩短指令字长。

保留码点方式:

操作码的位数随着地址数的减少而增加。为了使计算机能够识别操作码的位数,保留1111字段,作为拓展标记(见下图,图中操作数的地址码为4位)。

零地址、一地址、二地址指的是操作数有几个。指令字长固定的情况下,操作码的位数 = 指令字长 - 地址字长。可以通过不断减少多地址指令的操作码种类,来增加少地址指令的条数。

2. 地址码

地址码用来指出该指令的源操作数的地址(一个或两个)、结果的地址以及下一条指令的地址。这里的“地址"可以是主存的地址,也可以是寄存器的地址,甚至可以是I/О设备的地址。

以主存地址为例,分析指令的地址码字段。通过下面的分析可见,通过利用一些硬件资源(ACC、PC等),可在不改变指令字长的前提下,扩大指令操作数的直接寻址范围、减少访存次数,以提高机器性能。

(1)四地址指令

| OP | A 1 A_1 A1 | A 2 A_2 A2 | A 3 A_3 A3 | A 4 A_4 A4 |

|---|

其中,OP为操作码; A 1 A_1 A1为第一操作数地址; A 2 A_2 A2为第二操作数地址; A 3 A_3 A3为结果地址; A 4 A_4 A4为下一条指令的地址。

- 完成 ( A 1 ) O P ( A 2 ) → A 3 (A_1)OP(A_2)\rightarrow A_3 (A1)OP(A2)→A3的操作。

- 访问4次内存(取指令1次,取两个操作数2次,存放结果1次)。

(2)三地址指令

程序计数器PC既能存放下一条指令的地址,又可以自加1,使用PC代替 A 4 A_4 A4字段,得到三地址指令格式。

| OP | A 1 A_1 A1 | A 2 A_2 A2 | A 3 A_3 A3 |

|---|

- 完成 ( A 1 ) O P ( A 2 ) → A 3 (A_1)OP(A_2)\rightarrow A_3 (A1)OP(A2)→A3的操作。

- 访问4次内存(取指令1次,取两个操作数2次,存放结果1次)。

(3)二地址指令

没必要将每次结果都存入主存,可以暂存在CPU的寄存器中,省去 A 3 A_3 A3字段,得到二地址指令。

| OP | A 1 A_1 A1 | A 2 A_2 A2 |

|---|

- 完成 ( A 1 ) O P ( A 2 ) → A 1 (A_1)OP(A_2)\rightarrow A_1 (A1)OP(A2)→A1的操作。

- 访问4次内存(取指令1次,取两个操作数2次,存放结果1次)。

- 若完成 ( A 1 ) O P ( A 2 ) → A C C (A_1)OP(A_2)\rightarrow ACC (A1)OP(A2)→ACC的操作,则访问3次内存。

(4)一地址指令

将一个操作数的地址隐含在运算器的ACC中,指令字中只需给出一个地址码。

| OP | A 1 A_1 A1 |

|---|

- 完成 ( A C C ) O P ( A 1 ) → A C C (ACC)OP(A_1)\rightarrow ACC (ACC)OP(A1)→ACC的操作。

- 访问2次内存(取指令1次,取操作数1次)。

(5)零地址指令

无地址码,例如空操作(NOP)、停机(HLT)这类指令只有操作码;子程序返回(RET)、中断返回(IRET)这类指令操作数的地址隐含在堆栈指针SP中。

7.1.2 指令字长

指令字长取决于操作码的长度、操作数地址的长度和操作数的个数。

(1)指令字长固定

可以设置为机器字长和存储字长相等,因此访问某个存储单元,便可取出一条完整的指令或一个完整的数据。

(2)指令字长可变

一般按照字节的倍数变化。

7.2 操作数类型和操作类型

7.2.1 操作数类型

-

地址:绝对地址无符号整数;相对地址有符号数。

-

数字:定点数、浮点数、十进制数。

-

字符:普遍使用ASCII码。

-

逻辑数据:1真0假,参与逻辑运算。

7.2.2 数据在存储器中的存放方式

1. 大端序与小端序

(左:小端序;右:大端序)

2. 边界对准

数据存放的起始地址是数据类型大小的整数倍。

- 既保证了在一个存取周期可以进行访问,又不会过于浪费空间。

7.2.3 操作类型

1. 数据传送

| 源 | 目的 | 指令示例 |

|---|---|---|

| 寄存器 | 寄存器 | MOVE |

| 寄存器 | 存储器 | STORE; MOVE; PUSH |

| 存储器 | 寄存器 | LOAD; MOVE; POP |

| 存储器 | 存储器 | MOVE |

置1、清0等。

2. 算数逻辑操作

- 算术运算:加减乘除、增1、减1、求补(取负数);

- 逻辑运算:与或非、异或;

3. 移位

- 算术移位

- 逻辑移位

- 循环移位

4. 转移(跳转)

(1)无条件转移 JMP

(2)条件跳转

根据条件码来进行跳转。

(3)调用CALL与返回RET

CALL用于从当前的程序位置转至子程序的入口;RETURN用于子程序执行完成后返回到原程序的断点。

(4)陷阱Trap与陷阱指令

一旦运行过程中出现意外故障,计算机就发出陷阱信号,暂停当前程序的执行,转入故障处理程序进行相应的故障处理。

陷阱指令一般不提供给用户直接使用,而是作为隐指令在出现意外故障时由CPU自动产生并执行。

5. 输入输出

对于I/O单独编址的计算机而言,通常设有输入输出指令,它完成从外设中的寄存器读人-个数据到CPU的寄存器内,或将数据从CPU的寄存器输出至某外设的寄存器中。

6. 其他

其他包括等待指令、停机指令﹑空操作指令、开中断指令.关中断指令、置条件码指令等。

7.3 寻址方式

寻址方式是指确定本条指令的数据地址以及下一条将要执行的指令地址的方法。

7.3.1 指令寻址

1. 顺序寻址

通过程序计数器PC加1,自动形成下一条指令的地址。(加1并不是实际上加1,而是加1个单位,使得指向下一条指令。可能是2字节、4字节、8字节等)

2. 跳跃寻址

通过转移类指令实现。

7.3.2 数据寻址

-

数据寻址方式种类较多,在指令字中必须设一字段来指明属于哪一种寻址方式。

-

形式地址A:指令字中的地址。通常都不代表操作数的真实地址。

-

有效地址EA:操作数的真实地址,由寻址方式和形式地址共同来确定的。

假设指令字长、存储字长、机器字长相等。

1. 立即寻址

形式地址A不是操作数的地址,而是操作数本身(补码),称为立即数。使用#表示立即寻址特征标记。

2. 直接寻址

形式地址A就是操作数的真实地址EA。

- 比较简单。

- A的位数限制了操作数的范围;且修改操作数必须修改A的值。

3. 隐含寻址

指令字中不明显地给出操作数的地址,其操作数的地址隐含在操作码或某个寄存器中。

例如,一地址格式的加法指令只给出一个操作数的地址,另一个操作数隐含在累加器ACC中,这样累加器ACC成了另一个数的地址。

- 有利于缩短指令字长。

4. 间接寻址 @

形式地址不直接指出操作数的地址,而是指出操作数有效地址所在的存储单元地址,即EA=(A)。(指针)

- 扩大了操作数的寻址范围(由A那么长变成了整个存储字长那么长)。

- 多次间接寻址时用存储字的首位来标记间接寻址是否结束。1表示继续,0表示结束。故存储字首位不能作为EA的组成部分。

- 便于编写程序,方便调用子程序跳转。多次寻址导致指令执行时间延长。

5. 寄存器寻址

在寄存器寻址的指令字中,地址码字段直接指出了寄存器的编号,即 E A = R i EA=R_i EA=Ri。其操作数在由R所指的寄存器内。

- 无须访存,减少了执行时间。

- 地址字段只需指明寄存器编号(计算机中寄存器数有限),故指令字较短,节省了存储空间。

6. 寄存器间接寻址

寄存器中存放的是操作数所在主存单元的地址,即 E A = ( R i ) EA=(R_i) EA=(Ri)。

7. 基址寻址

基址寻址需设有基址寄存器BR,其操作数的有效地址EA等于指令字中的形式地址与基址寄存器中的内容(称为基地址)相加,即EA=A+(BR)。

!BR的值由操作系统自动给出,用户不得修改。

基址寄存器分为显式和隐式两种:

- 隐式:计算机内专门设有一个BR,使用时不必指出,体现出指令为基址寻址方式即可。

- 显式:在一组通用寄存器中,由用户明确指出哪个寄存器用作基址寄存器,存放基地址。

- 扩大操作数的寻址范围(将主存空间分为若干段,BR里存放段首地址,A里存放偏移量,采用段地址+段内偏移量来寻址)

8. 变址寻址

其有效地址EA等于指令字中的形式地址A与变址寄存器IX的内容相加之和,即EA=A+(IX)。

!IX的值由用户给定。

基址寻址与变址寻址的区别:

- 基址寻址主要用于为程序或数据分配存储空间,故基址寄存器的内容通常由操作系统或管理程序确定,在程序的执行过程中其值是不可变的,而指令字中的A是可变的。

- 在变址寻址中,变址寄存器的内容是由用户设定的,在程序执行过程中其值可变,而指令字中的A是不可变的。

变址寻址主要用于处理数组问题,在数组处理过程中,可设定A为数组的首地址,不断改变变址寄存器IX的内容,便可很容易形成数组中任一数据的地址,特别适合编制循环程序。

9. 相对寻址 *

有效地址是将程序计数器PC与指令字中的形式地址A相加而得,即EA=(PC)+A。

- 常用于跳转,A称为位移量,可正可负,用补码表示。

- 转移地址不固定,可随PC的变化而变化,无论程序在主存的哪段区域都可正常运行。

10. 堆栈寻址

堆栈寻址要求计算机中设有堆栈。

堆栈既可用寄存器组(称为硬堆栈)来实现,也可利用主存的一部分空间作堆栈(称为软堆栈)。

以软堆栈为例,可用堆栈指针SP(Stack Point)指出栈顶地址,也可用CPU中一个或两个寄存器作为SP。操作数只能从栈顶地址指示的存储单元存或取。可见堆栈寻址也可视为一种隐含寻址,其操作数的地址总被隐含在SP中。堆栈寻址就其本质也可视为寄存器间接寻址,因SP可视为寄存器,它存放着操作数的有效地址。

SP的修改与主存编址方式有关。进栈-,出栈+,向低地址生长。

- 按字编址:进出栈SP±1

- 按字节编址

- 存储字长16位:进出栈SP±2

- 存储字长32位,进出栈SP±4

7.4 指令格式举例

7.4.1 需考虑因素

-

指令系统的兼容性

-

操作类型:包括指令数及操作的难易程度。

-

数据类型:确定哪些数据类型可以参与操作。

-

指令格式:包括指令字长、操作码位数、地址码位数、地址个数、寻址方式类型,以及指令字长和操作码位数是否可变等。

-

寻址方式:包括指令和操作数具体有哪些寻址方式。

-

寄存器个数:寄存器的多少直接影响指令的执行时间。

7.5 RISC技术

精简指令系统计算机 (Reduced Instruction Set Computer)

与之对应的为:CISC ,复杂指令系统计算机 (Complex Instruction Set Computer)

7.5.1 RISC的主要特征

- 选用使用频度较高的一些简单指令,复杂指令的功能由简单指令来组合

- 指令长度固定、指令格式种类少、寻址方式少

- 只有

LOAD/STORE指令访存 - CPU中有多个通用寄存器

- 采用流水技术一个时钟周期内完成一条指令

- 采用组合逻辑实现控制器

7.5.2 CISC的主要特征

- 系统指令复杂庞大,各种指令使用频度相差大

- 指令长度不固定、指令格式种类多、寻址方式多

- 访存指令不受限制

- CPU中设有专用寄存器>

- 大多数指令需要多个时钟周期执行完毕

- 采用微程序控制器

7.5.3 RISC和CISC的比较

- RISC更能充分利用VLSI芯片的面积

- RISC更能提高计算机运算速度:指令数、指令格式、寻址方式少,通用寄存器多,采用组合逻辑,便于实现指令流水

- RISC便于设计,可降低成本,提高可靠性

- (缺点)RISC不易实现指令系统兼容

![对DataFrame指定字段进行整数编码df[‘字段名称‘].factorize()[0]](https://img-blog.csdnimg.cn/img_convert/cbf97150e4ad93ed868f9b88cbe358be.png)