笔者有幸接触了arc处理器,今天就来简单了解一下arc的编程模型

1、ARC基本认识

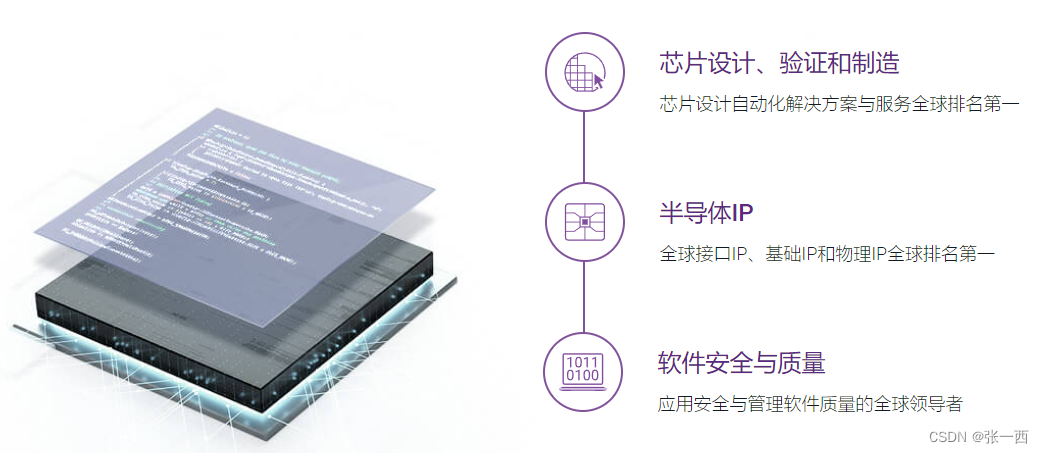

ARC IP是synopsys 新思公司开发的一个系列ARC IP核,其是一家电子设计自动化(EDA)解决方案提供商。其主页地址在这里!业务主要如下:

今天主要来聊一下其下的一些IP核,主要有如下几种:

-

ARC 600:ARCv1指令集

- Synopsys 的 DesignWare® ARC® 600 系列处理器芯核为 32 位 RISC 处理器芯核,其针对嵌入式应用和 DSP 任务高性能和低功耗的要求进行了优化。

- DesignWare ARC 600 系列处理器芯核拥有灵活的存储器选项,例如针对指令和数据的单周期紧密耦合内存 (CCM),以及可配置指令缓存 (I-cache) 和数据缓存 (D-cache),可有效满足各种处理需求。

- ARC 600 系列包括 ARC 601、ARC 605、ARC 610D 和 ARC 625D 处理器。这些处理器均可高度配置,每个实例均可以进行定制,从而在性能、能耗和面积之间达到理想的平衡,让 SoC 设计人员能够针对具体目标应用对处理器进行优化。此外,ARC 600 处理器还具有可扩展性,可让设计人员添加自己的定制指令,从而大大提高性能。

- 可选的 DSP 和浮点单元 (FPU) 功能,使得设计人员可利用单一的主机应用处理器满足各类处理需求。使用单一的处理器可简化设计、减少硅面积,实现更快的芯片调试。

- ARC处理器采用16/32位指令集架构设计,该架构提供了高代码密度,并且在16和32-位指令之间没有切换开销。凭借灵活的寻址模式,ARC 625D提供多达128个双或单操作数指令代码,可用于用户定义指令,以及多达64个可直接寻址核心寄存器和32个条件执行代码。

-

ARC 700:ARCv1指令集

- Synopsys 的 DesignWare® ARC® 700 系列处理器芯核为 32 位 RISC 处理器芯核,是要求高性能和低功耗的深嵌入式应用和 DSP 任务的完美解决方案。DesignWare ARC 700 系列处理器芯核拥有灵活的存储器选项,例如针对指令和数据的单周期紧密耦合内存 (CCM),以及可配置指令缓存 (I-cache) 和数据缓存 (D-cache),可有效满足各种处理需求。

- DesignWare ARC 700 系列包括 ARC 710D、ARC 725D 和 ARC 770D 处理器,这些处理器均可高度配置,每个实例均可以进行定制,从而在性能、能耗和面积之间达到理想的平衡,让 SoC 设计人员能够针对具体目标应用对处理器进行优化。此外,ARC 700 处理器还具有可扩展性,可让设计人员添加自己的定制指令,从而大大提高性能。

- 可选的 DSP 和浮点单元 (FPU) 功能,使得设计人员可利用单一的主机应用处理器满足各类处理需求。使用单一的处理器可简化设计、减少硅面积,实现更快的芯片调试。

-

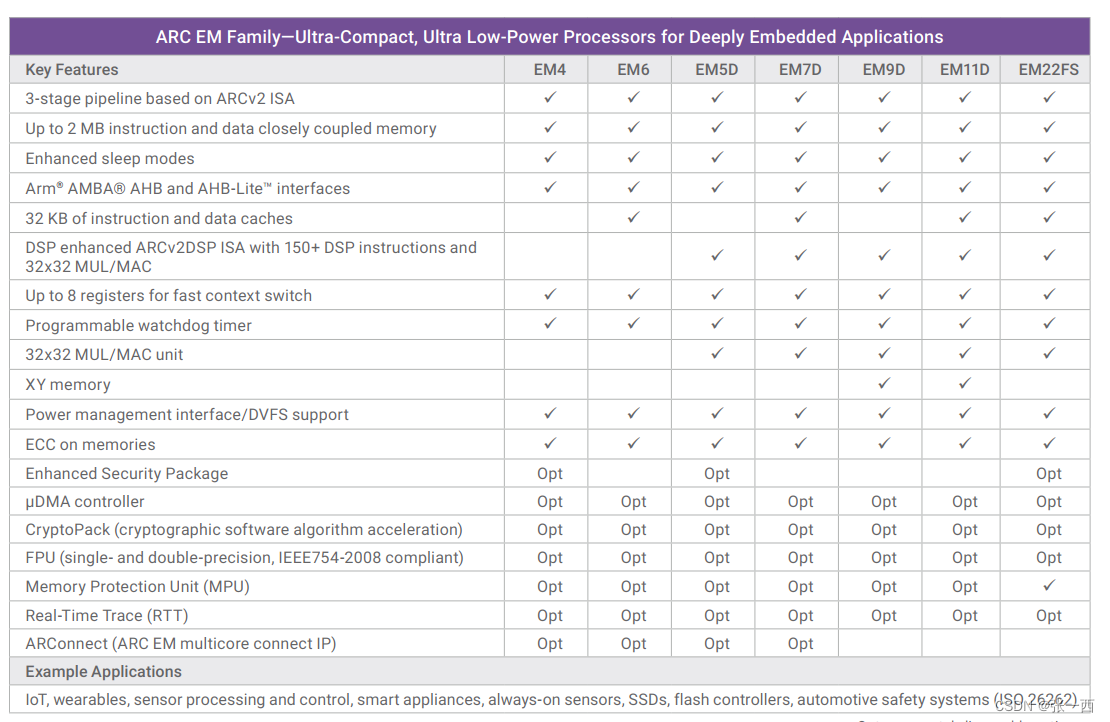

ARC EM 系列:针对微控制器,对内存Flash空间以及功耗敏感的场景。

- 基于 ARCv2 指令集架构 (ISA) 的 DesignWare® ARC® EM 系列包括 ARC EM4 、EM6、EM5D/7D、EM9D/EM11D以及EM22FS等

- 超紧凑型 EM 内核具有出色的代码密度、小巧的尺寸和非常低的功耗,使其非常适合注重功耗和面积的嵌入式和深度嵌入式应用。

-

ARC HS系列:针对高性能嵌入式应用

- 基于高效 ARCv2 指令集架构 (ISA) 的 DesignWare® ARC® HS 系列包括 HS3x、HS4x 和 DSP 增强型 HS4xD 处理器。所有 HS 处理器都支持紧密耦合内存 (CCM),实现单周期访问指令和数据

- HS 处理器针对GHz+ 的运行速度进行了优化,并具有超小的面积和功耗,使其非常适合对性能要求非常高的嵌入式应用。所有的 HS 处理器都提供单核、双核和四核配置。

-

ARC EV系列:针对嵌入式视觉处理器应用

- 主要有EV74/74FS 、EV72/EV72FS、EV71/EV71FS IP核。

- DesignWare® ARC EV 处理器是完全可编程和可配置的 IP 核,它针对嵌入式视觉应用进行了优化,融合了软件解决方案的灵活性和硬件的低成本和低功耗等特点。为了快速准确地执行卷积神经网络 (CNN) 或递归神经网络 (RNN),EV 处理器集成了可选的高性能深度神经网络 (DNN) 加速器。

- EV 处理器设计用于无缝集成到 SoC 中,并且能和任何主处理器一同使用,还能和主机并行运行。为了加速应用软件开发,EV 处理器得到了基于现有和新兴嵌入式视觉和神经网络标准的全面软件编程环境的支持,包括 OpenCV、OpenVX™、OpenCL™ C 以及采用 Synopsys 的 ARC MetaWare EV 开发工具包的 Caffe。

-

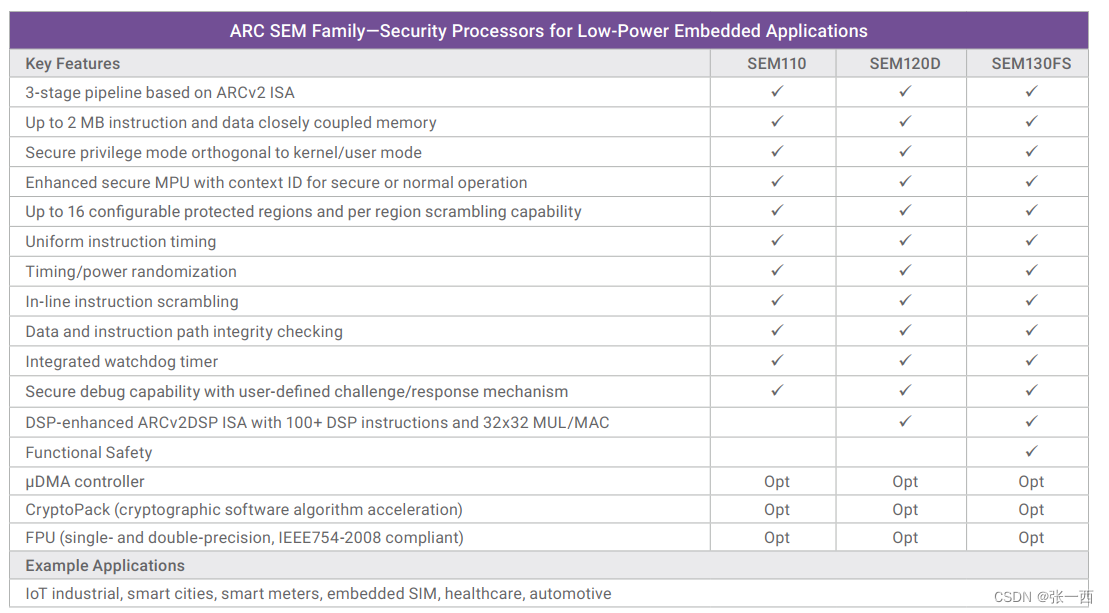

ARC SEM系列:主打安全领域的性能功耗一体的应用场景

- SEM系列包括性能高效、超低功耗、紧凑型安全处理器,使设计人员能够将安全集成到其SoC中,以抵御逻辑、硬件和物理攻击。

- 基于ARCV2指令集,具有紧密耦合存储器和外围设备的能力。它们集成了非常适合各种嵌入式应用程序的安全功能,可以作为独立的安全核心或同时执行安全和正常功能的单个核心。

- ARC SEM系列包括SEM110和SEM120D处理器。这两个处理器都包括上面列出的功能,SEM120D增加了一个DSP指令集和统一的乘法/MAC单元。它适用于在同一核心中需要实时处理和安全功能的应用程序

-

ARC VPX系列:DSP处理器架构,面向嵌入式终端,如物联网以及音频等领域

- DesignWare® ARC® VPX DSP 系列针对嵌入式工作负载的独特功率、性能和面积 (PPA) 要求进行了优化,例如物联网传感器融合、雷达和激光雷达处理、发动机控制、语音/言语识别、自然语言处理和其他终端 AI 应用。VPX 处理器基于增强型 ARCv2DSP 指令集,在 128 位(VPX2、VPX2FS)和 256 位(VPX3、VPX3FS)矢量字上运行,根据相同的超长指令字 (VLIW)/单指令多数据 (SIMD) 架构补充现有的 512 位 VPX5 和 VPX5FS。

- 安全增强型 ARC VPXxFS 处理器集成了硬件安全特性,包括针对内存和接口的纠错码 (ECC) 保护、安全监测器和锁步机制,有助于设计人员达到最严格的 ISO 26262 ASIL B、ASIL C 和 ASIL D 功能安全合规水平

-

ARC NPX系列:面向AI需要神经网络模型支持数据运算的领域,如高级驾驶员辅助驾驶。

- 全新的 DesignWare® ARC® NPX 神经处理单元 (NPU) IP 系列可为最新、最复杂的神经网络模型提供业界最佳的性能和支持。DesignWare ARC NPX6 NPU IP 提供高达 96K MAC 的能力,支持更高的 MAC 利用率、新的稀疏性和新的可扩展性互连,可满足 AI 应用的超低功耗实时计算需求。

- 单个 ARC NPX6 NPU IP 实例可在 1.3 GHz, 5nm 工艺最坏情况下 (worst case),提供高达 250 TOPS 的性能,或者通过使用新的稀疏功能提供高达 440 TOPS 的性能,这可以提高神经网络的性能并降低其能源需求。NPU IP 和新的 MetaWare MX 开发工具包都集成了连接特性,可实现多个 NPU 实例的实施,从而在单个 SoC 上实现高达 3,500 TOPS 的性能。

- 用于功能安全的神经处理器 IP,DesignWare ARC NPX6FS NPU IP 满足严苛的随机硬件故障检测和系统功能安全开发流程要求,可以达到 ISO 26262 ASIL D 安全等级。这些处理器包含全面的安全文档,具有符合 ISO 26262 标准的专用安全机制,可满足下一代区域架构的

备注:FS系列:功能安全(Functionality Security)

2、ARC寄存器认识

以ARC HS系列为例,简单介绍其寄存器模型。

其主要有以上寄存器,都是32位寄存器。

- 参数寄存器:r0-r7,8个参数,

- 暂存器:r10-r15

- 保存寄存器:r16-r25 调用函数需要保存的寄存器

- 指针寄存器:gp(全局指针)、fp(栈顶指针)、sp(栈底指针)

- 链接寄存器:ilink(异常链接寄存器)、blink(分支链接寄存器)

- 通用目的寄存器:genaral purpose reg,不是暂存器也不是保存寄存器

- 程序寄存器:PCL = PC & 0xFFFF FFFC ,PC 在arc里面是辅助寄存器,反应的时候实际的指令地址,其是只读半字对齐的寄存器。

3、ARC异常模型认识

待续