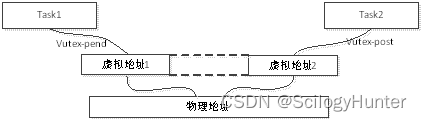

经过前面文章的学习,我们知道:不管是Verilog设计语言,还是Sytemverilog验证语言,标准都定义了语言调度机制,来规范各家编译器和仿真器的开发。今天,我们着重看一下Verilog 硬件设计语言中竞争问题,以及解决竞争问题的办法。

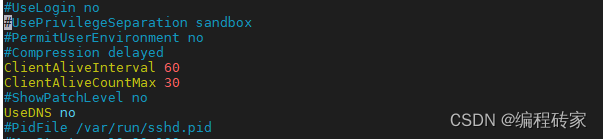

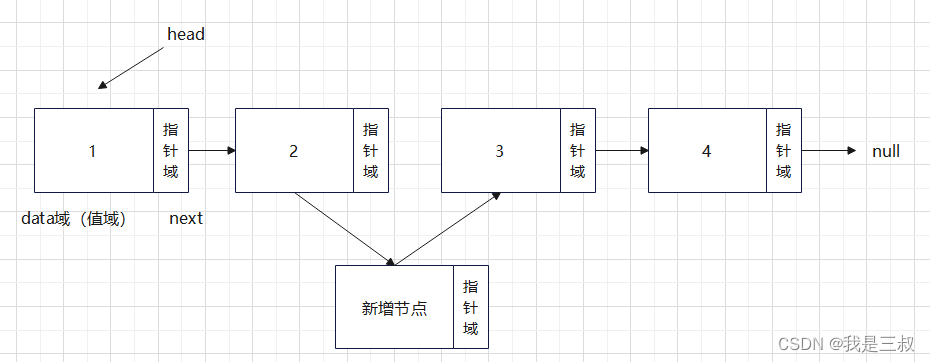

先上图,如下。大家都非常熟悉下面的调度机制了。这里不多说了。

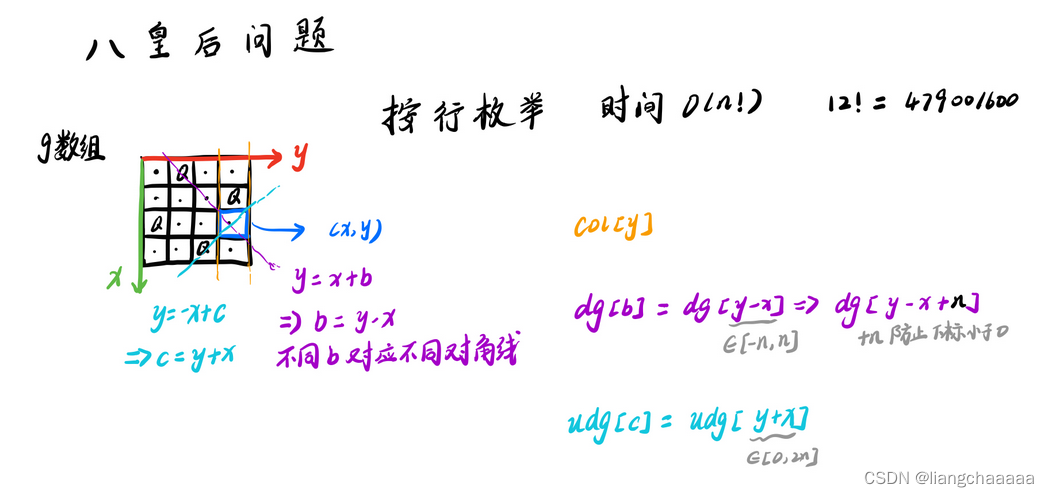

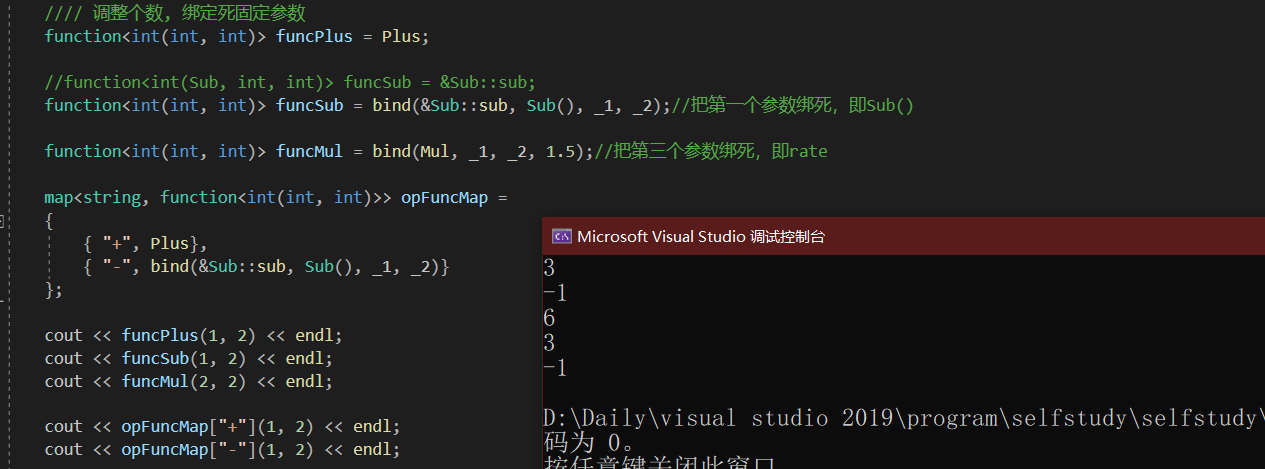

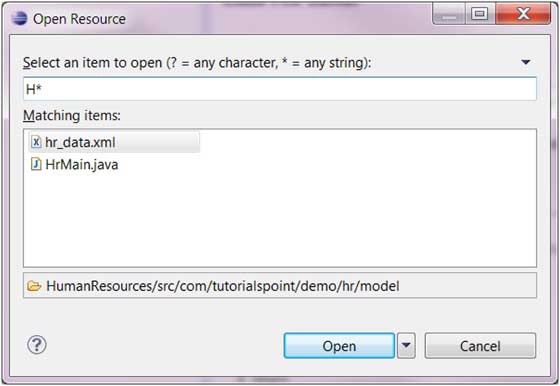

接下来,我们看一个例子:

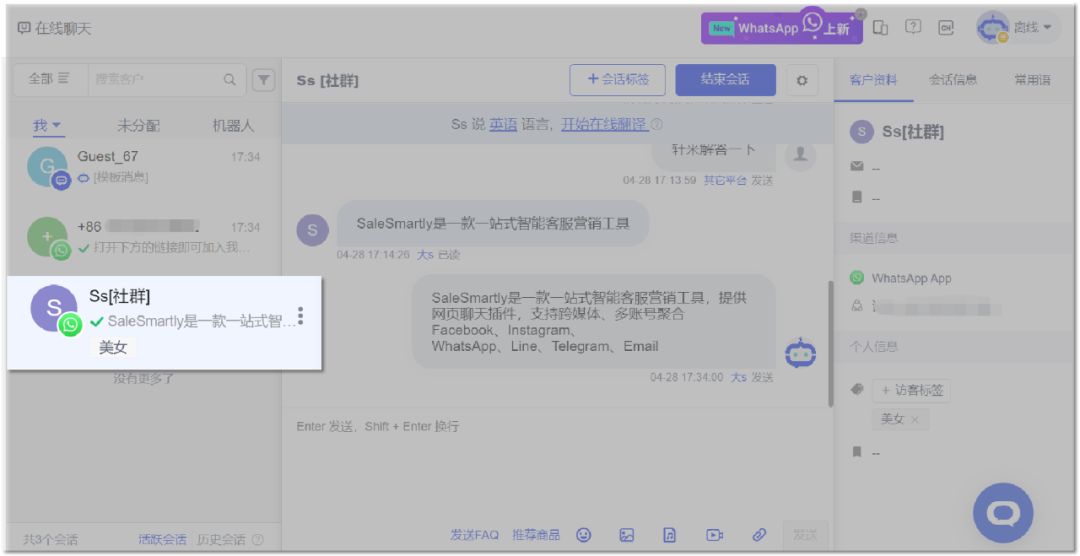

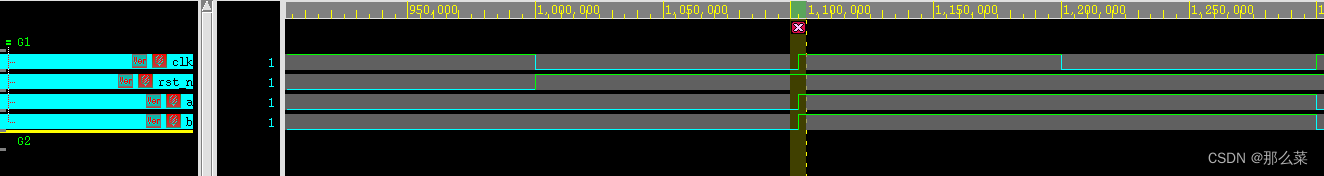

通过VCS+Verdi 工具查看波形如下:可见,使用阻塞赋值的方式,在每个clk 的时钟上升边沿,b的数值 === a 的数值。

我们通过仿真调度查看选项,看到的数值赋值情况如下,与仿真调度机制预期结果一致。

我们通过仿真调度查看选项,看到的数值赋值情况如下,与仿真调度机制预期结果一致。

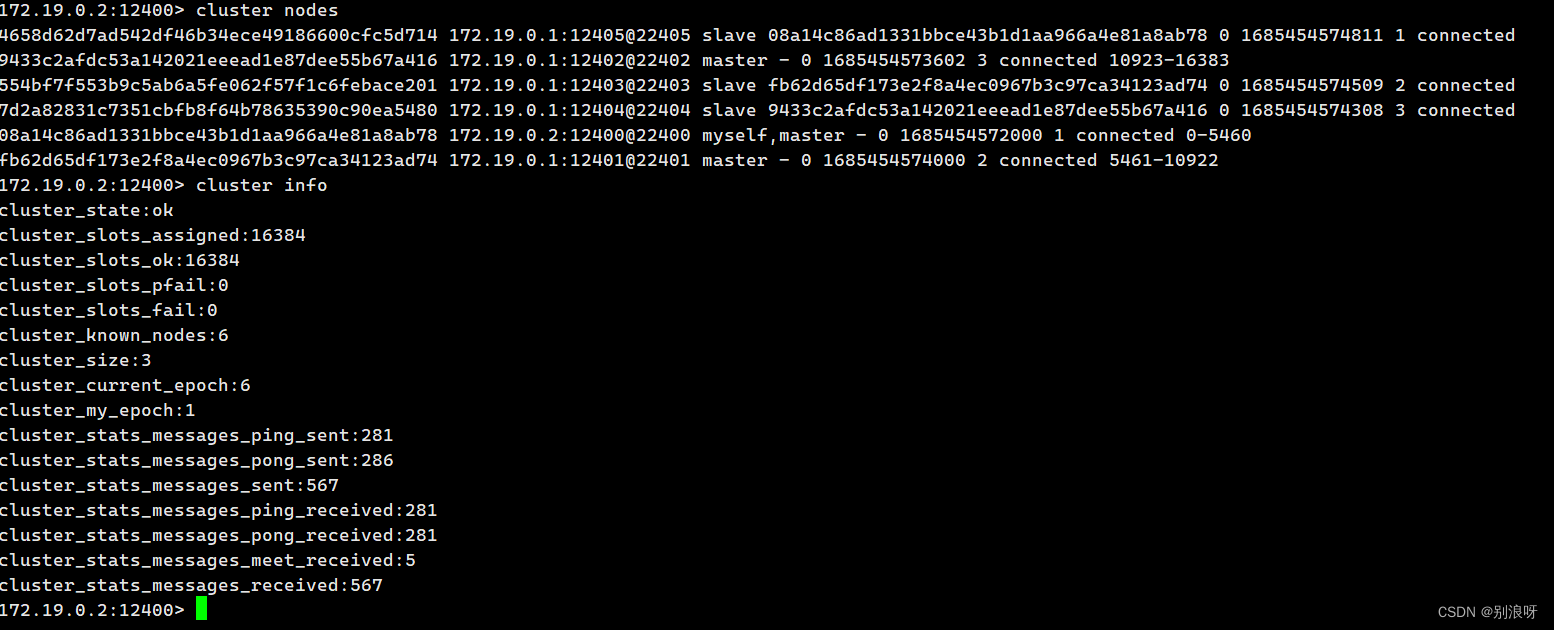

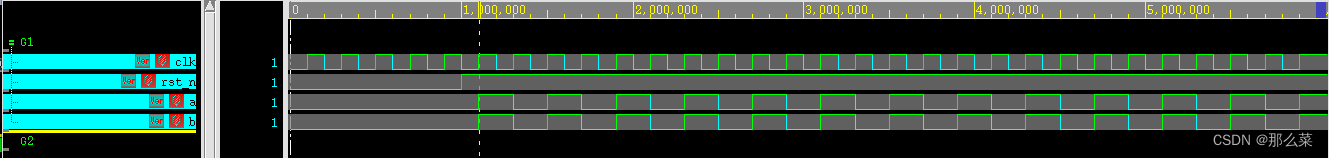

将上述例子,我们修改如下:使用非阻塞赋值的方式。

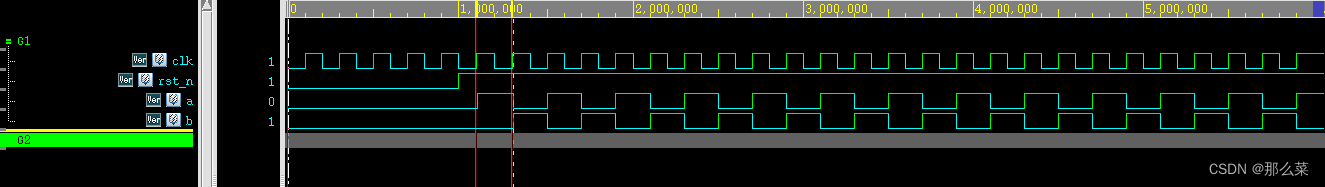

仿真结果,与实际硬件电路行为一致,避免了硬件电路的竞争现象发生。

我们通过仿真调度查看选项,看到的数值赋值情况如下,与仿真调度机制预期结果一致。

我们通过仿真调度查看选项,看到的数值赋值情况如下,与仿真调度机制预期结果一致。