HSST分为PCS和PMA,

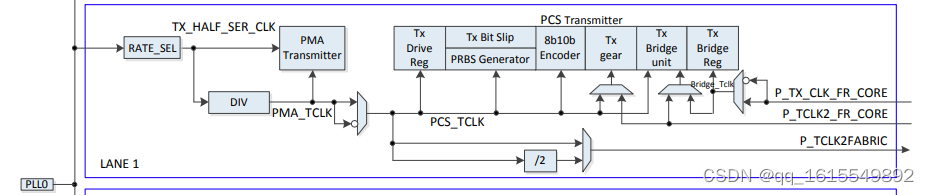

TX PCS:8b/10b编码

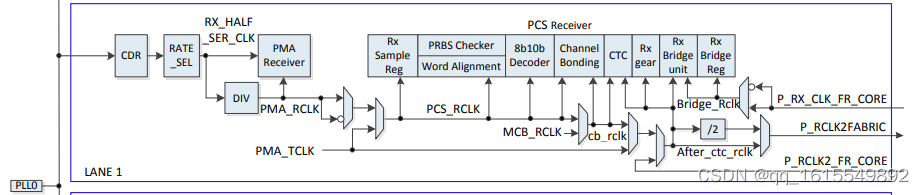

RX PCS

TX PMA

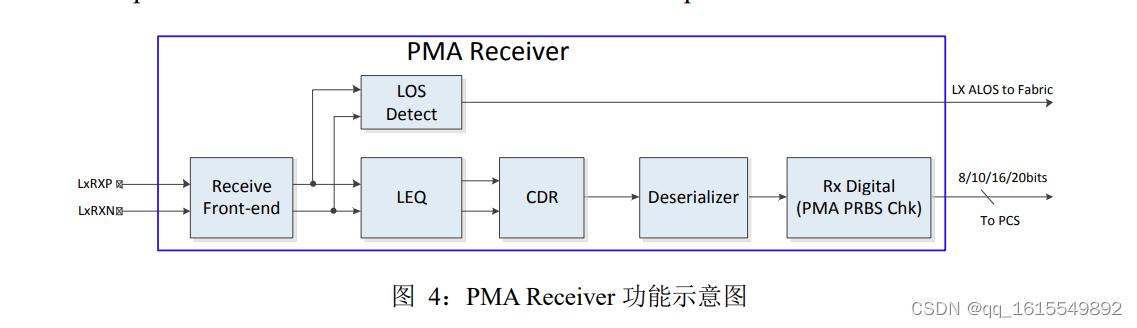

RX PMA

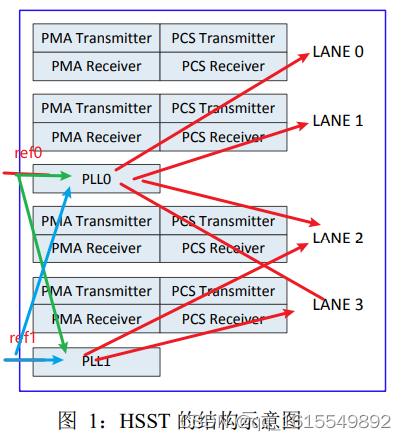

含1个HSST,有4个全双工收发LANE。

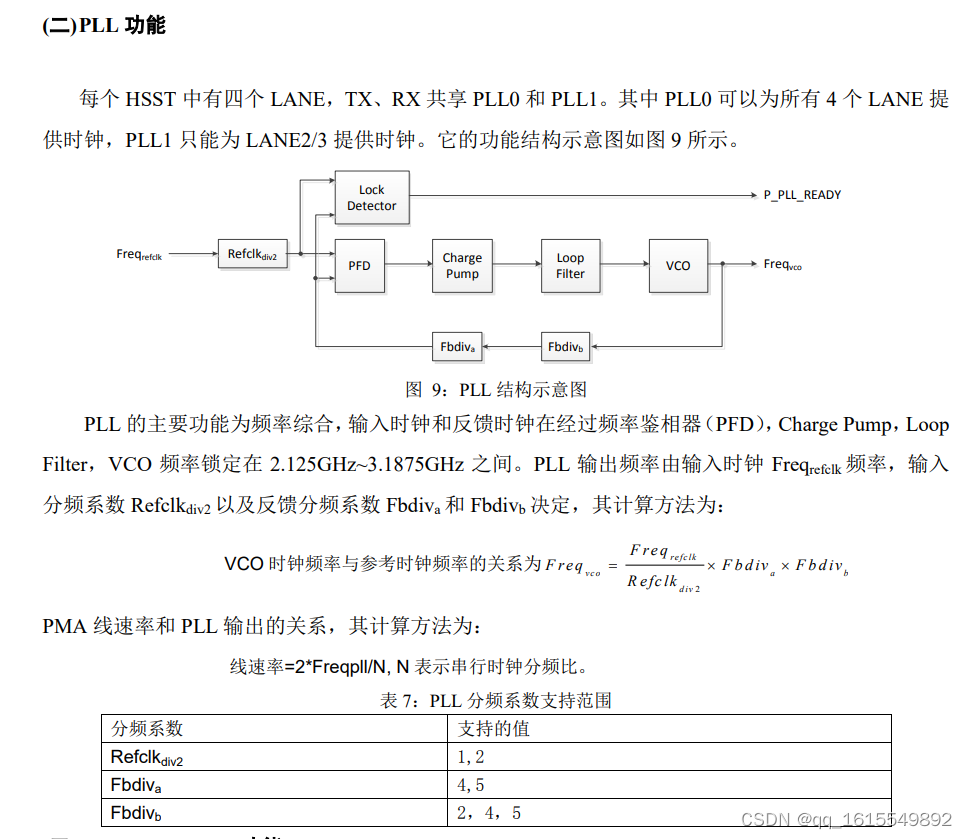

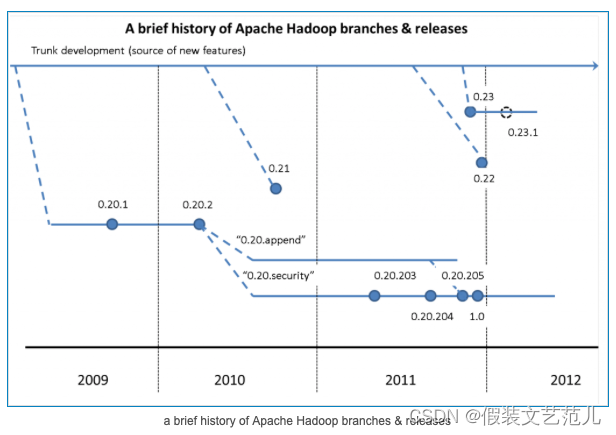

LINE和PLL的关系

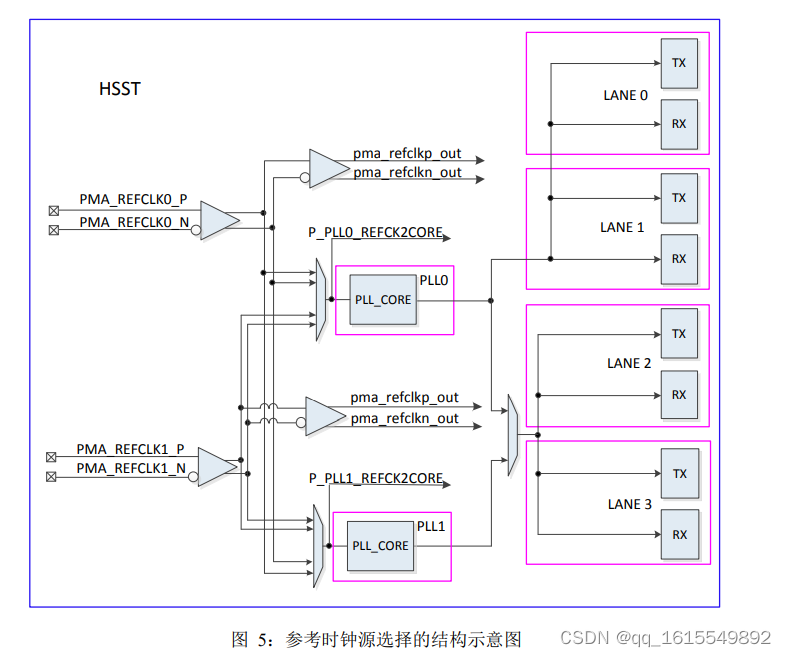

PLL0可以为4个LANE提供时钟,PLL1只能为LANE2&3提供时钟。

PLL VCO 的转出频率范围为 2.125GHz~3.1875GHz。PLL0 和 PLL1 都各自对应有一对外

部差分参考时钟输入,每个 PLL 还可以选择来自另一个 PLL 的参考时钟或者来自 Fabric 的时钟作为

参考时钟输入(Fabric 逻辑时钟做参考时钟,仅用于内部测试);PLL 输出频率支持动态再分频,以

适应 0.6Gbps~6.375Gbps 的线速率范围。

PCS框图

PMA框图

发送时钟

接收时钟

PLL

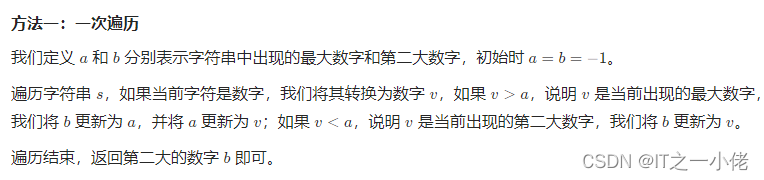

假如线速率是622.08M,参考时钟是多少?

633.08=77.76 x 8

refclkdiv=1;fbdiva=3,fbdivb=2

这也说明,当参考时钟固定,其线速率的选择也是固定值。

线速率的取值尽量是能整除,线速率也不是任意选择的。例如:我要线速率为1234.5678Mbps。没有对应的晶振做参考时钟。

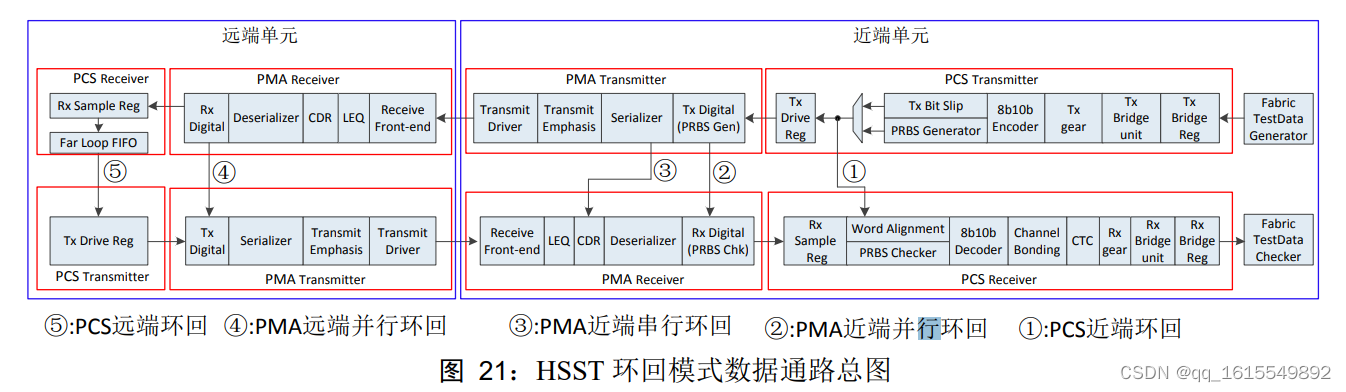

环回的定义

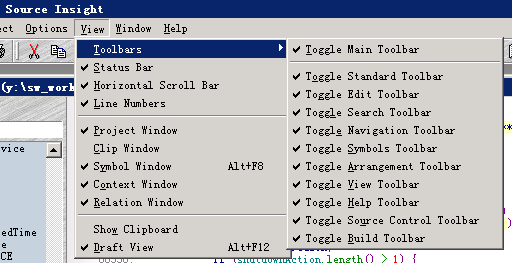

寄存器

略,太多了。

[1] UG

[2] 百度百科

![深度强化学习的组合优化[1] 综述阅读笔记](https://img-blog.csdnimg.cn/57d57efb3a1f429db78d1be169df3ee3.png)

![[附源码]计算机毕业设计JAVA学习资源共享与在线学习系统](https://img-blog.csdnimg.cn/78b0e29b6e2e43c2a0f15078d9b92b18.png)