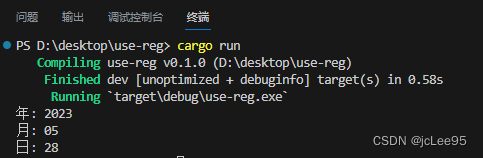

Reoder buffer(ROB)

为了解决异常问题

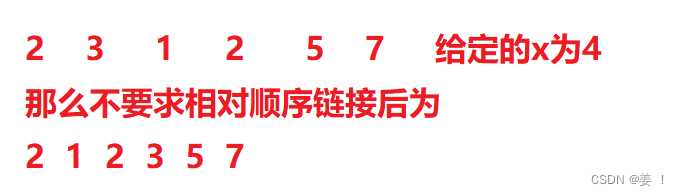

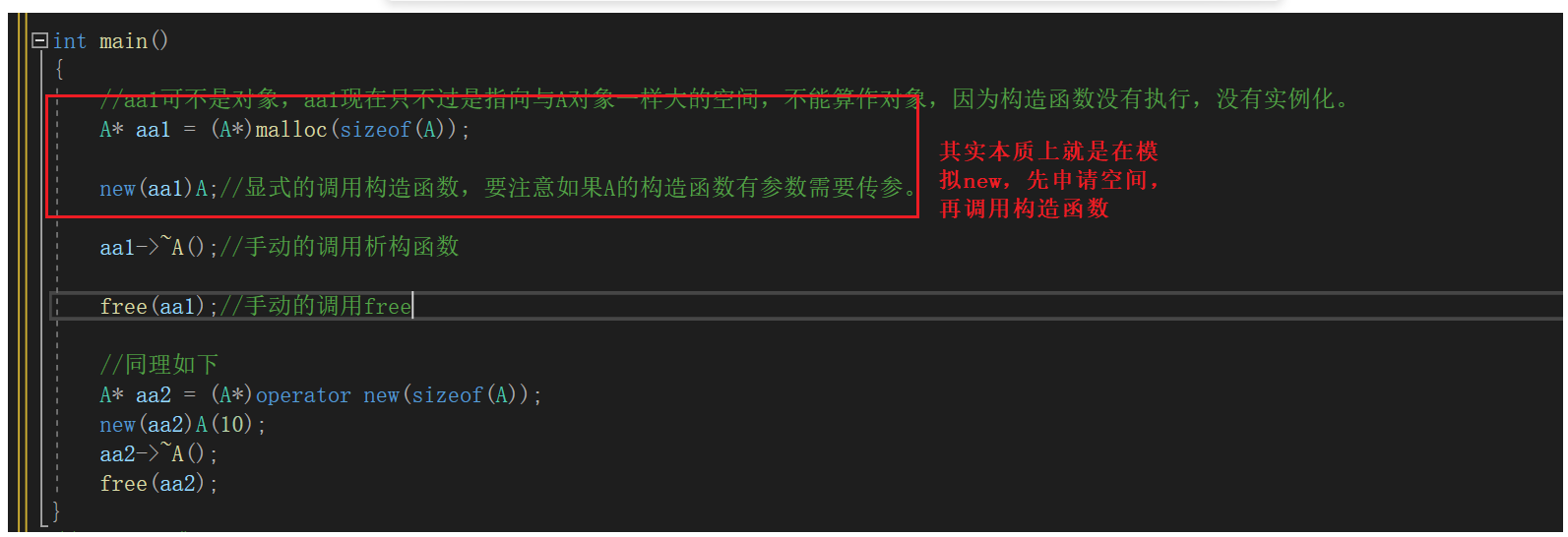

instruction 的decode阶段被写入缓冲区的条目,指令完成的话,向缓冲区写入结果,最早decode的指令(程序顺序)如果没有被标记异常的话,写入reg file

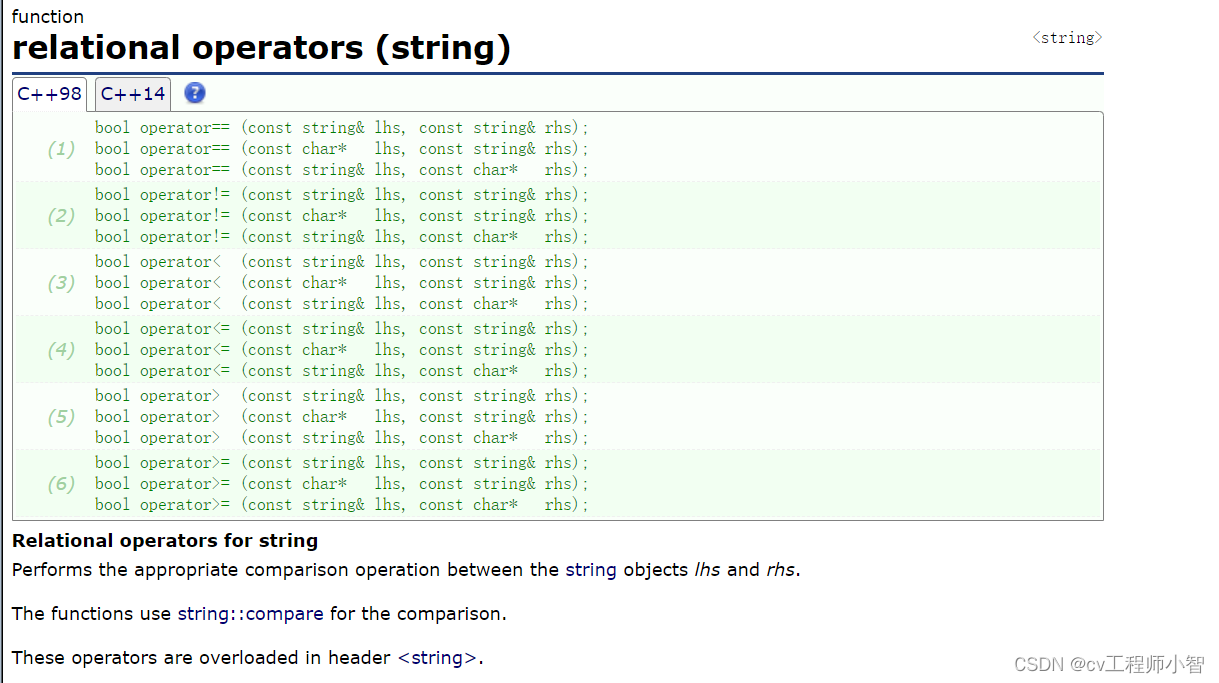

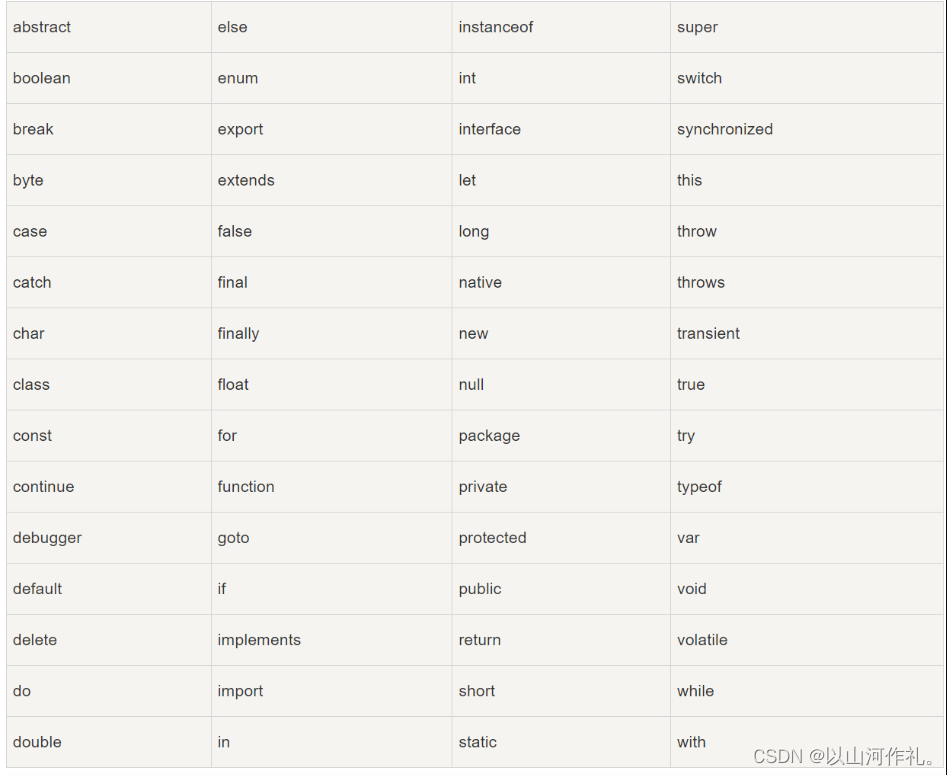

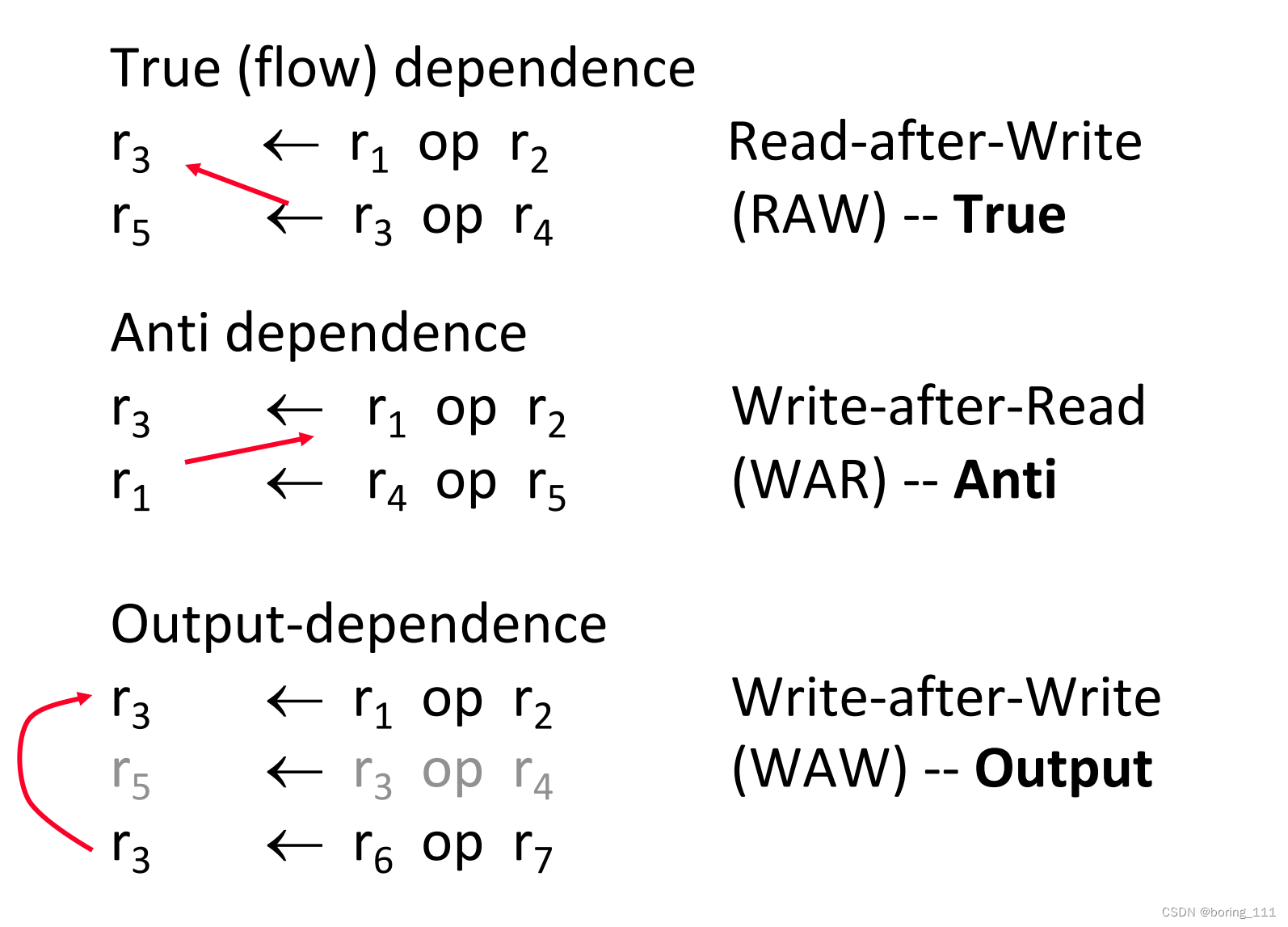

register rename

是为了解决假的冲突,什么是假的冲突呢,请看下面这三个例子

只有第一个是冲突的。 Output and anti dependencies are not true dependencies

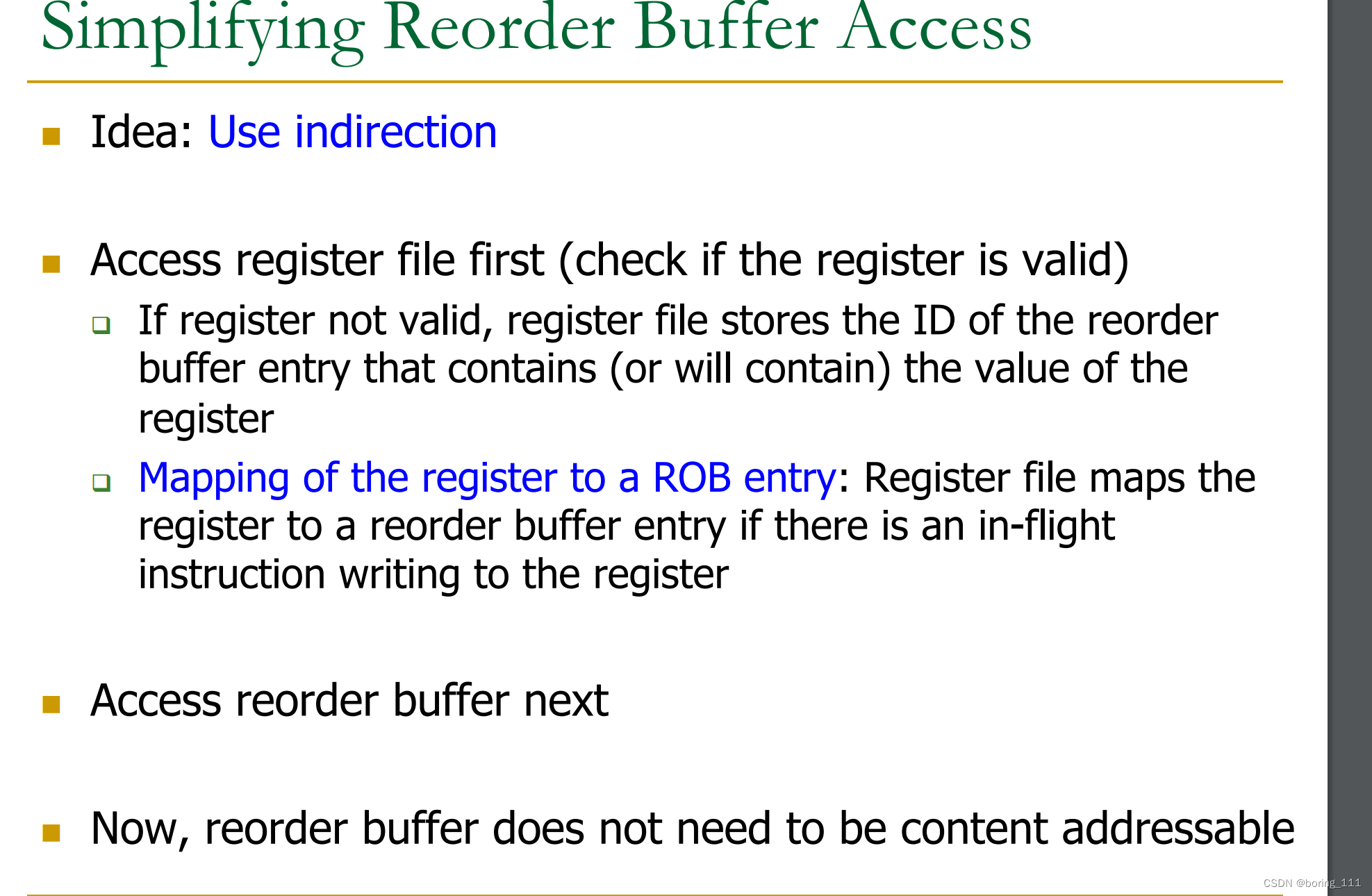

改名可以这样改

Register ID ——》 ROB entry ID Architectural register ID ---》 Physical register ID

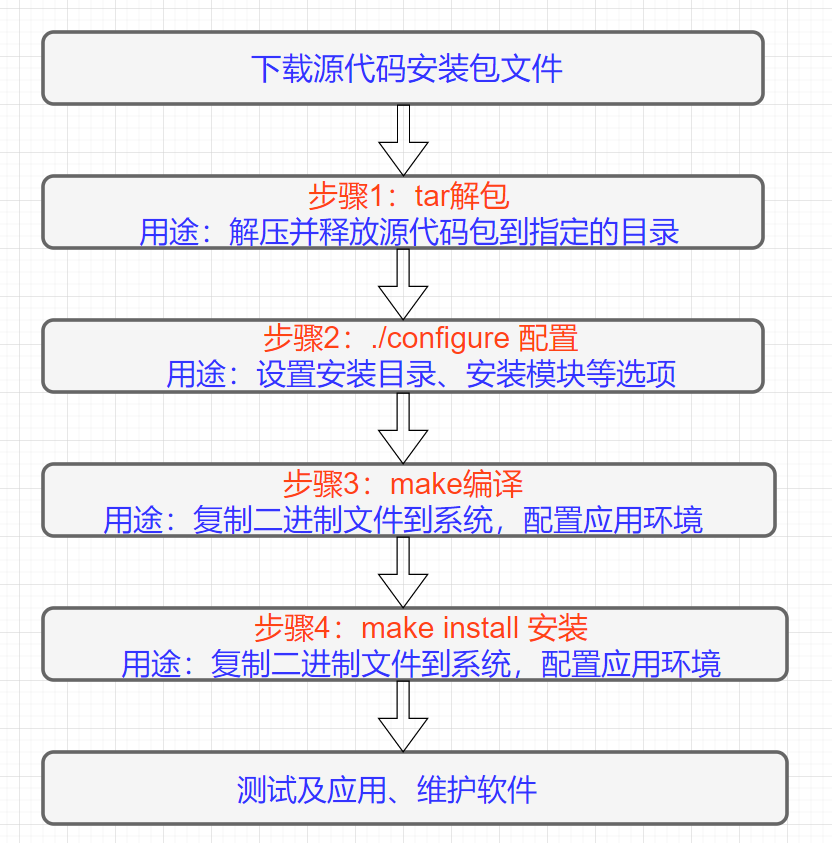

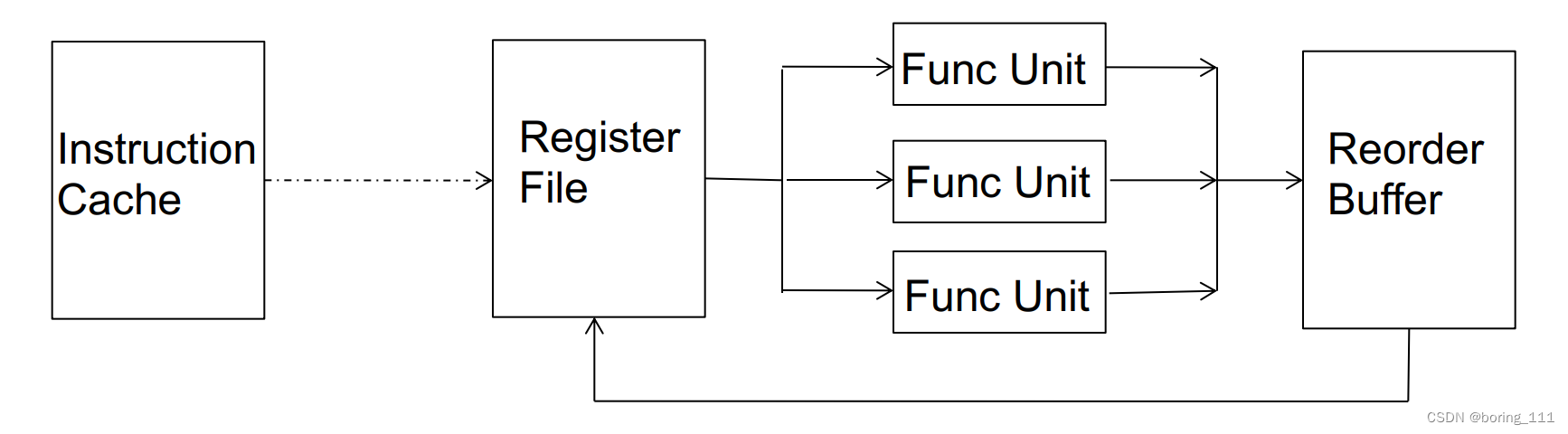

整体流程

Reorder buffer的trade off

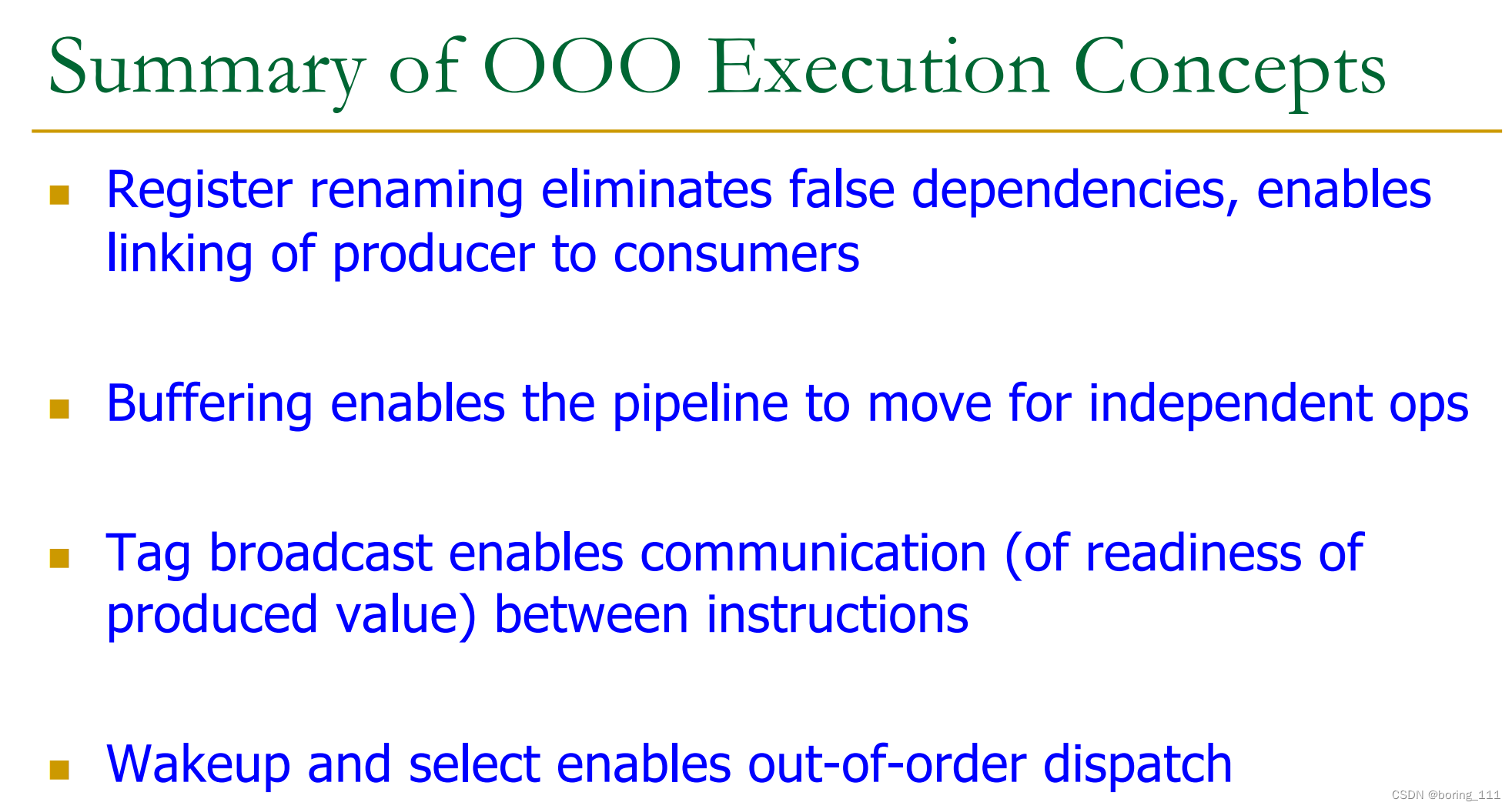

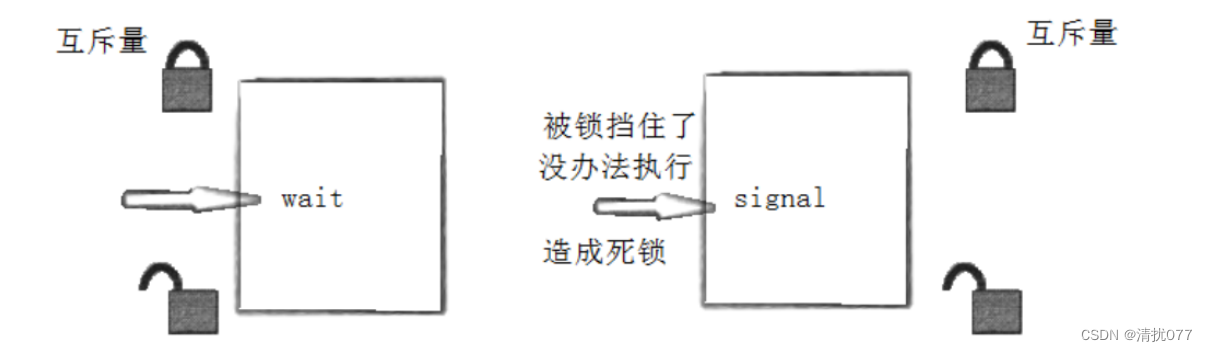

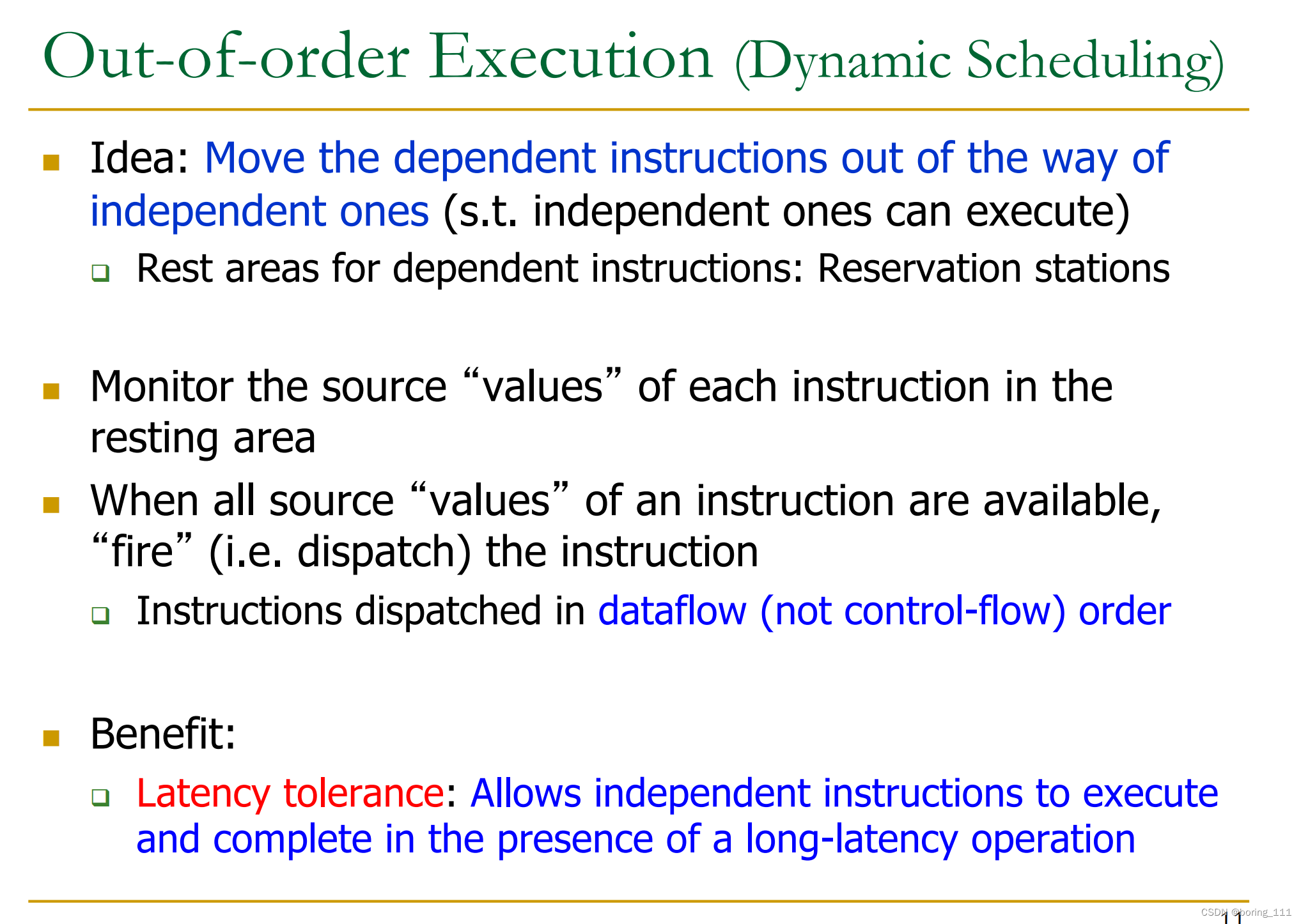

Out of Order Execution

设计初衷

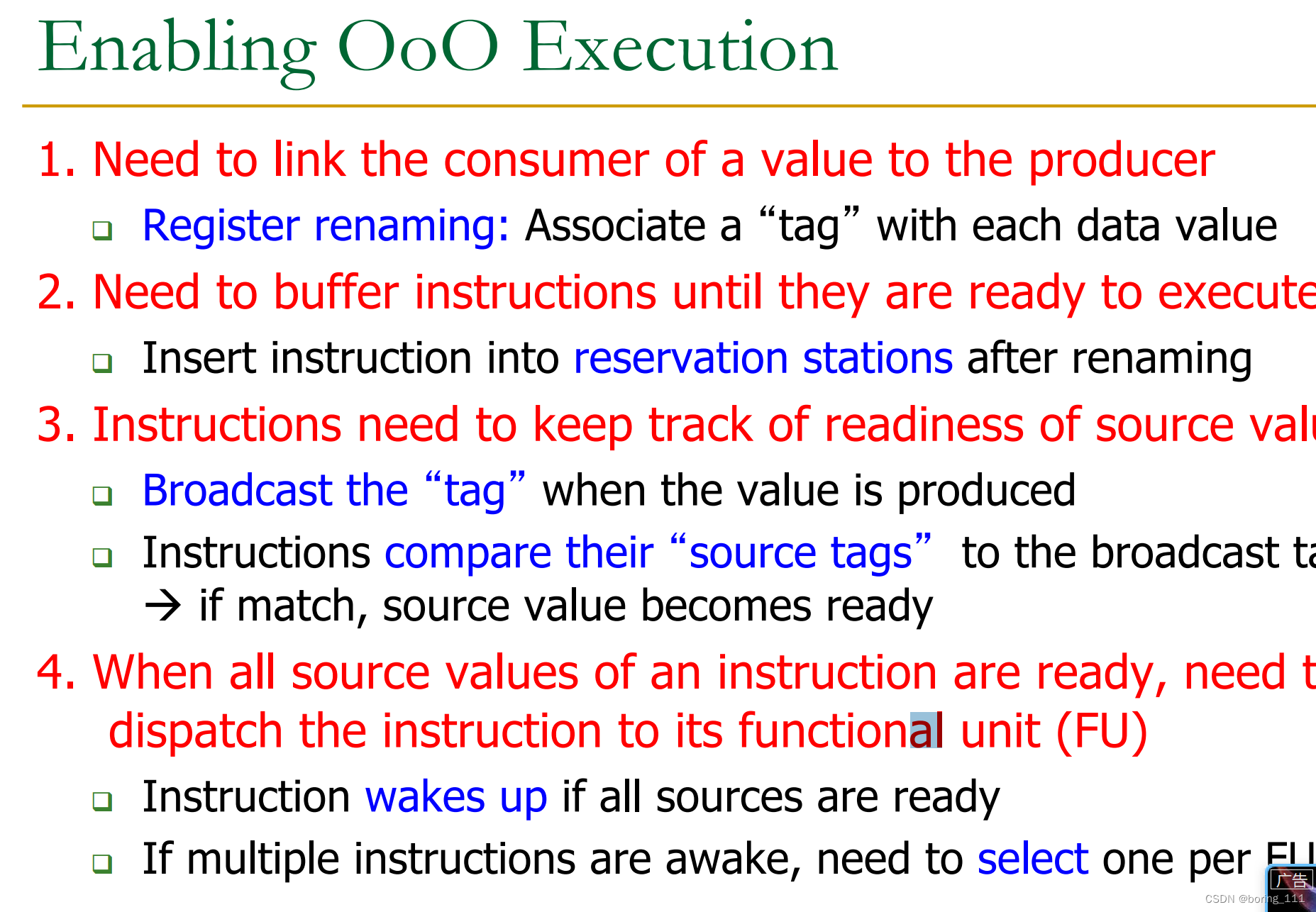

面临的问题,需要做到的事

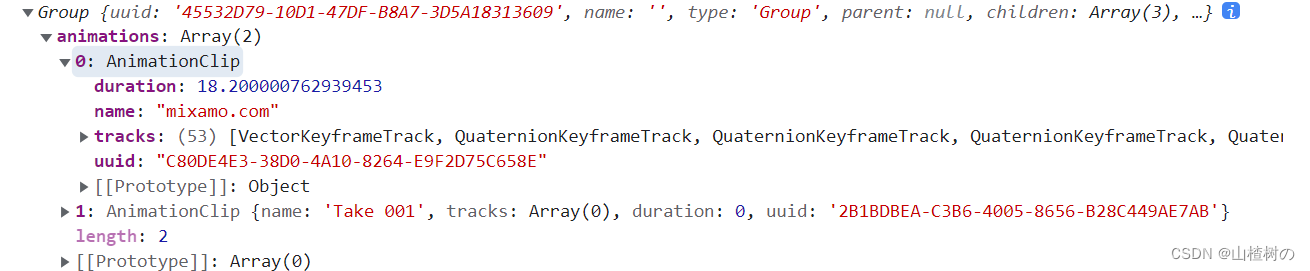

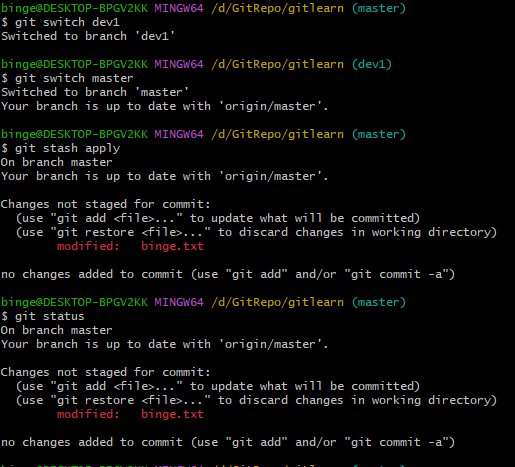

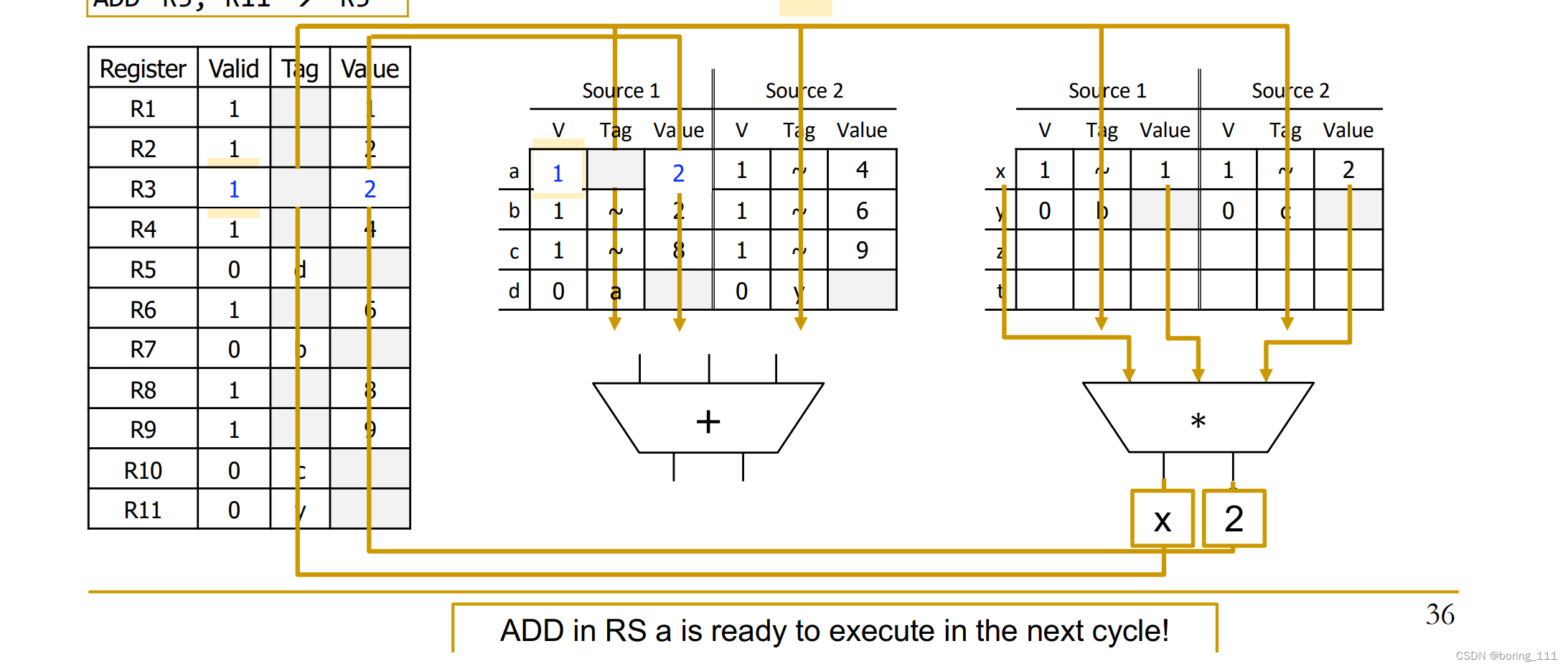

过程

比如r8 + r9 ---> r10 r10在这个指令结束前都不会得到,那么我们就要将valid标记为0,然后tag就是保留站的offset.

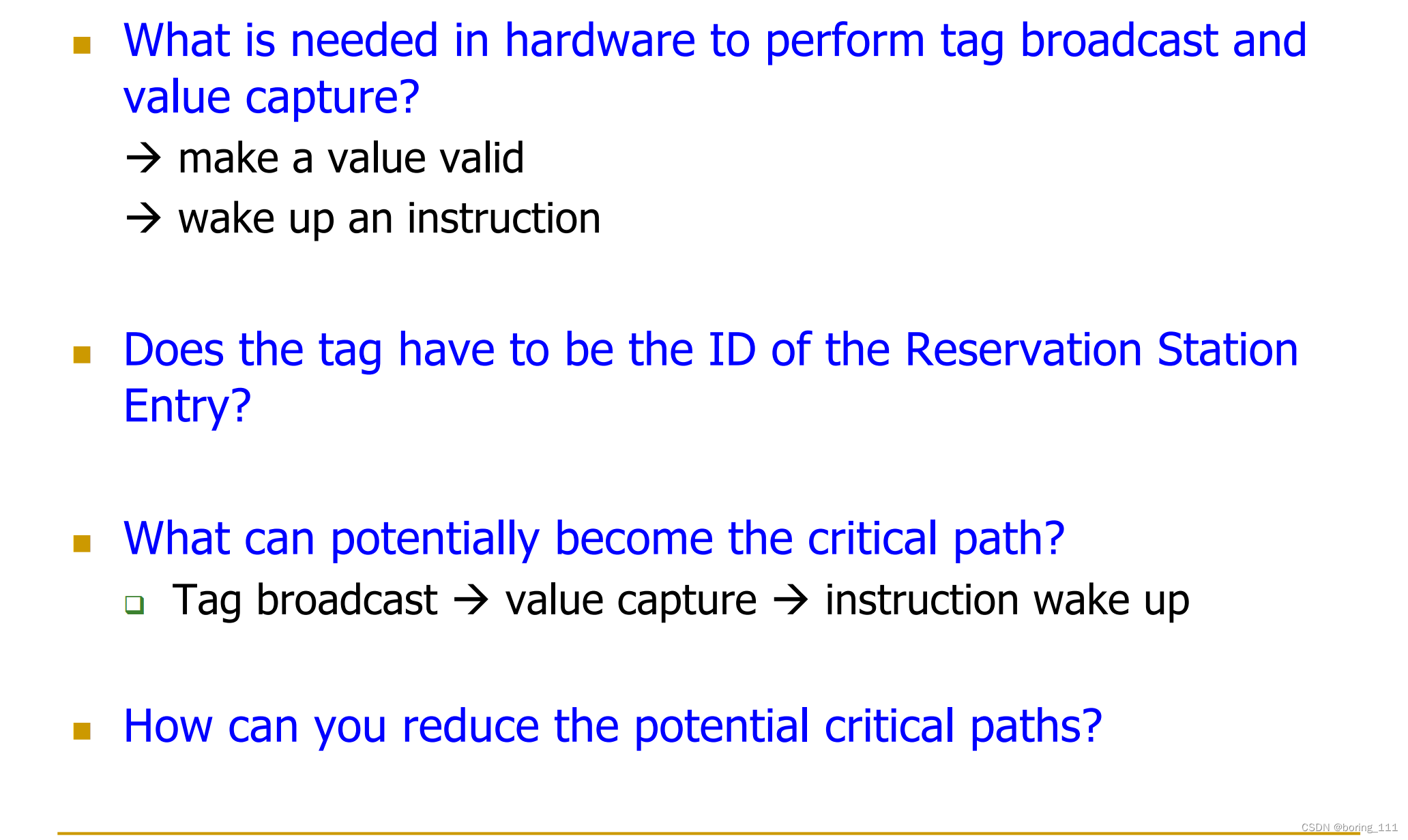

完成的话就broadcast这个tag和value

如果广播后有指令的源reg都valid的话,就wake up这个指令

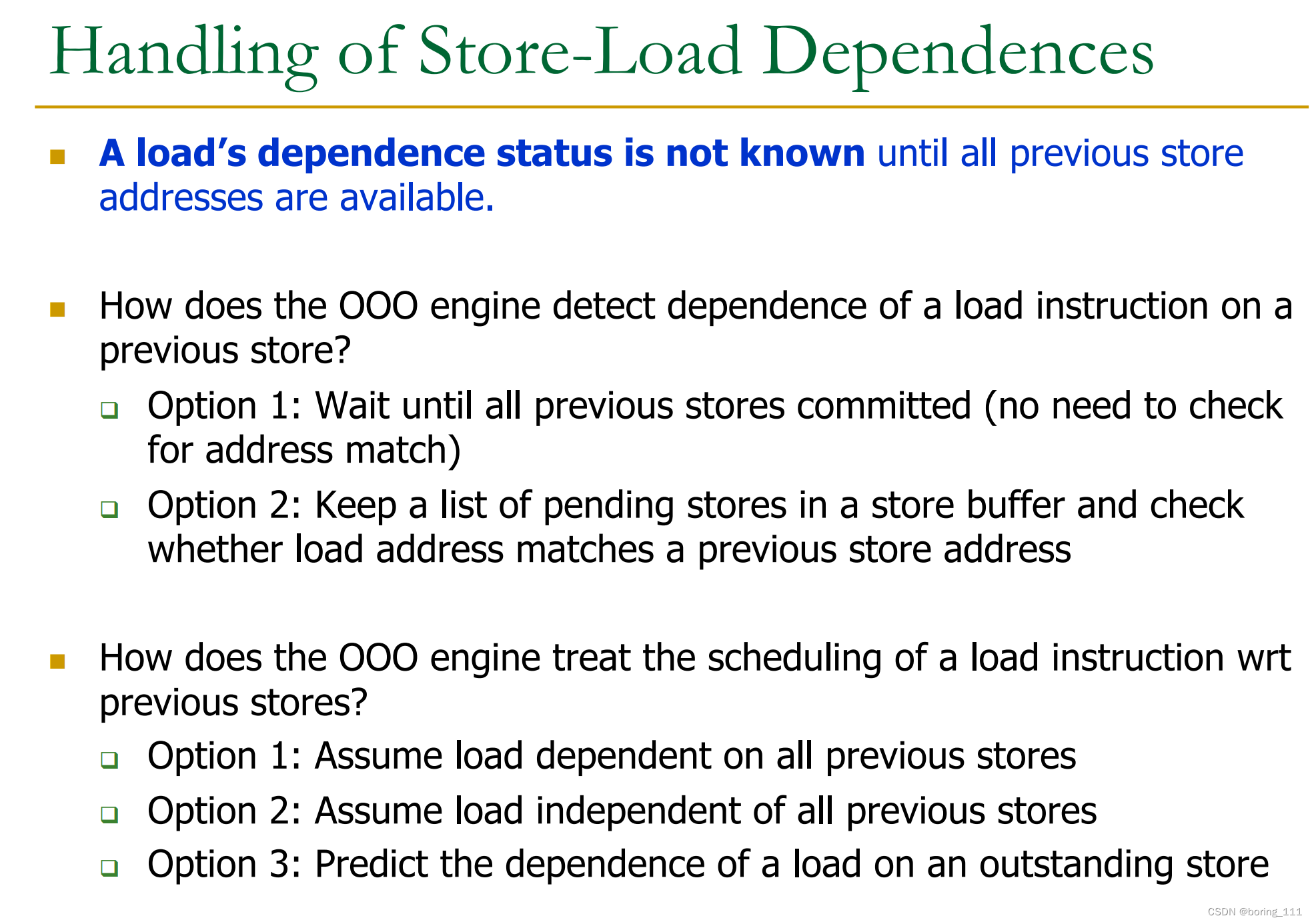

out of order store/load问题

memory很难rename,因为地址太多了,同时在5级流水线中,要aluout作为address,是动态而不是静态的依赖判断

summary