目录

- 贴片电容介绍

- MLCC的制作过程

- 电容失效的头号大敌

- 电容失效的最主要原因

- 电容的容值、耐压值与封装尺寸的关系

- 电容串并联

- 串联

- 并联

- 电容的等效电路

- 选取电容的建议

- 总结

贴片电容介绍

贴片电容相信干电子技术活的基本都使用过,他的全称为:多层片式陶瓷电容器(Multilayer Ceramic Capacitor,MLCC),也称为贴片电容,片容。他的本质作用是储存电荷,至于他在不同的位置有不同的作用和不同的叫法后面老道会总结。

MLCC的制作过程

简单的说MLCC的制作过程就是包括:调制-制片-压缩-切割-烧制-电镀(这是老道自己总结的,实际工艺还是很复杂的)。

- 调制:如同和面一样将主要材料为陶瓷的粉末掺杂其余物质混合在一起。

- 制片:如同制作纸张一样将调制好的陶瓷粉末混合体制作成一张又一张的薄片,同时还会在薄片上印上电极,一张薄片上面有很多分开的小矩形内部电极

- 压缩:在一定的压力和温度下将很多张代用小电极的薄片压缩在一起

- 切割:按照封装大小将压缩好的薄片切割开来

- 烧制:如同烧砖一样将各切割开来的部分烧制成陶瓷

- 电镀:在烧制好的陶瓷两端电镀上将内部电极连接起来且方便焊接的外部电极

说明一下,MLCC可以这样理解。

MLCC的每两层薄片可以看成是一个小的平行板电容器,很多层叠在一起就等于是将很多个相同的平行板电容器并联起来,我们都知道电容并联之后的容值就是每一个部分的容值之和,所以在相同的情况下MLCC的层数越多其容值就越大,至于内部电极与外部电极的链接方式是如下图所示的交错链接。

电容失效的头号大敌

电容失效的最主要原因

电容失效就是电容不起作用了(储存不了电荷了),本质原因是被击穿了,导致击穿的原因有很多,最主要的就是板子发生形变或者受到外界机械力的作用导致电容内部出现了裂缝,这样电容裂缝位置就很容易被击穿从而导致电容失效。

电容的容值、耐压值与封装尺寸的关系

总的来说,当电容达到了一定容值和耐压值他的封装就小不了。哈哈,看似说了又好像什么也没说。

这里举个例子,比如0402封装的电容器。

0402封装的电容器长为40mil宽为20mil,厚度好像是20mil(反正厚度是一个受到约束的定值)。

一方面

从制作过程来看就是将很多片含有内电极的长为40mil宽为20mil的矩形薄片按照一定的间距压缩到厚度为20mil的长方体就形成了0402电容。

再看电容的决定式C=εS/4πkd ,我们只关心S和d,其余参数在制作完成就已经决定了。前面说了MLCC的每两层薄片可以看成是一个小的平行板电容器,我们将这个称为单位电容器吧(为了好理解,老道自己编的名字),由电容的决定式我们知道只要封装尺寸定了,S就不会变了,唯一变化的就是d,而d为两张薄片间的距离,d具体值不得而知,但我们敢肯定他一定有一个最小值,当d为最小值时且薄片的厚度也为最小值时,此时0402封装的电容器就是由最多个单位电容器并联而成的,根据电容并联可知此时的容值为最大,也就是说0402封装的电容的容值存在最大值,一旦超过这个最大值就必须选择更大的封装。

另一方面

由电容的表达式C=Q/U知,当容值一定时,要想耐压值U越大Q就要越大,在材料不变的情况下,对于电容封装尺寸固定了,也就是内电极的尺寸固定了,那电荷Q的最大值也就固定了,要想更多的Q也就只有追求更大的封装尺寸。

总结: 由于贴片MLCC的封装大小限制其容值与耐压值都会有限制,通常来说同一封装的MLCC耐压值和容值如同鱼和熊掌不可兼得,一般容值越大耐压值越低。

电容串并联

我们都知道电容串联增压、并联增容的结果,下面老道详细来说说。

串联

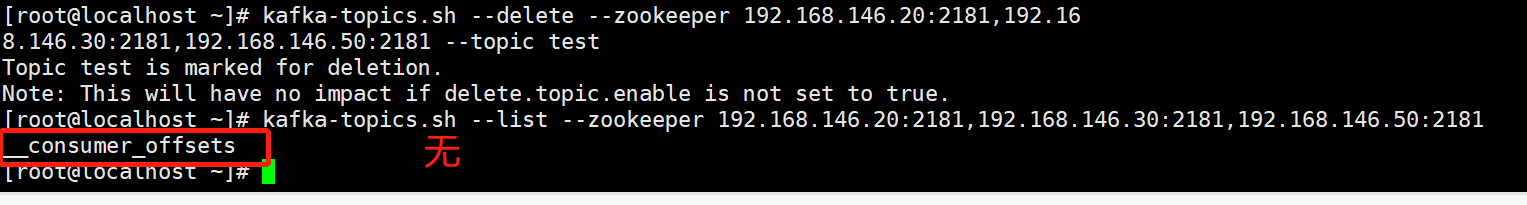

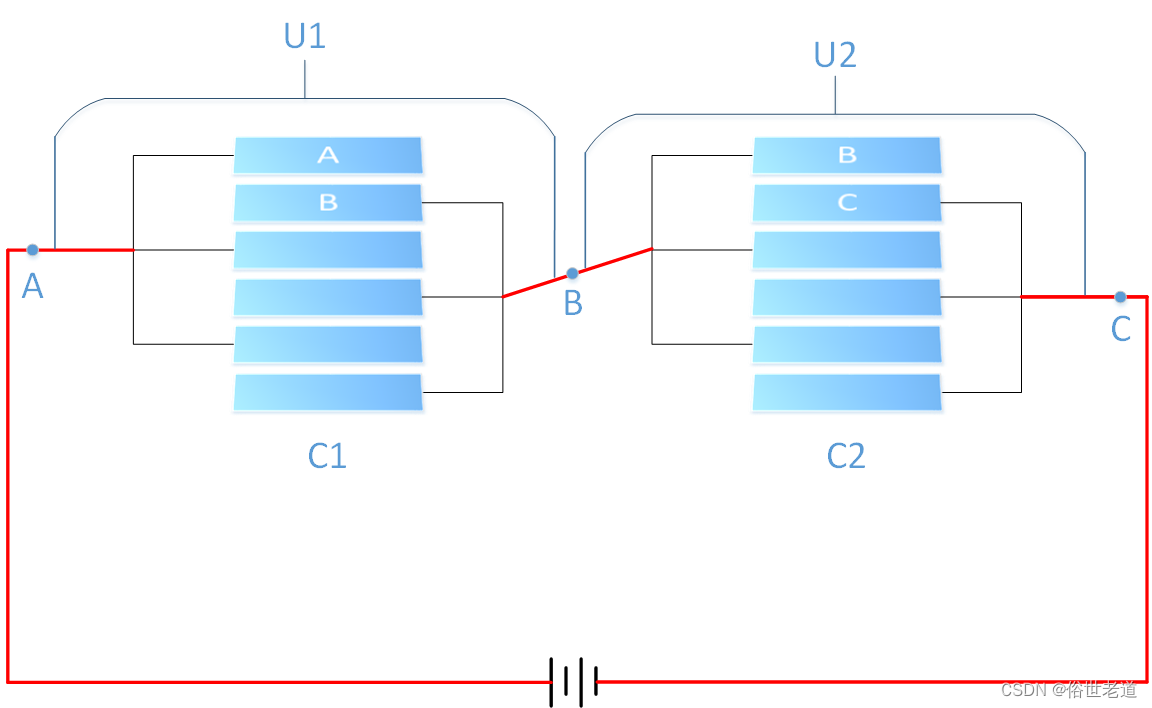

下面是两个电容串联的电路情况:

电容串联的等效容值1/C=1/C1+1/C2 下面老道说说这个等式是怎么推出来的:

我们都知道容抗为1/2πfC,抛开电容的作用不谈,其实电容就是一个阻值随频率f变化的电阻,频率越高阻值越低,即电容的特性阻低频通高频。

在上图的直流电路中C1、C2分得的电压为U1、U2,U1、U2的大小与电容C1、C2的大小成反比。

由电容的决定式C=εS/4πkd可知电容的值在制作完成时就已经决定了,由电容的表达式C=Q/U又知,电容两端的电压与电容的电荷量成正比;在没有串联电容C2之前,电容C1两端的电压为电源电压U,此时对应的电荷量为Q,在串联电容C2之后(假设C1与C2的容值相等,这样好说明一些)电容C1两端的电压为U1,此时对应的电荷量为Q1,根据C1、C2的容值比易知U1=1/2U,Q1=1/2Q。

同理可知C2的的电压U2=1/2U,Q2=1/2Q。

当C1与C2如上图串联起来时,从MLCC内部结构看两个电阻的薄片B被导线连通形成了一张等电势的薄片;将C1、C2看成两个电阻串联,易知道UA>UB>UC,UA即为薄片A的电势,UB即为薄片B的电势,UC即为薄片C的电势。

此时C1与C2可等效为许多个薄片A与C形成的单位电容器并联而成的电容C,薄片A与C上的电荷量均为1/2Q,而薄片A与C的电压仍为电源电压U,根据C=Q/U知,此时的电容C容值变为了C1或C2的一半也即是1/C=1/C1+1/C2,这是一般的结论,在C1、C2为任意值都可用,前面假设C1、C2相等只是为了方便说明。

总结:上方文字有点多,加之老道表述可能不清楚,可能让大家比较迷惑,不过没关系看总结。

多个MLCC串联相当于电阻产生了分压,而对于每个电容而言容值是不可能改变的,由C=Q/U知当U降低那Q也就必然降低,多个MLCC串联可以等效为最上面MLCC的正极性薄片与最下面MLCC的负极性薄片组成了一个新的MLCC,新的MLCC的端电压就等于没有串联之前的MLCC端电压,但电荷Q却降低了,所以新MLCC容值也就降低了,具体满足下面表达式1/C=1/C1+1/C2+…

至于串联增压就是运用了电容的串联分压作用,容易理解原本未串联的电容承受的电压就是电源电压,但当串联其他电容后就有了分压作用,此时承受的电压就小于电源电压了,换句话说就可以对串联后的电容施加更大的电源电压了,但应该注意在电容串联过程中应该注意容值叫小的电容的耐压值,因为容值小的电容分得的电压反而大。

并联

并联相当好理解,因为MLCC本来就是很多个单位电容器并联起来的,多个MLCC并联就相当于并联的单位电容器变多了而已。

并联MLCC的等效容值C=C1+C2+…,多个MLCC并联等效于将每个MLCC的正极性薄片叠加在一起,负极性薄片叠加在一起形成一个新的MLCC,这个新的MLCC端电压不变但薄片上的电荷量却是每个并联的MLCC电荷的叠加,由C=Q/U易知等效的C增加,具体满足C=C1+C2+…

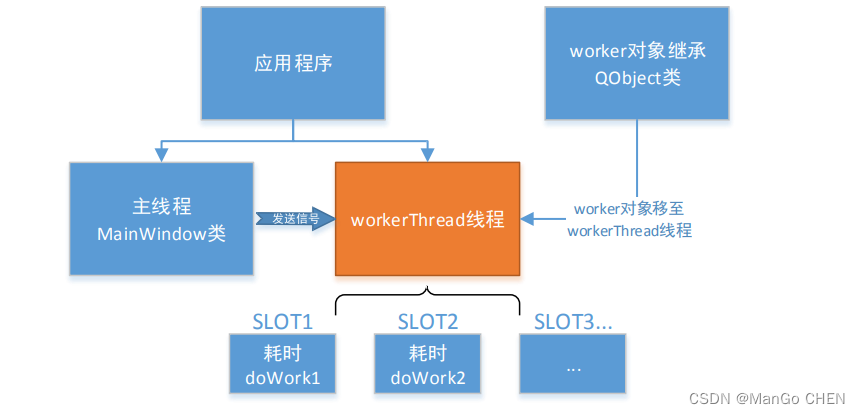

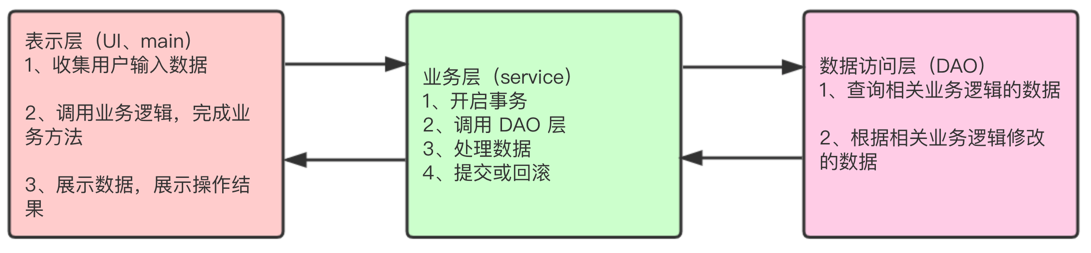

电容的等效电路

电容的等效电路如上图所示:

ESL:等效电感

ESR:等效电阻

C:理想电容

电容有一个重要的参数:谐振频率

- 当工作频率f<fs电容呈容性;

- 当工作频率f=fs电容呈纯阻性;

- 当工作频率f>fs电容呈感性。

通常保证电容的工作频率f远低于fs来确保电容呈容性。

选取电容的建议

第一:在板子的空间没有特殊限制的情况下能选大尺寸的封装不用小尺寸的封装。

一方面因为当容值与耐压值一定时,大封装的电容器的薄片更厚,当板子形变时这样更不容易形成裂纹。但应注意大封装的电容不推荐使用手工焊,因为封装大更容易出现受热不均的问题,可能导致电容出现裂纹,如果使用手工焊,最好提前将电容预热,焊接时间也不宜过长。另一方面在板子维修时更换小封装的阻容十分不方便。

第二:电容的工作温度至少要比限制温度低上10-15℃。

第三:电容的耐压值选取要考虑余量。

①一般情况下降额到70%使用;

②关键或军工等重要场合降额到50%-60%使用;

③大功率、低阻抗按降额到30%使用。

第四:如果板子的工作环境容易发生形变可以选取柔性材料制作的电容,能够很好的预防裂纹的出现。

第五:

- Ⅰ类瓷介电容高频特性好,稳定性高,但容值不会太高通常不到10uf

常用于10M-300MHz - Ⅱ类瓷介电容低频特性好,容值随温度变化大,容值能达到100uf

常用于1K-10MHz

总结

随着集成电路的发展,MLCC的应用越来越广泛,随着集成电路的集成度进一步提高,MLCC的体积可能会越来越小,而MLCC的容值和耐压值的的大小受到其体积的限制(至少在目前材料没有突破的前提下,可以这样认为),但我们可以通过MLCC的串并联来增加耐压值和容值。

在pcb layout时应特别注意电容器的位置,尽量远离会受机械冲击的连接器和容易发生形变的区域。

备注:小白理解,不喜勿喷,欢迎大家批评指正