2.2 加入factory 机制

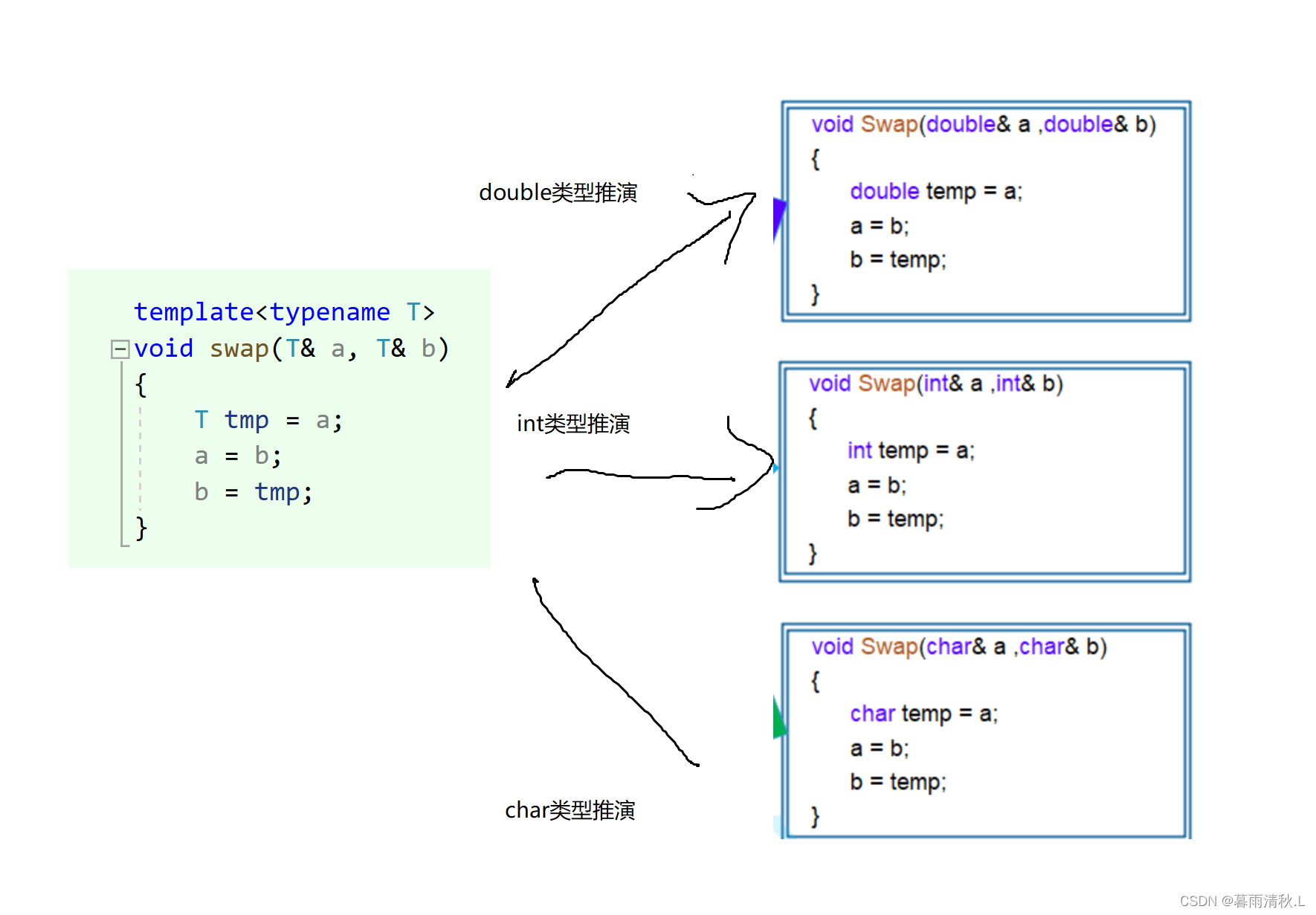

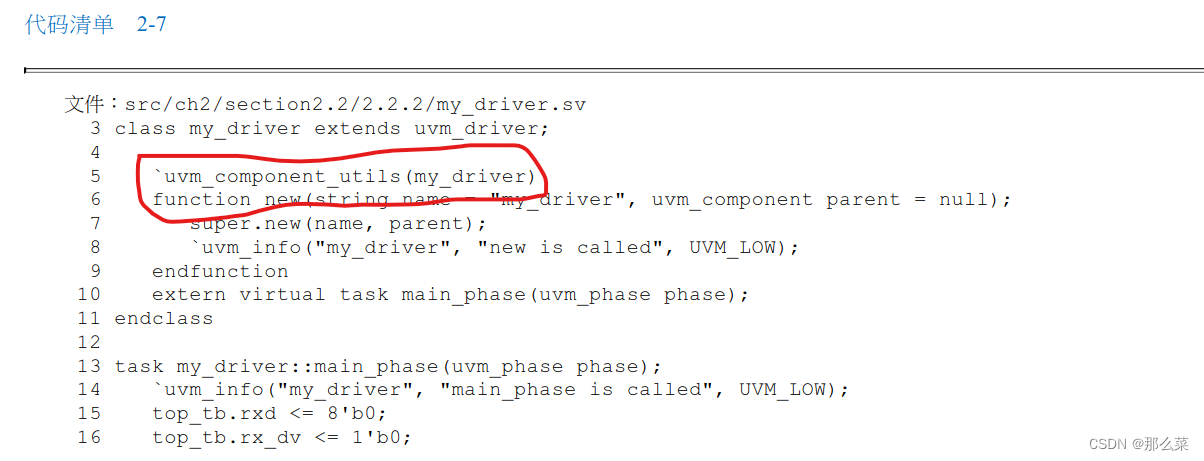

factory机制的实现被集成在了一个宏中:uvm_component_utils。这个宏所做的事情非常多,其中之一就是将my_driver登记在 UVM内部的一张表中,这张表是factory功能实现的基础。只要在定义一个新的类时使用这个宏,就相当于把这个类注册到了这张表中。那么factory机制到底是什么?这个宏还做了哪些事情呢?

我们对它的初次印象就是:通过uvm_component_utils该宏定义的类,都会通过传入一个字符串自动创建一个类,并自动调用其中的function 和 task

定义好该类,并通过uvm_component_utils 宏注册后,就可以更改TB,如下:

文件:src/ch2/section2.2/2.2.2/top_tb.sv

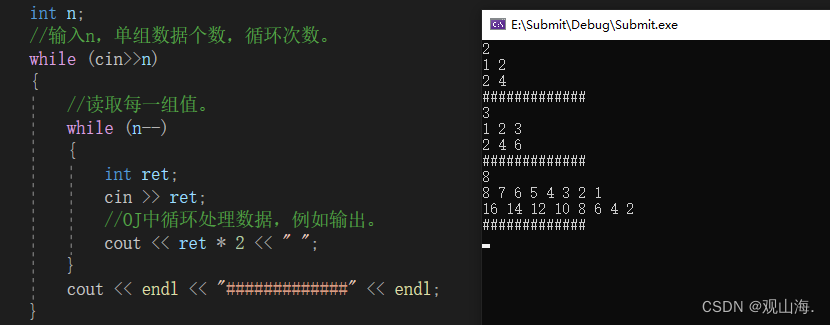

7 module top_tb;

…

36 initial begin

37 run_test("my_driver");

38 end

39

40 endmodule一个run_test语句会创建一个my_driver的实例,并且会自动调用my_driver的main_phase。仔细观察run_test语句,会发现传递给 它的是一个字符串。UVM根据这个字符串创建了其所代表类的一个实例。

除了根据一个字符串创建类的实例外,上述代码中另外一个神奇的地方是main_phase被自动调用了。在UVM验证平台中,只 要一个类使用uvm_component_utils注册且此类被实例化了,那么这个类的main_phase就会自动被调用。

2.3 加入 objection 机制

在上一节中,虽然输出了“main_phase is called”,但是“data is drived”并没有输出。而main_phase是一个完整的任务,没有理由 只执行第一句,而后面的代码不执行。看上去似乎main_phase在执行的过程中被外力“杀死”了,事实上也确实如此。

UVM中通过objection机制来控制验证平台的关闭。细心的读者可能发现,在上节的例子中,并没有如2.2.1节所示显式地调用 finish语句来结束仿真。但是在运行上节例子时,仿真平台确实关闭了。在每个phase中,UVM会检查是否有objection被提起 (raise_objection),如果有,那么等待这个objection被撤销(drop_objection)后停止仿真;如果没有,则马上结束当前phase。

加入了objection机制的driver如下所示:

文件:src/ch2/section2.2/2.2.3/my_driver.sv

13 task my_driver::main_phase(uvm_phase phase);

14 phase.raise_objection(this);

15 `uvm_info("my_driver", "main_phase is called", UVM_LOW);

16 top_tb.rxd <= 8'b0;

17 top_tb.rx_dv <= 1'b0;

18 while(!top_tb.rst_n)

19 @(posedge top_tb.clk);

20 for(int i = 0; i < 256; i++)begin

21 @(posedge top_tb.clk);

22 top_tb.rxd <= $urandom_range(0, 255);

23 top_tb.rx_dv <= 1'b1;

24 `uvm_info("my_driver", "data is drived", UVM_LOW);

25 end

26 @(posedge top_tb.clk);

27 top_tb.rx_dv <= 1'b0;

28 phase.drop_objection(this);

29 endtask读者可以简单地将drop_objection语句当成是finish函数的替代者,只是在drop_objection语句之前必须先调用 raise_objection语句,raise_objection和drop_objection总是成对出现。

raise_objection语句必须在main_phase中第一个消耗仿真时间的语句之前。如$display语句是不消耗仿真时间的,这些语句可以放在raise_objection之前,但是类似@(posedge top.clk)等语句是要消耗仿真时间的。按照如下的方式使用raise_objection是无法 起到作用的:

task my_driver::main_phase(uvm_phase phase);

@(posedge top_tb.clk);

phase.raise_objection(this);

`uvm_info("my_driver", "main_phase is called", UVM_LOW);

top_tb.rxd <= 8'b0;

top_tb.rx_dv <= 1'b0;

while(!top_tb.rst_n)

@(posedge top_tb.clk);

for(int i = 0; i < 256; i++)begin

@(posedge top_tb.clk);

top_tb.rxd <= $urandom_range(0, 255);

top_tb.rx_dv <= 1'b1;

`uvm_info("my_driver", "data is drived", UVM_LOW);

end

@(posedge top_tb.clk);

top_tb.rx_dv <= 1'b0;

phase.drop_objection(this);

endtask2.4 加入virtual interface

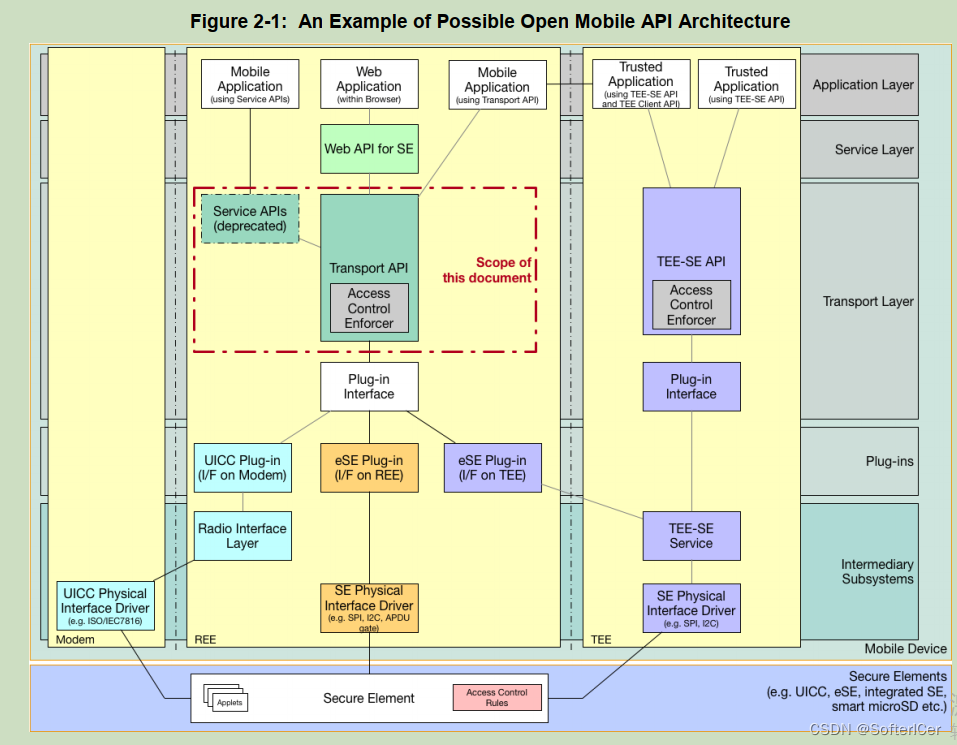

在SV 验证平台及UVM 验证平台风风火火的今天,interface 作为 验证和设计之间的桥梁,发挥了至关重要的作用。在之前的文章,已经讲的很清晰,大家可以参考如下系列文章。

UVM 验证方法学之interface学习系列文章