本项目基于VU9P(xcvu9pflga2105)板卡以及ZYNQ(xc7z015clg485)

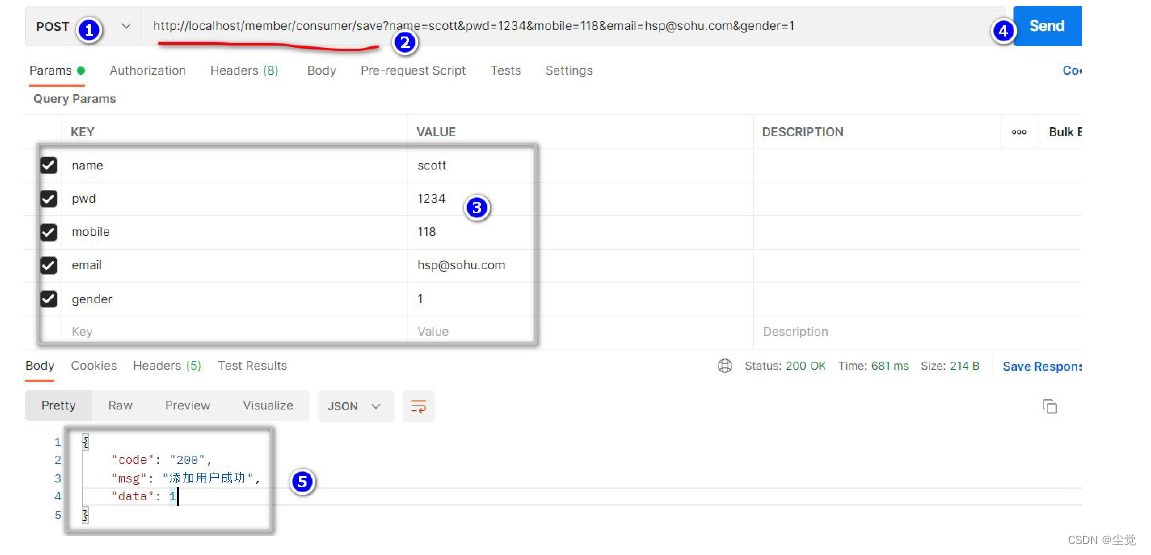

简单结构流程介绍:

1.上位机通过千兆网将指令下发到ZYNQ,ZYNQ进行解帧,将数据解析出来后存储到RAM中,RAM将数据不断输送给GPIO模块,GPIO模块根据对应地址输出数据是否变化来判断是否发送数据给到VU9P。

2.千兆网使用的RGMII接口,通过例化vivado官方的ip核,在ip核例程中对用户层逻辑进行修改(处理mac层数据进行解帧)暂时不介绍千兆网工程,后续单独介绍。

3.ZYNQ与VU9P之间使用16根GPIO线进行通信,采用类似spi模式,一根线作为片选信号,一根线作为时钟线,5根线作为地址线,8根线作为数据线进行传输,一根线作为从机反馈线。

4.上位机下发数据位宽为32bit,gpio模块四个时钟发送完毕

RTL图:

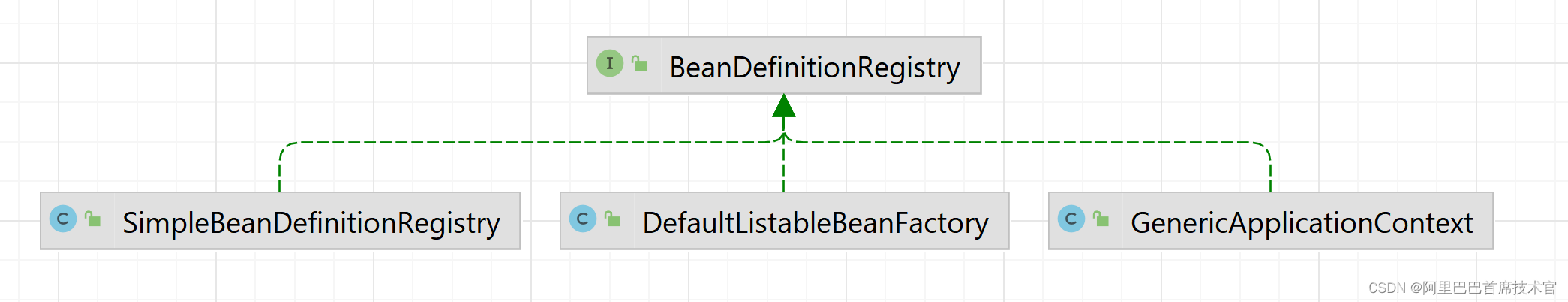

1.其中channel模块用来检测输入数据变化情况,当四路数据有任何一路发生变化,channel模块会对数据进行处理,再高5位添加上地址位,并拉高一个时钟的data_en,即数据有效信号,并将地址+数据送到master主机模块中

2.主机对数据进行分解,将地址用5根线进行输出,数据用8根线进行输出,同时输出片选以及时钟信号给到slave从机模块

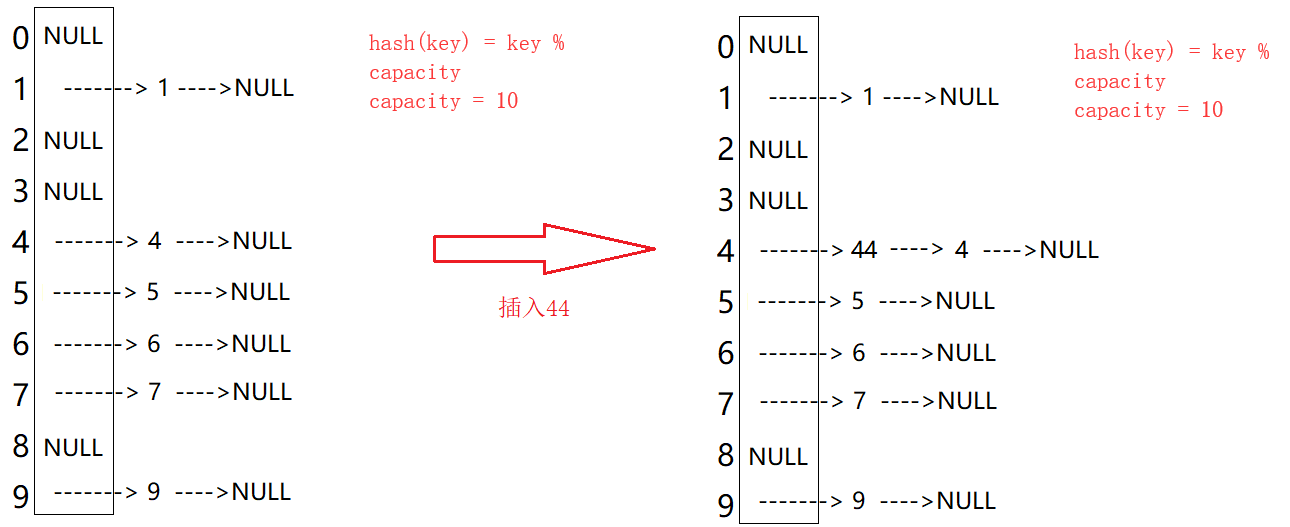

3.从机模块接收到数据以及地址后,对数据进行拼接,将地址以及数据存储到RAM中

4.VU9P根据RAM中的数据指令进行其他操作。

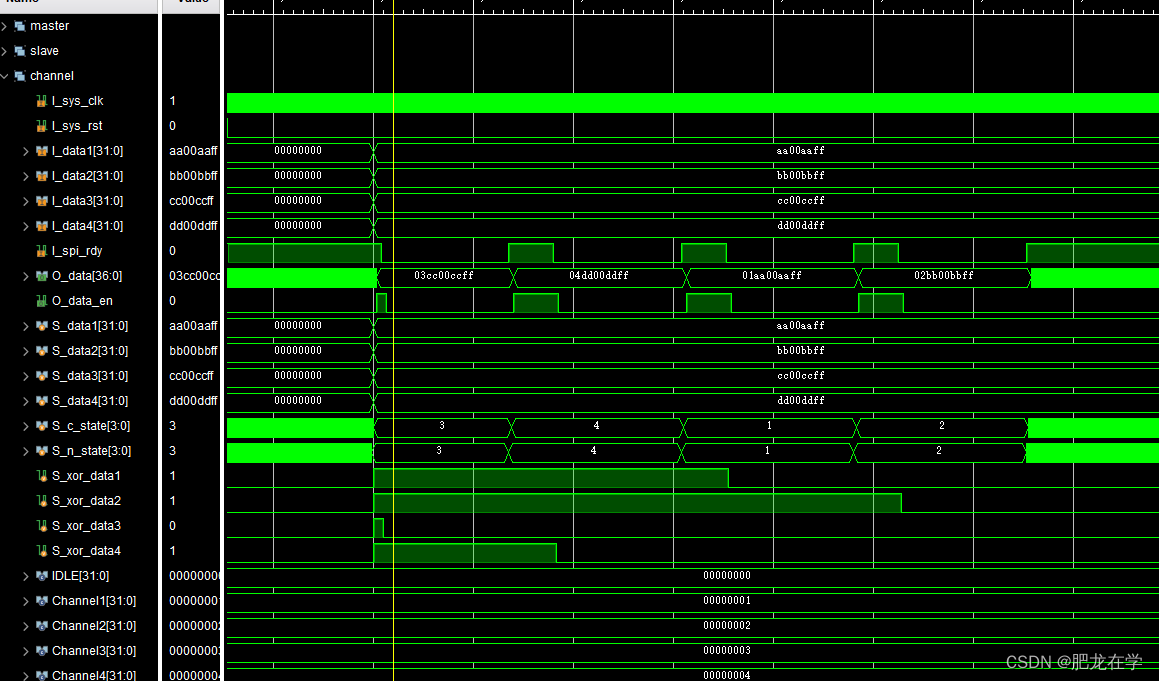

仿真:

四个通道在3000ns同时发生变化。

channal模块检测数据变化情况,虽然四路数据同时变化,但channal模块会自动对数据进行排序,分别进行传输,且将地址加到数据高5位,输出数据位宽位37位

主机对数据进行分解后发送给从机。

从机接收到16路gpio信号后对信号进行拼接,每拼接一个字节拉高ram写使能,将数据存储到对应的地址中。

bram仿真结果(输入):

bram仿真结果(输出):(地址循环,数据循环输出)

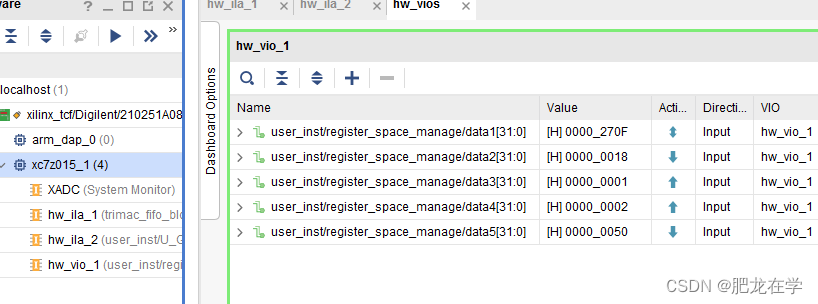

上板:

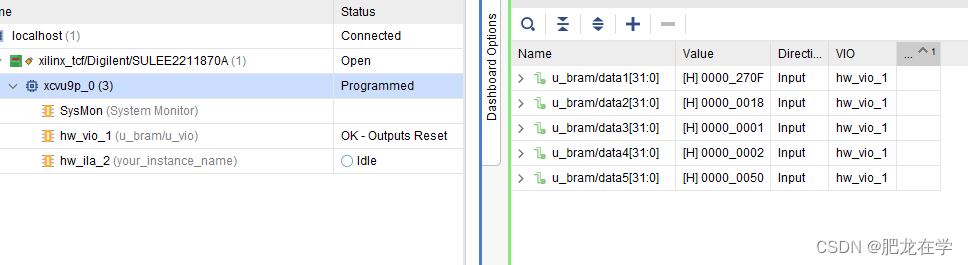

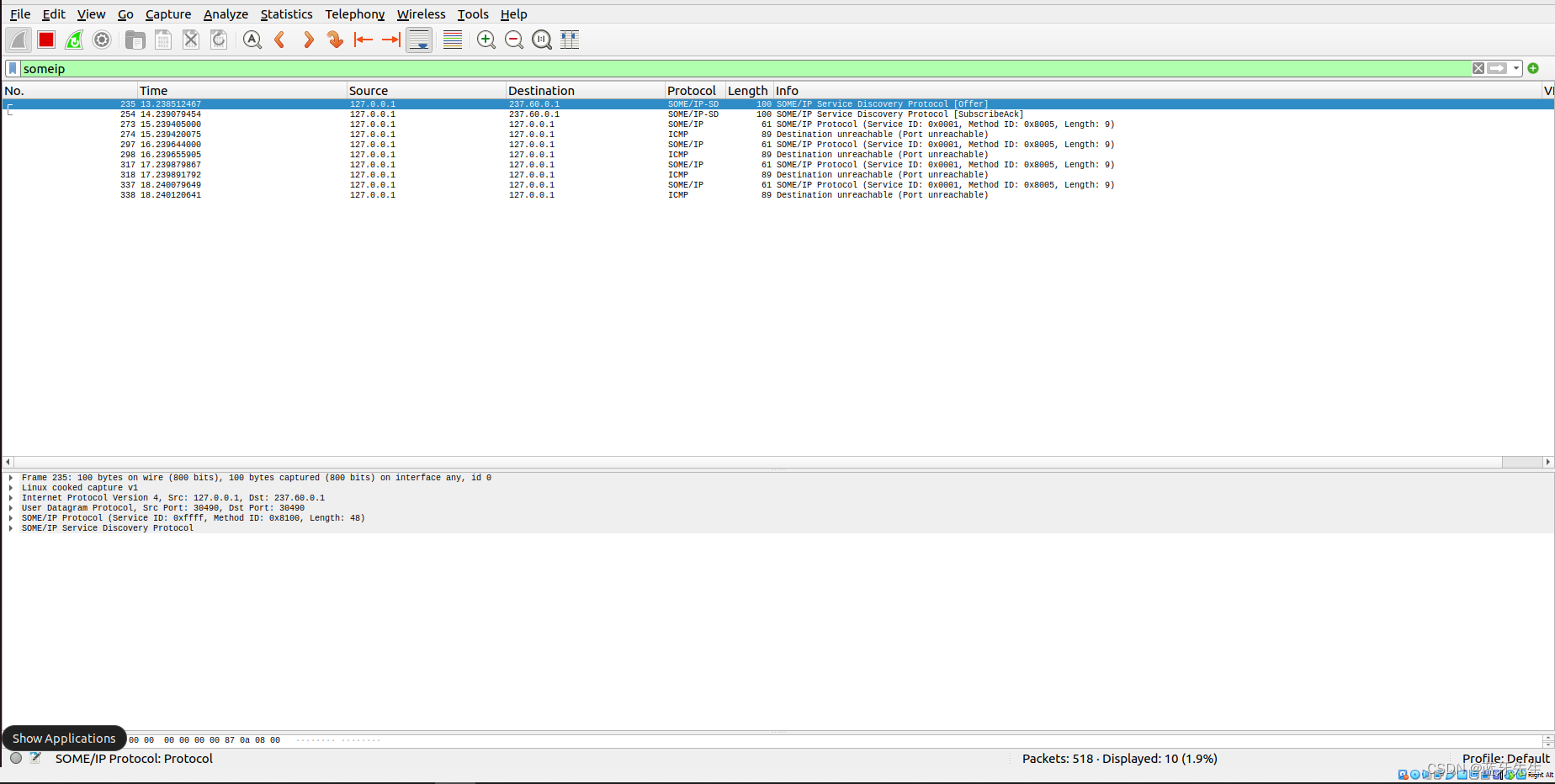

仿真过程模拟的主机和从机,上板时候要将主机从机分开,主机工程在ZYNQ,从机功臣在VU9P,通过上位机发送指令给到ZYNQ,在ZYNQ上用vio观测数据变化情况,同时在VU9P上同样使用vio观测数据接收情况。

ZYNQ:

VU9P: