目录

1.中断基本概念

2.中断的意义

3.中断处理过程

4. 中断体系结构

5.NVIC

6.EXTI

1.中断基本概念

在处理器中,中断相当于对于突发事件的处理过程。

当遇到内部/外部的紧急事件需要处理时,暂时中止当前程序,转而去处理紧急事件,

待处理完毕后,再返回被打断的程序继续向下运行。

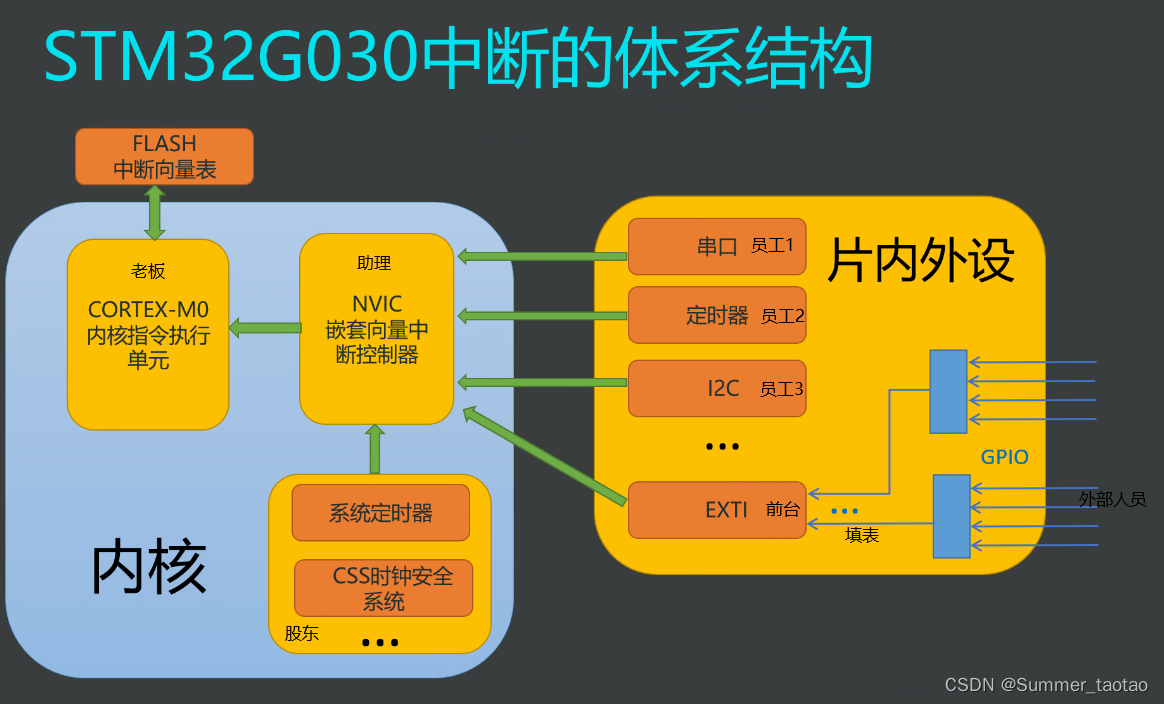

(NVIC在内核里)

2.中断的意义

中断能够对突发事件进行及时处理,实现程序的并行化,进而提高CPU的工作效率。

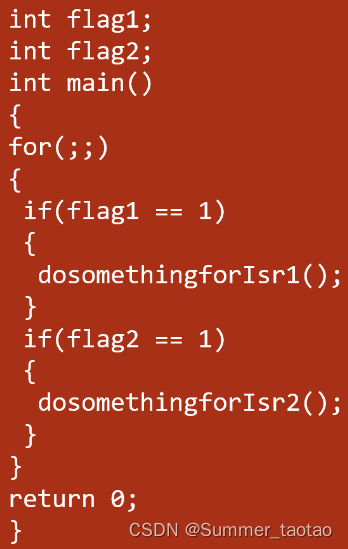

//为什么提高效率了?

因为CPU对于没有发生的事情是在不停的在轮询(询问有没有发生?)

3.中断处理过程***

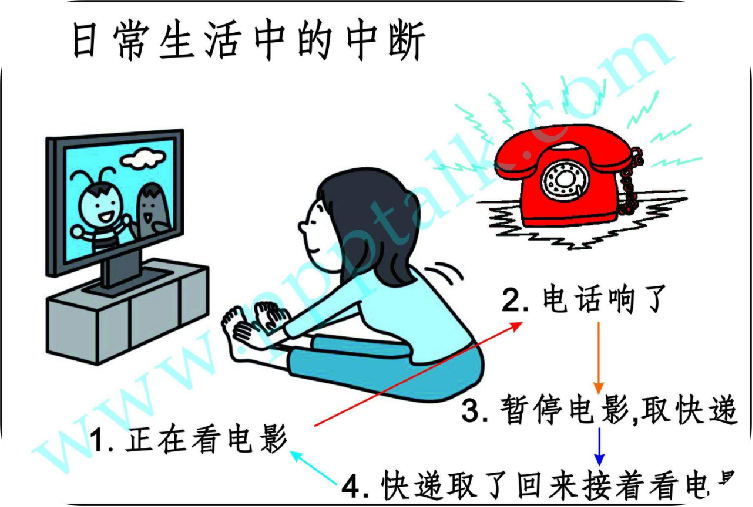

示例:

1.看电影---正在执行的主程序

2.来电话---中断信号

3.暂停电影---压栈,把变量压进栈里

4.取快递---处理中断事件(中断处理函数)

5.继续看电影---出栈

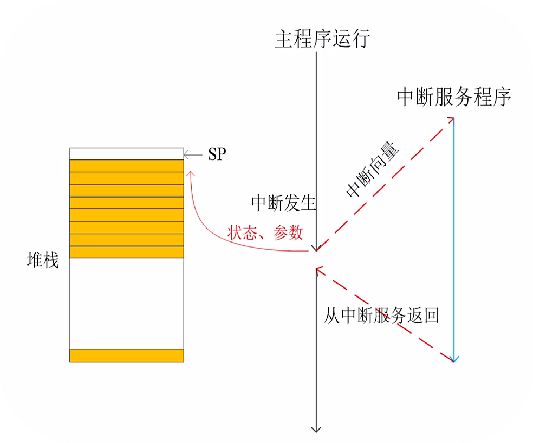

中断处理过程:

进入中断

处理器自动保存现场到堆栈里

{PC, xPSR, R0-R3, R12, LR}

一旦入栈结束,ISR便可开始执行

退出中断

中断前的现场被自动从堆栈中恢复

一旦出栈完成,继续执行被中断打断的指令

出栈的过程也可被打断,使得随时可以响应新的中断而不再进行现场保存

R0 - R12

R13 栈指针 SP : 指向栈顶地址

R14 链接寄存器 LR :存放返回地址

R15 程序计数器 PC :保存要执行的指令地址

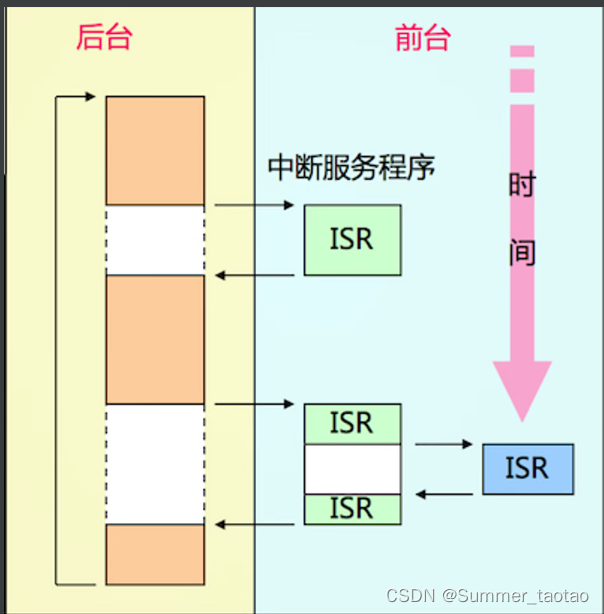

中断做多任务不可避免的

前后台系统

4. 中断体系结构

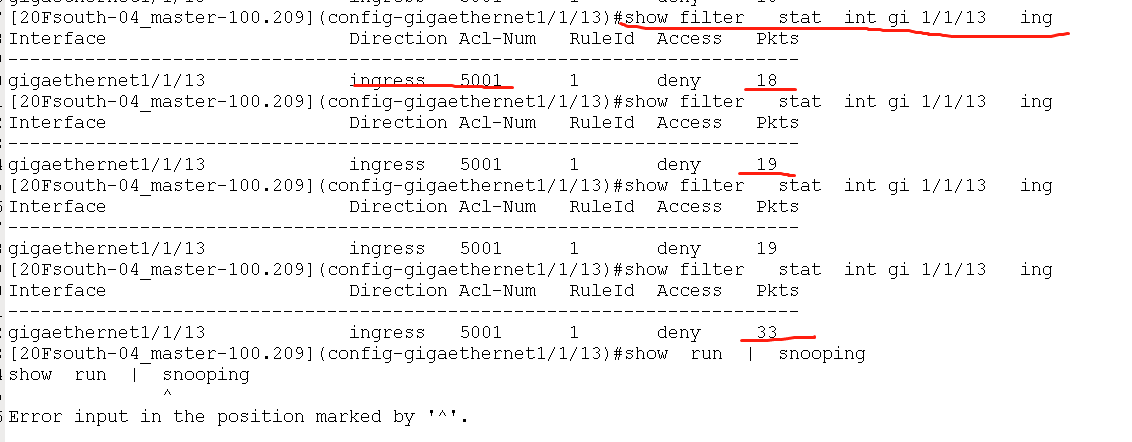

5.NVIC

嵌套向量中断控制器(Nested Vectored Interrupt Controller)

NVIC主要功能

负责管理中断 (CPU的小助理)

1)管理中断事件

每一个中断事件都有执行或禁止两种状态,由NVIC负责将中断事件标记为清除和挂起两种状态。

(当多个中断事件同时到达时,NVIC会优先处理优先级更高的事件)

(当中断执行完成时,NVIC会将中断事件置为清除状态)

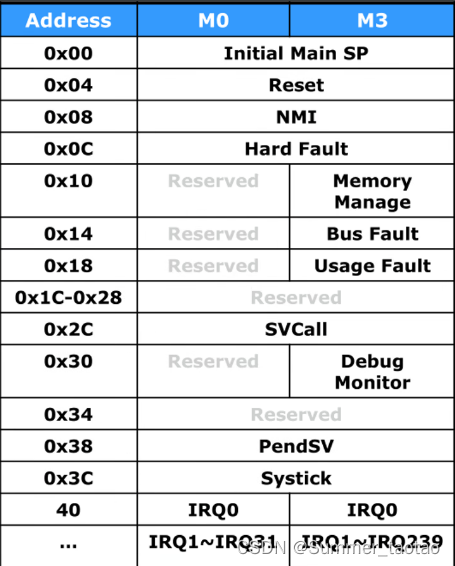

2)支持中断向量化处理

当中断事件发生时,处理器会将PC置为中断事件入口函数的地址,进而跳转到中断服务程序去执行,这就是个中断(异常)向量,因为每一个异常源或者中断事件都会对应一个服务程序的入口地址,将这些地址按照优先级进行排布后,组成的一张表就称为中断(异常)向量表。

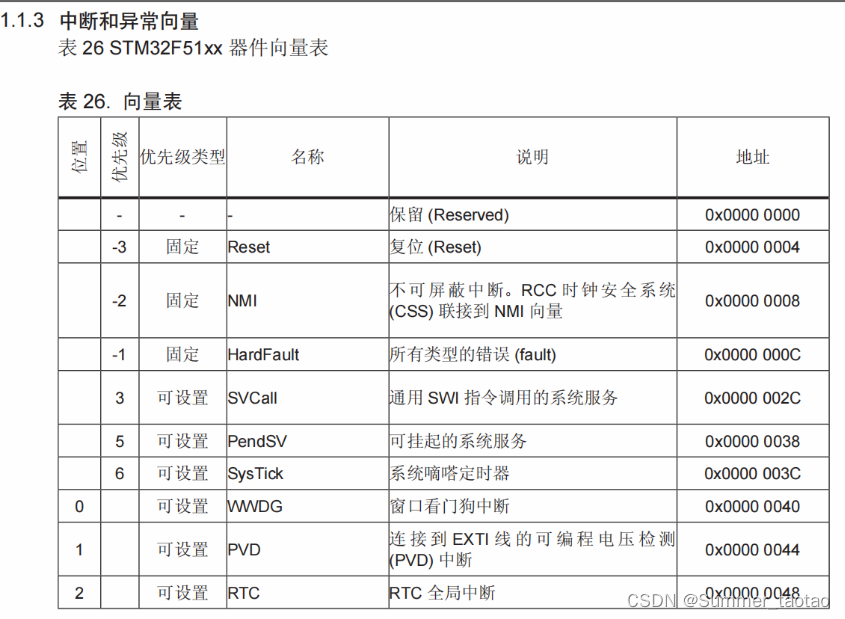

中断和异常向量表:存在FLASH里,本质是中断函数的地址,内核里面叫异常,内核外面叫中断

有优先级,数越小越大,除此又可以编辑的

Cortex-M0内核 可以处理15个内部异常和32个外部中断

STM32G030 只使用了6个内部异常和28个外部中断

3)支持中断嵌套

STM32的功能,与优先级有关

3个固定的优先级,都是负值,不能改变。

四个可编程优先级,用两个bit位表示,00,01,10,11

优先级数值越小,优先级等级越高。

注意

不同优先级的中断同时发生,优先处理优先级编号较小的那个

同样优先级的中断同时发生,中断向量号较小的那个优先响应

6.EXTI

外部事件/中断控制器

主要功能:

一个功能是产生中断,另一个功能就是产生事件。

产生中断的目的,是将信号送入NVIC,进而运行中断服务程序,实现对应功能,是软件级。

产生事件的目的,是将采集到的一个脉冲信号送到某个外设,进而驱动某些设备做出动作,是电路级别的传输,是硬件级的。

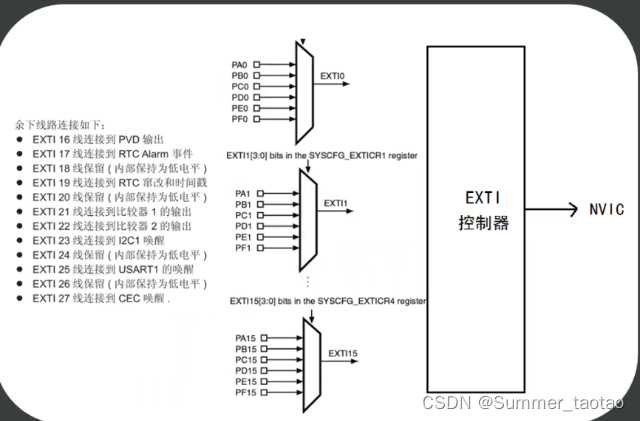

EXTI外部中断控制器EXTI

共28个中断线GPIO有16个中断线

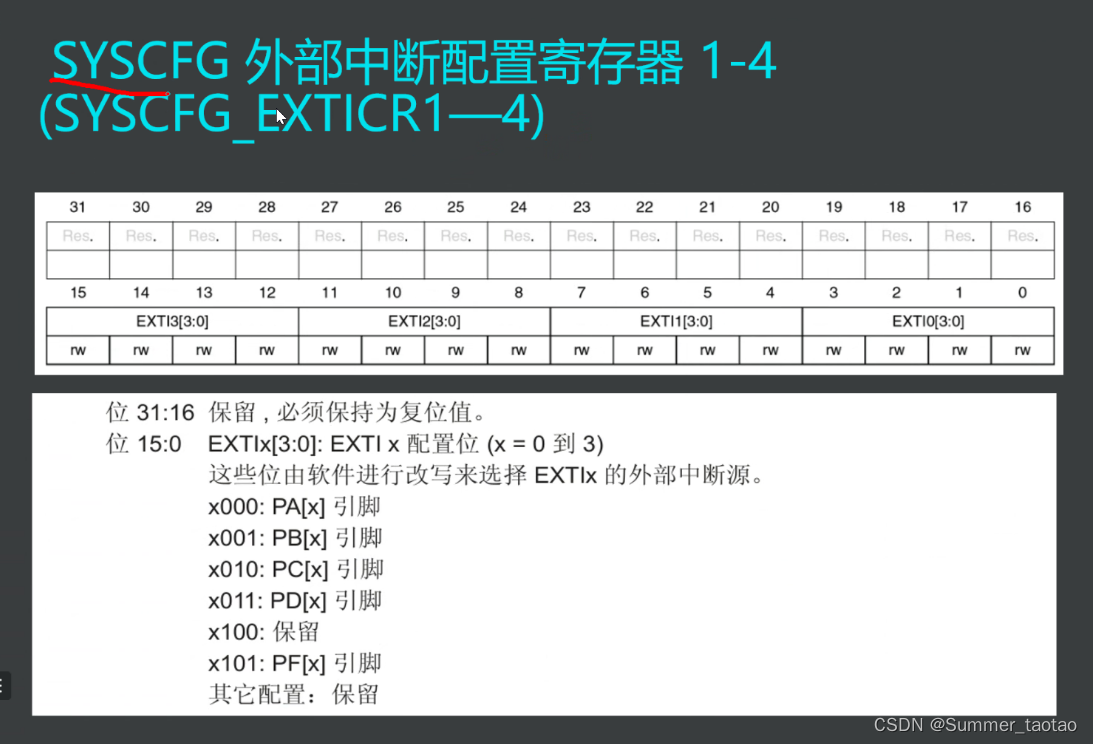

系统配置控制器SYSCFG

主要用于管理GPIO的外部中断

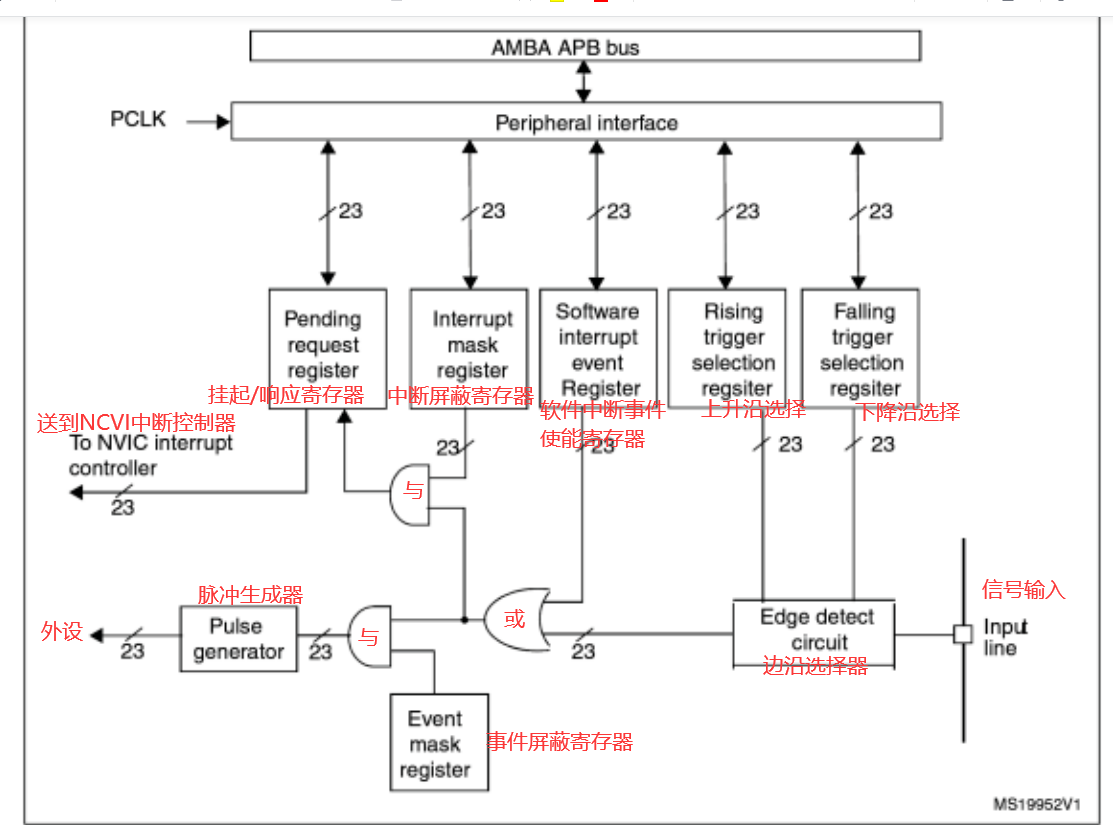

结构框图:

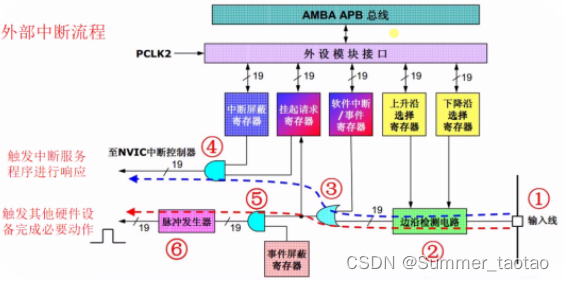

编号1是信号输入线,EXTI支持产生多达28个外部事件/中断请求。

编号2是边沿检测电路,用于监测上升沿或下降沿信号。

它会根据上升沿触发选择寄存(EXTI_RTSR)和下降沿触发选择寄存器(EXTI_FTSR)对应位的设置来控制信号触发。

边沿检测电路以输入线作为信号输入端,监测是否有边沿跳变,检测到有边沿跳变输出有效信号 1 给编号 3 电路,否则输出无效信号0。

编号3是一个或门电路,信号来源是外部事件或者软件中断/事件寄存器产生。

允许我们通过程序控制EXTI_SWIER就可以启动中断/事件线

编号4是一个与门电路,信号来源是编号3送来的信号和中断屏蔽寄存器的值,

如果中断屏蔽寄存器为0,也不会将信号送到NVIC,

只有编号3送来了中断信号且中断屏蔽寄存器允许产生中断,才会将中断信号送入NVIC.

接下来我们来看看红色虚线指示的电路流程。它是一个产生事件的线路,最终输出一个脉冲信号。

产生事件线路是在编号3电路之后与中断线路有所不同,之前电路都是共用的。

编号5是一个与门电路,信号来源是编号3送来的信号和事件屏蔽寄存器的值,

如果事件屏蔽寄存器为0,不会将信号送到脉冲发生器,

只有编号3送来了信号且事件屏蔽寄存器允许产生事件,才会将信号送入脉冲发生器(编号6), 进而产生脉冲来控制外部设备做出动作。

这样我们可以简单的控制 EXTI_EMR 来实现是否要产生事件的目的