FPGA这一块和C语言不太一样。

学习FPGA,必须时刻有时钟的概念,而单片机时钟相关性就比较差,FPGA必须把握每一个时钟。

首先介绍一下,非阻塞赋值,这个在时序逻辑里面经常遇见。

reg A;

reg B;

always @(posedge clk)

begin

A<=1,b1;

b<=1'b1;

/*

B<=1'b1;

A<=1'b1;

end

在这段程序中,A和B是同时被赋值的,具体来说就是在上升沿来的时刻,A和B同时被置1,即使调换AB的顺序;另外还有以下:

always@(posedge clk)

begin

A<=1'b1;

end

always@(posedge clk)

begin

B<=1'b1;

end

即使在两个always语句中,AB也是被同时赋值的,这就叫做非阻塞赋值。

下面介绍以下阻塞赋值:

aways@(posedge clk)

begin

A= 1‘b1;

B<=1'b1;

end

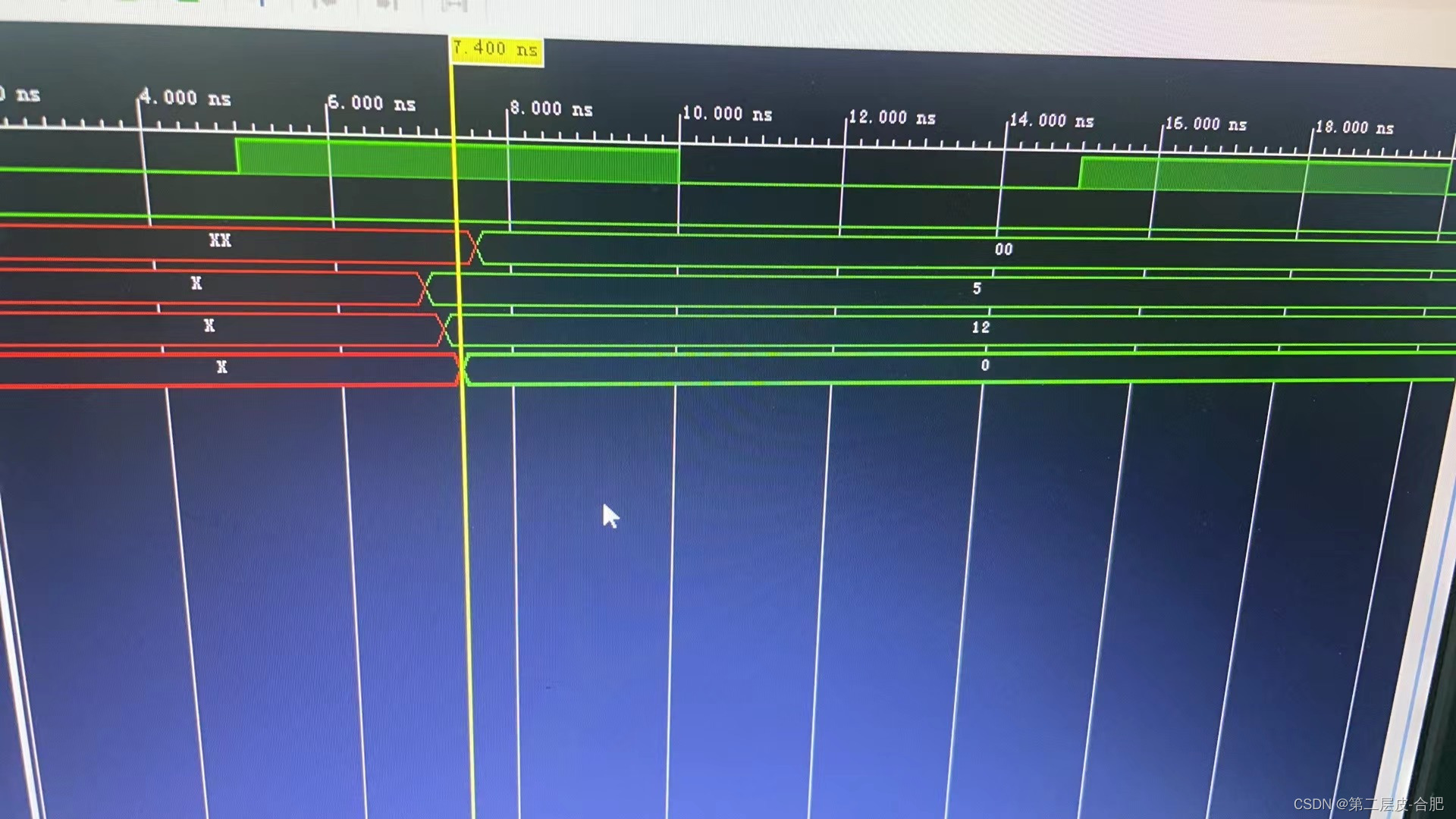

这是阻塞赋值,A比B提前零点几纳秒,不过整体来说,还是在一个时钟周期内完成的。

通常用#符号来定义阻塞的大小。

#2,代表延迟两个时钟单位;

每一个语句都是在上一条语句的基础上,进行一个延迟操作。

在针对AB求和再除以2,非阻塞两个时钟,阻塞一个时钟周期内完成。

在实战仿真时,有了以下三个经验法则:

1.加法注意位宽溢出的问题;

2.每一条语句都是在上一条语句基础上延迟,而不是在时钟基础上;

3.仿真时,找问题,可以把wire,reg信号都拉出来,进行观察。