一. MMDC 控制器

对于 I.MX6U 来说,有 DDR 内存控制器,否则的话它怎么连接 DDR 呢?MMDC控制器 就是 I.MX6U 的 DDR内存控制器。

MMDC 外设包含一个内核(MMDC_CORE)和 PHY(MMDC_PHY),内核和 PHY 的功能如下:

MMDC 内核:内核负责通过 AXI 接口与系统进行通信、DDR 命令生成、DDR 命令优化、 读/写数据路径。

MMDC PHY:PHY 负责时序调整和校准,使用特殊的校准机制以保障数据能够在 400MHz

被准确捕获。

MMDC 控制器有如下特点:

1. 最高支持DDR3的频率是 400MHz。800MT/S传输速率。

2. 多模支持,支持 DDR3/DDR3L LPDDR2 x16位

3. MMDC提供的DDR3连接信号。6ULL给DDR提供了专用的IO。

二. DDR的时钟配置

1. 时钟配置简介

时钟是由主控来提供的,也就是IMX6ULL芯片来提供。所以,我们需要通过看时钟树来学习DDR的时钟配置。下面找到"时钟章节" 来看一下 DDR的时钟配置路线。

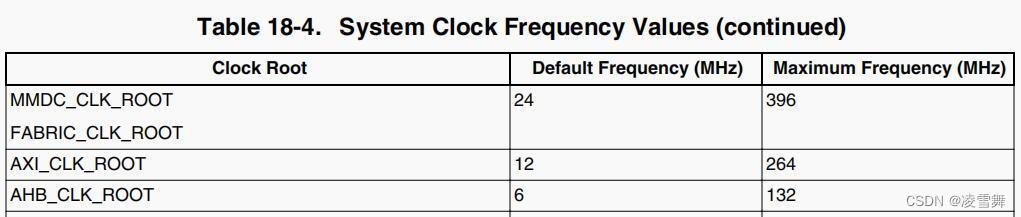

时钟树中有一个叫 "MMDC_CLK_ROOT " 的时钟线。

DDR使用的时钟源为MMDC_CLK_ROOT=PLL2_PFD2=396MHz,其实不是 400 MHz。

由IMX6ULL参考手册的时钟章节下表说明可以知道。如下表所示:

2. DDR的时钟配置

DDR使用的时钟源为MMDC_CLK_ROOT=PLL2_PFD2=396MHz。(在前面历程已经设置为396MHz)

根据上面的时钟树。有如下配置:

(1) CBCMR寄存器的PRE_PERIPH2_CLK_SE位选择时钟源。

bit-22:21,设置 pre_periph2 时钟源,为01时,选择 PLL2_PFD2 作为 pre_periph2 的时钟源。

(2) CBCDR寄存器的PERIPH2_CLK_SEL位继续选择时钟源。

bit-26,为 0时,PLL2作为MMDC时钟源,396MHz。

(3) CBCDR寄存器的FABRIC_MMDC_PODF位设置分频值。

bit5:3,设置0,是1分频。最终MMDC_CLK_ROOT=396MHz。

总结:

DDR的时钟配置说明完成。

后面我们直接使用恩智浦公司提供的 DDR配置工具。通过配置工具可以完成 DDR的初始化,测试,超频,压力测试等一系列的工作。