目录

- 1、前言

- 2、WM8731音频解读

- 3、vivado工程1介绍

- 4、vivado工程2介绍

- 5、上板调试验证

- 6、资料获取

1、前言

本文用FPGA驱动WM8731音频芯片,实现音频相关的应用,适用于在校学生做毕业设计、研究生项目开发,也适用于在职工程师做项目开发,可应用于医疗、军工等行业的数字音频应用领域;

提供完整的、跑通的工程源码和技术支持;

工程源码和技术支持的获取方式放在了文章末尾,请耐心看到最后;

本设计提供两套vivado工程;

1:FPGA驱动WM8731实现音频环回工程;

2:FPGA驱动WM8731实现音频录音工程;

2、WM8731音频解读

WM8731音频解读我之前已经写过两篇文章,请前往参考;

链接1:https://blog.csdn.net/qq_41667729/article/details/120753491

链接2:https://blog.csdn.net/qq_41667729/article/details/120953453

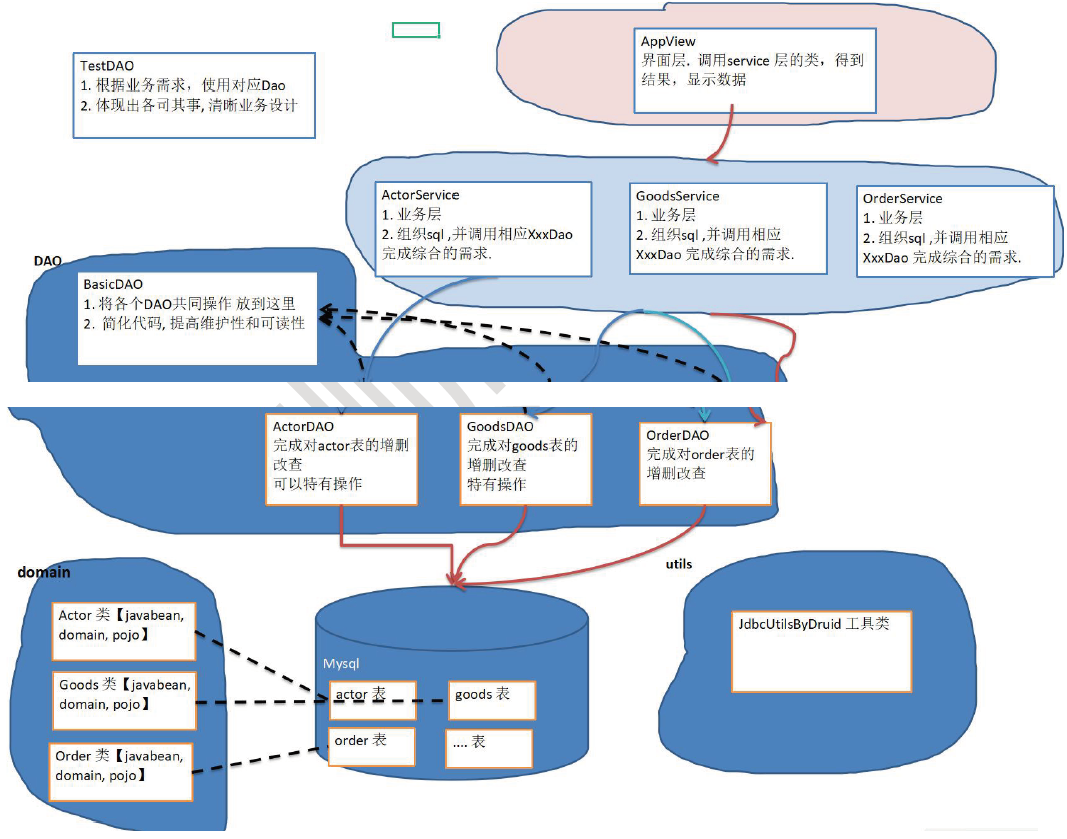

3、vivado工程1介绍

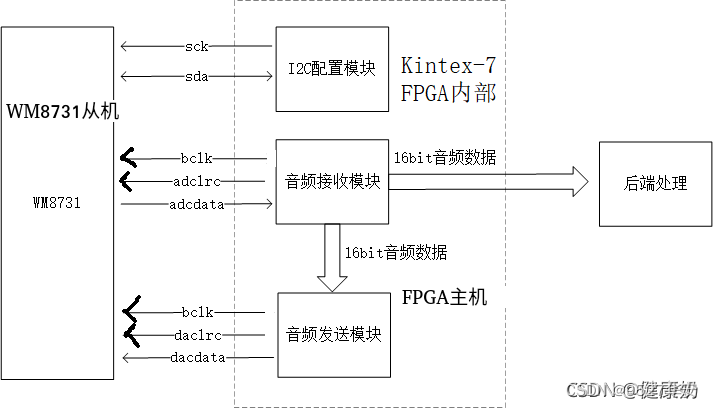

设计框图如下:

FPGA作为i2s主机,WM8731作为i2s从机,这样设计的好处在于保证了时序的同步,即采集时钟和发送时钟都是同一个时钟,且这个时钟由FPGA提供,这样就不存在数据时钟不同源甚至不同步的问题,对数据采集而言具有高度科学性。。。

将i2c配置模块、音频接收模块、音频发送模块例化为一个顶层,代码如下:

module wm8731_i2s_slave(

input clk_100m , //输入参考时钟

input rst_n , //低电平复位

input i_adc_data, //输入音频ADC串行数据

output o_av_bclk , //输出i2c音频时钟

output o_adc_rlc , //输出ADC左右声道信号

output o_dac_rlc , //输出DAC左右声道信号

output o_dac_data, //输出音频DAC串行数据

output o_aud_scl , //i2c配置

inout o_aud_sda //i2c配置

);

wire p_bclk;

wire n_bclk;

wire [31:0] o_rx_data;

//i2s时序生成模块,这里是i2s主机模块,WM8731作为从机;

//SYS_CLK参数配置系统参考时钟;

//SAMPLE_RATE参数配置i2s采样率,这里设置为48K;

//SAMPLE_DEEP参数配置采样深度,这里设置为32位;

i2s_slave_time #(

.SYS_CLK (100_000_000),

.SAMPLE_RATE (48_000 ),

.SAMPLE_DEEP (32 )

)

u_i2s_slave_time(

.clk_100m (clk_100m ),

.rst_n (rst_n ),

.o_av_bclk (o_av_bclk ),

.o_adc_rlc (o_adc_rlc ),

.o_dac_rlc (o_dac_rlc ),

.p_bclk (p_bclk ),

.n_bclk (n_bclk )

);

//音频接收模块,将串行ADC数据转为32位的并行ADC数据

//SAMPLE_DEEP可配置采样深度

i2s_slave_rx #(

.SAMPLE_DEEP(32)

)

u_i2s_slave_rx(

.clk_100m (clk_100m ),

.rst_n (rst_n ),

.i_adc_rlc (o_adc_rlc ),

.i_adc_data (i_adc_data ),

.i_p_bclk (p_bclk ),

.i_n_bclk (n_bclk ),

.o_rx_data (o_rx_data ),

.o_rx_done ( )

);

//音频发送模块,将32位并行DAC数据转为串行ADC数据

//SAMPLE_DEEP可配置采样深度

i2s_slave_tx #(

.SAMPLE_DEEP(32)

)

u_i2s_slave_tx(

.clk_100m (clk_100m ),

.rst_n (rst_n ),

.i_dac_rlc (o_dac_rlc ),

.i_adc_data (o_rx_data ),

.i_p_bclk (p_bclk ),

.i_n_bclk (n_bclk ),

.o_dac_data (o_dac_data ),

.o_tx_done ( ),

.p_rlc_edge ( )

);

//WM8731 i2c配置模块

wm8731_config wm8731_config(

.clk (clk_100m ), // 时钟信号

.rst_n (rst_n ), // 复位信号

.i2c_ack ( ), // I2C应答标志 0:应答 1:未应答

.aud_scl (o_aud_scl ), // wm8731的SCL时钟

.aud_sda (o_aud_sda ) // wm8731的SDA信号

);

endmodule

基于此,设计了FPGA驱动WM8731实现音频环回工程;

工程架构如下:

开发板FPGA型号:xc7k410tffg676-2;

输入:麦克风,即ADC输入;

输出:耳机,即DAC输出;

应用:WM8731的音频回环测试;

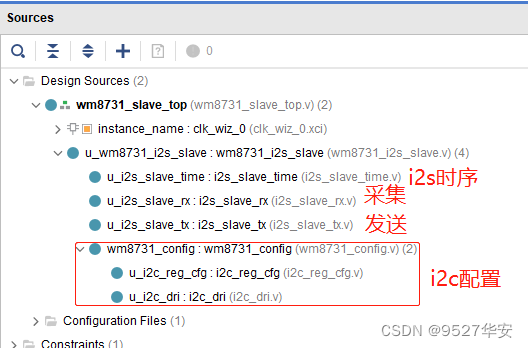

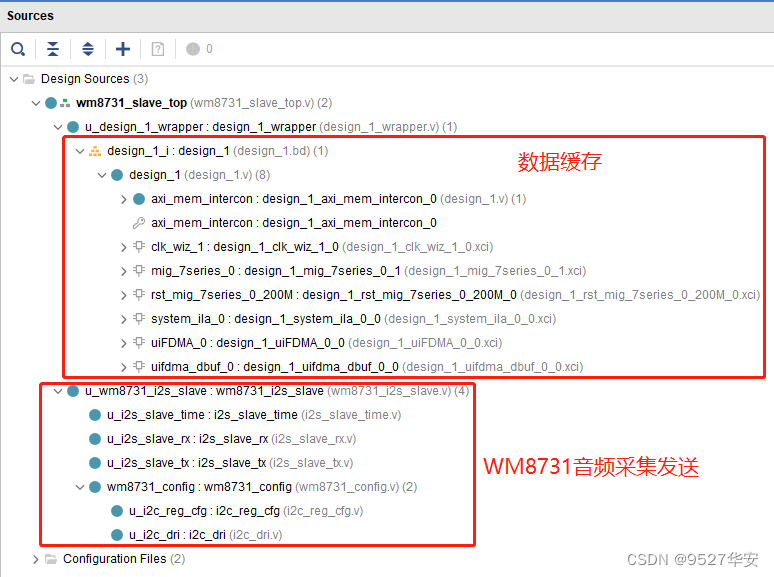

工程源码架构如下:

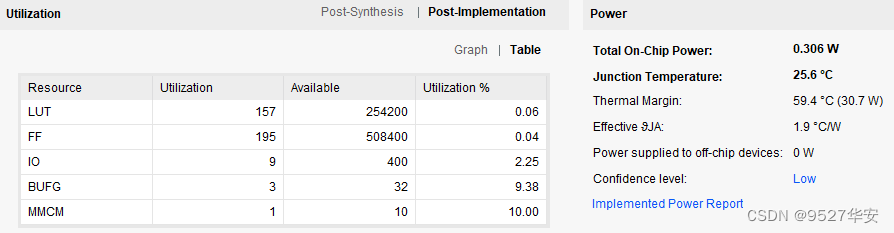

FPGA资源消耗如下:

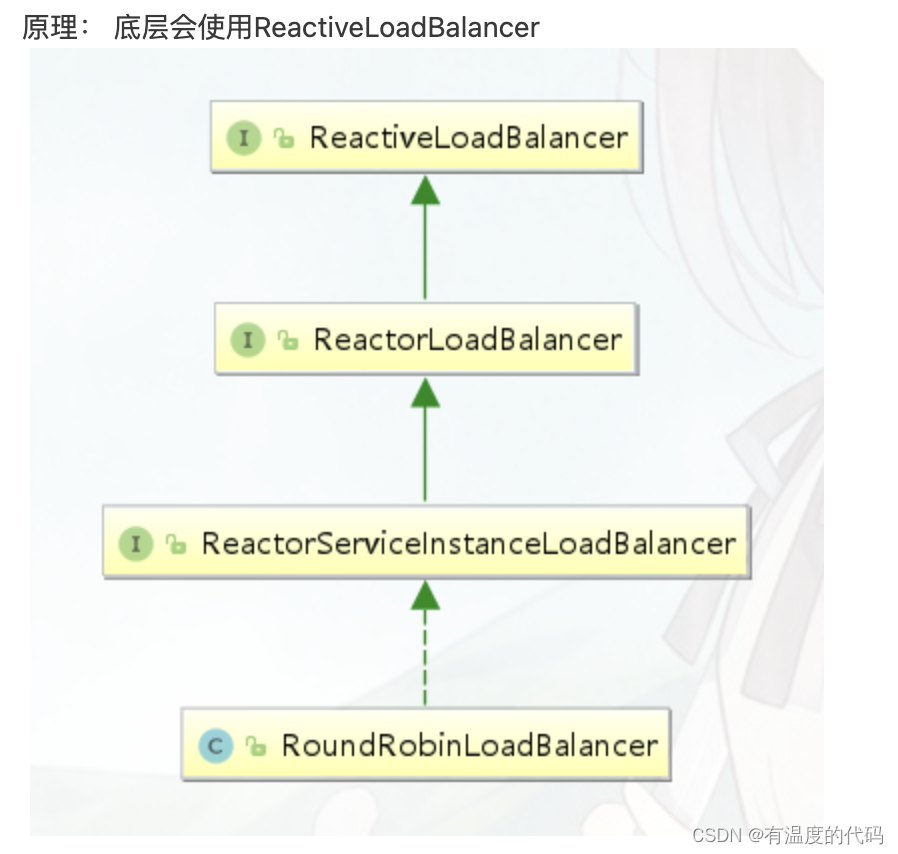

4、vivado工程2介绍

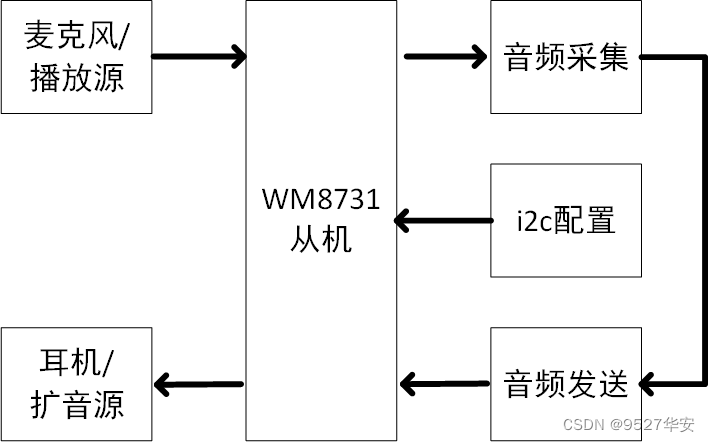

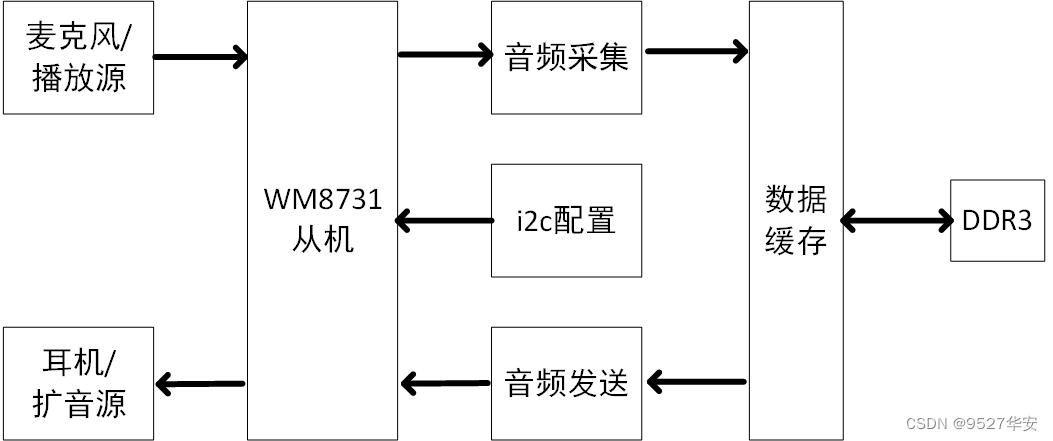

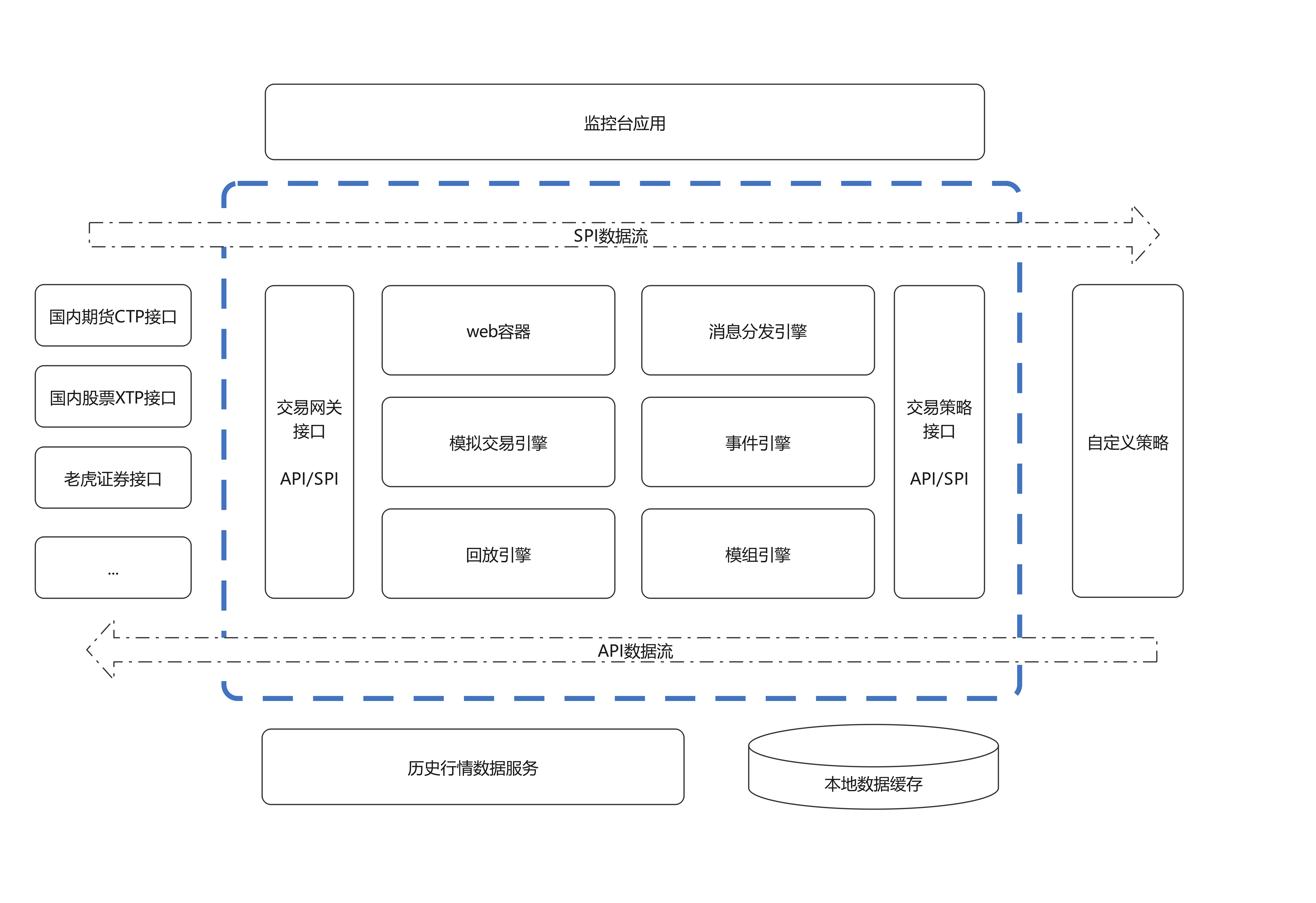

设计框图如下:

开发板FPGA型号:xc7k410tffg676-2;

输入:麦克风,即ADC输入;

输出:耳机,即DAC输出;

应用:WM8731的音频录音测试;

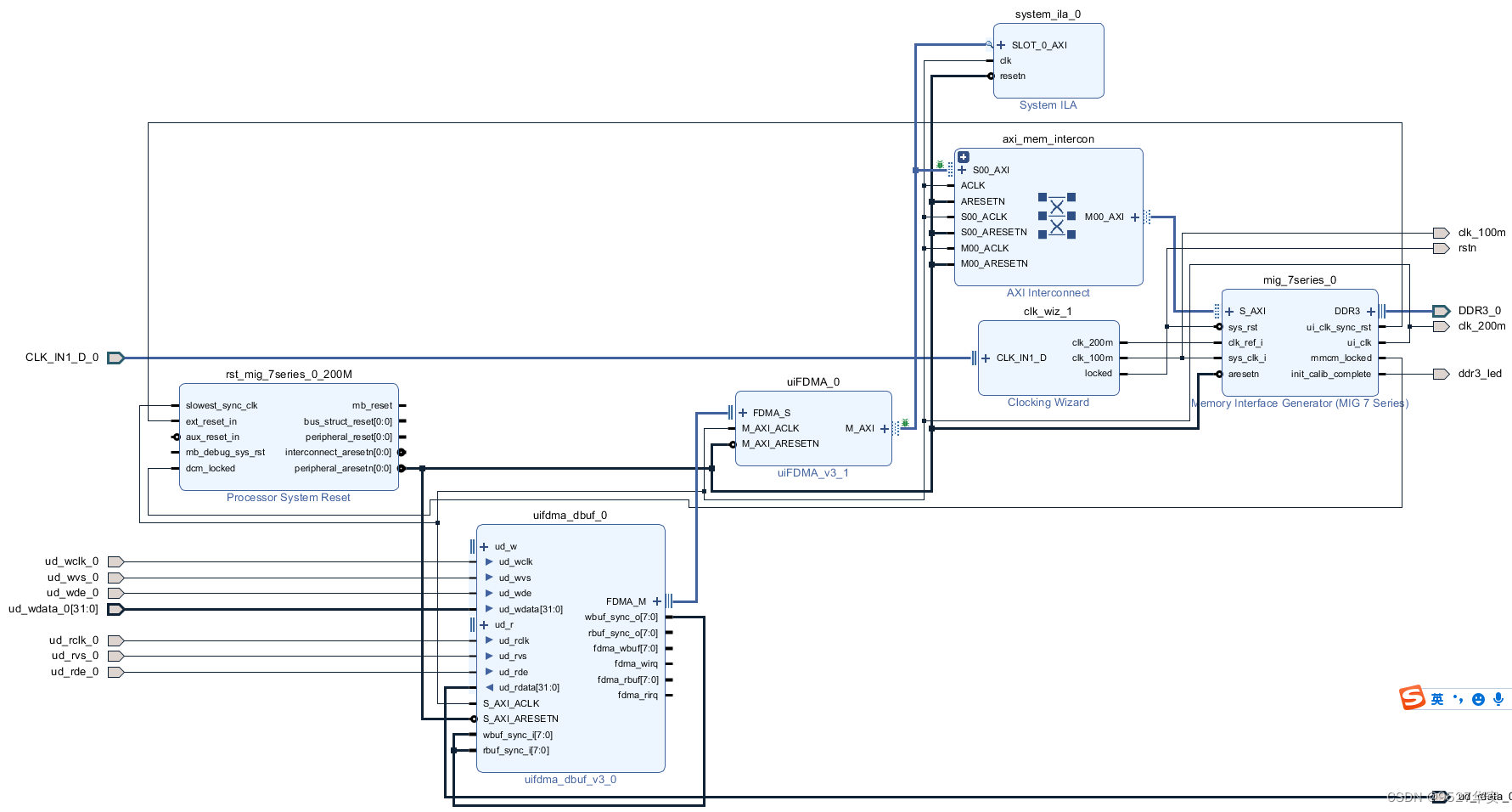

工程Block Design架构如下:

工程源码架构如下:

5、上板调试验证

由于板子不方便带回家录视频,所以演示就不给出了,请谅解。。。

6、资料获取

福利:工程代码的获取

代码太大,无法邮箱发送,以某度网盘链接方式发送,

网盘资料如下:

FPGA驱动WM8731实现音频环回工程源码获取链接:https://download.csdn.net/download/qq_41667729/87781868

FPGA驱动WM8731实现音频录音工程源码获取链接:https://download.csdn.net/download/qq_41667729/87781869

![PMP项目管理-[第十二章]采购管理](https://img-blog.csdnimg.cn/01abcb8b975b44e694335e3e1745c33c.png)

![心法利器[84] | 最近面试小结](https://img-blog.csdnimg.cn/img_convert/90a5f9e6bbc1e3a556ef065f1394a837.png)