前言

I/O Delay约束主要有两个命令:set_input_delay和set_output_delay。

I/O Delay约束的主要目的同时钟约束一样,是告诉编译器,外部输入输出信号与参考时钟之间的相位关系,便于综合器能够真实和准确的对IO接口的信号进行时序分析,同时也有利于综合器的布局布线。

注意:I/O Delay约束和 IDELAYE、ODELAYE原语是完全不同的,前者是用于编译器进行时序分析的,后者是对数据进行延时的(由于建立时间和保持时间不满足,导致在接收数据有错时,需要对数据进行延迟,以满足建立时间和保持时间)。换言之,前者是时序分析手段,后者是电路调试手段。

一、input delay

输入信号是在时钟沿后多长时间到达模块的port上。

"set_input_delay"命令是用于指定输入端口(PIN)的数据输入相对于设计中参考时钟边沿的延迟。 输入延迟值以ns为指定单位,可以为正值,也可以为负值,具体取决于设备接口处的时钟和数据的相对相位关系。

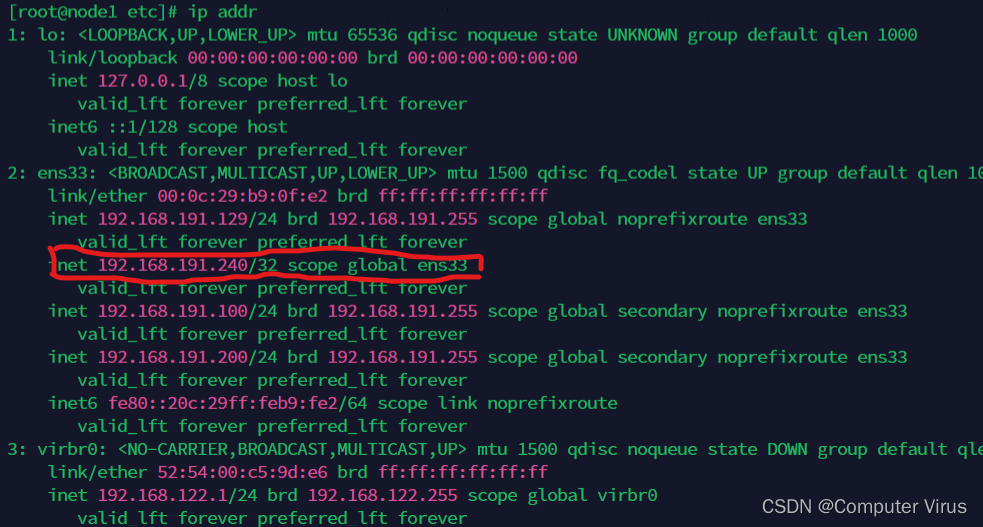

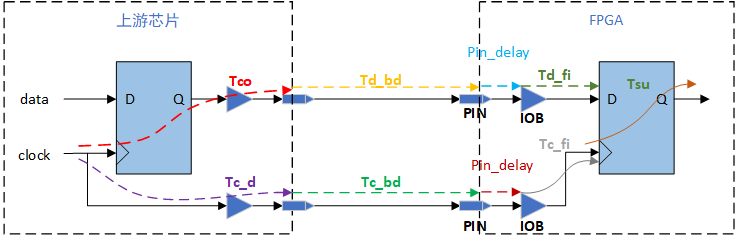

这里特别强调的是FPGA芯片的PIN到内部IOB是有pin delay的,但是set_input_delay指定的延迟是不包含pin delay的值。即set_input_delay所指的延迟是下图中Tco+td_bd-Tc_d-tc_bd的值。

说明:

上图为IO接口的时序分析模型,模型可分为3部分,分别是上游芯片,PCB走线,下游芯片(这里主要指FPGA)。上图中的时序参数含义分别如下:

| 时序参数 | 含义 |

| Tco | 上游芯片输出数据管脚相较于扇出节点时钟发射沿延时 |

| Tc_d | 上游器件输出管脚处时钟,相较于扇出节点时钟延时 |

| Td_bd | 数据在PCB上的走线延时 |

| Tc_bd | 时钟在PCB上的走线延时 |

| pin_delay | FPGA的封装引脚pin到内部IOB的延迟 |

| Td_fi | FPGA内部数据通路上,IOB到FPGA内部D触发器的路径延迟 |

| Tc_fi | FPGA内部随路时钟通路上,IOB到FPGA内部D触发set_input_delayinput_delay |

二、set_input_delay语法

set_input_delay [-clock <args>] [-reference_pin <args>] [-clock_fall] [-rise]

[-fall] [-max] [-min] [-add_delay] [-network_latency_included]

[-source_latency_included] [-quiet] [-verbose] <delay>

<objects>

| 选项 | 含义 |

|---|---|

| -clock | 相对时钟,默认使用上升沿,也可以使用-clock_fall指定使用下降沿 |

| -reference_pin | 指定延迟与出现在指定引脚或端口上的时钟的有效边沿有关,而不是与时钟有关。 |

| -clock_fall | 指定延迟是相对于时钟的下降沿 |

| -rise | 指定应用于指定端口上的上升转换的输入延迟。 默认是对上升和下降转换应用延迟(用于指定数据的,非时钟的)。 |

| -fall | 指定应用于指定端口上的下降转换的输入延迟。 默认是对上升和下降转换应用延迟(用于指定数据的,非时钟的)。 |

| -max | 表示指定的输入延迟仅在计算最大(最长)路径延迟时使用(建立时间)。 |

| -min | 表示指定的输入延迟仅在计算最小(最短)路径延迟时使用(保持时间)。 |

| -add_delay | 将指定的延迟约束添加到端口,以与端口上已定义的任何其他 set_input_delay 约束共存。 默认行为是替换现有的延迟。 |

| -network_latency_included | 表示参考时钟的时钟网络延迟包含在延迟值中。 除非指定的输入或输出延迟值包括源延迟或网络延迟,否则 Vivado 时序分析器会考虑在时钟延迟之后到达捕获触发器的时钟边沿。 |

| -source_latency_included | 指示相对时钟的源延迟包含在指定的延迟值中。 |

| -quiet | 忽略命令错误 |

| -verbose | 命令执行期间暂停消息限制 |

| delay | 延时值 |

| objects | 端口列表 |

三、用法举例

示例一: 创建一个时钟周期为10ns的sysClk 时钟,然后设定端口DIN相对于时钟sysClk 上升沿的最大和最小延迟为2ns:

create_clock -name sysClk -period 10 [get_ports CLK0]

set_input_delay -clock sysClk 2 [get_ports DIN]

示例二: 创建一个虚拟时钟clk_port_virt ,周期为10ns,然后设定端口DIN相对于时钟clk_port_virt 下降沿的最大和最小延迟为2ns:

create_clock -name clk_port_virt -period 10

set_input_delay -clock_fall -clock clk_port_virt 2 [get_ports DIN]

示例三: 定义输入端口reset相对于wbClk_IBUF_BUFG_inst/O输出的时钟的输入延迟为2ns,其中wbClk_IBUF_BUFG_inst/O输出时钟的时钟源为wbClk:

set_input_delay -clock wbClk 2 -reference_pin [get_pin wbClk_IBUF_BUFG_inst/O] reset

示例四: 定义输入端口DIN相对时钟sysClk不同的相对延迟,用于最大路径分析和最小路径分析:

create_clock -name sysClk -period 10 [get_ports CLK0]

set_input_delay -clock sysClk -max 4 [get_ports DIN]

set_input_delay -clock sysClk -min 1 [get_ports DIN]

示例五: 限制I/O端口之间的纯组合逻辑路径,首先定义一个虚拟时钟,用于约束输入和输出延迟,例如设定DIN端口到DOUT端口的纯组合逻辑的延迟为5ns(10ns-1ns-4ns):

create_clock -name sysClk -period 10 [get_ports CLK0]

set_input_delay -clock sysClk 4 [get_ports DIN]

set_output_delay -clock sysClk 1 [get_ports DOUT]

示例六: DDR数据的input delay约束:

create_clock -name clk_ddr -period 6 [get_ports DDR_CLK_IN]

set_input_delay -clock clk_ddr -max 2.1 [get_ports DDR_IN]

set_input_delay -clock clk_ddr -max 1.9 [get_ports DDR_IN] -clock_fall -add_delay

set_input_delay -clock clk_ddr -min 0.9 [get_ports DDR_IN]

set_input_delay -clock clk_ddr -min 1.1 [get_ports DDR_IN] -clock_fall -add_delay

示例七: 对STARTUPE3 内部pin(UltraScale+器件)的input delay约束:

//重命名STARTUP/CCLK自动衍生的时钟名为clk_sck,时钟源为axi_quad_spi_0/ext_spi_clk,频率为时钟源的1/2

create_generated_clock -name clk_sck -source [get_pins -hierarchical *axi_quad_spi_0/ext_spi_clk] [get_pins STARTUP/CCLK] -edges {3 5 7}

set_input_delay -clock clk_sck -max 7 [get_pins STARTUP/DATA_IN[*]] -clock_fall

set_input_delay -clock clk_sck -min 1 [get_pins STARTUP/DATA_IN[*]] -clock_fall

四、实操演示

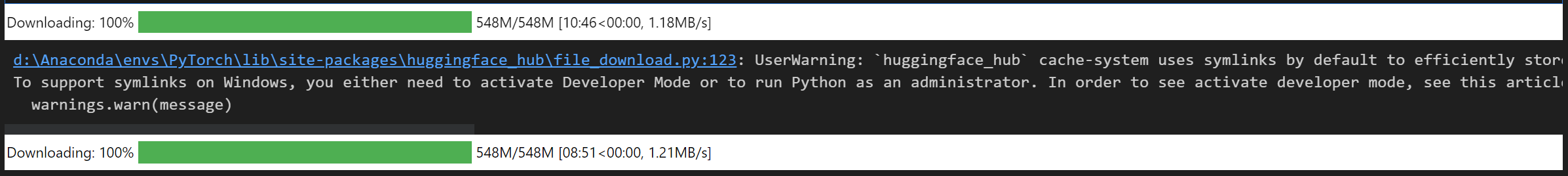

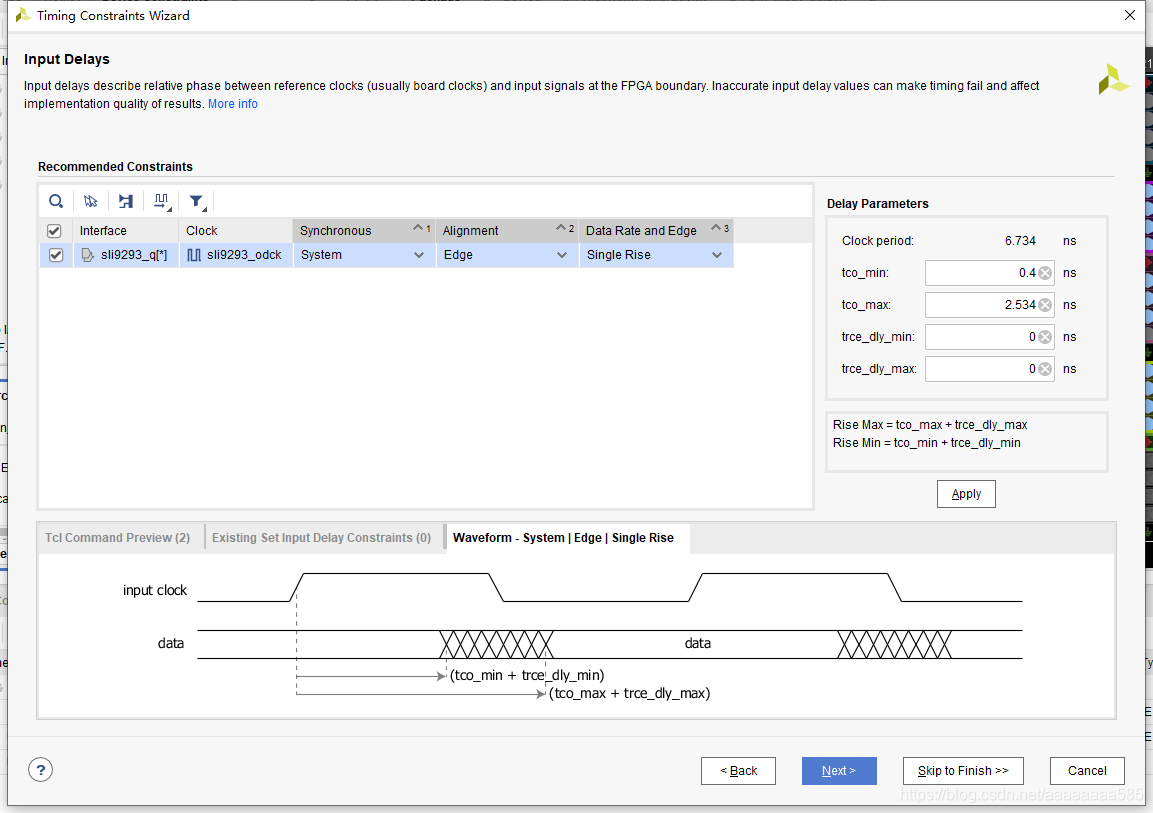

以SiI9293 MHL/HDMI接收器芯片为例,利用vivado的时序约束向导进行input delay约束,下图为硬件环境模型:

通过查阅SiI9293的芯片资料手册,可以获取芯片并行数据输出接口Q和随路时钟ODCK之间的时序关系: 时序约束中假设PCB布线等长时间差很小,可以忽略不计,由上可知在148.5MHz的频率下,数据在时钟上升沿前4.2ns稳定,并在时钟上升沿后的0.4ns后,开始输出下一个并行数据,结合vivado的时序约束向导中的input delays 页面,进行输入延时约束:

时序约束中假设PCB布线等长时间差很小,可以忽略不计,由上可知在148.5MHz的频率下,数据在时钟上升沿前4.2ns稳定,并在时钟上升沿后的0.4ns后,开始输出下一个并行数据,结合vivado的时序约束向导中的input delays 页面,进行输入延时约束:

界面中tco_min对应的延时值为手册中的Tck2out(min),tco_max 对应芯片手册中的Tck2out(max)

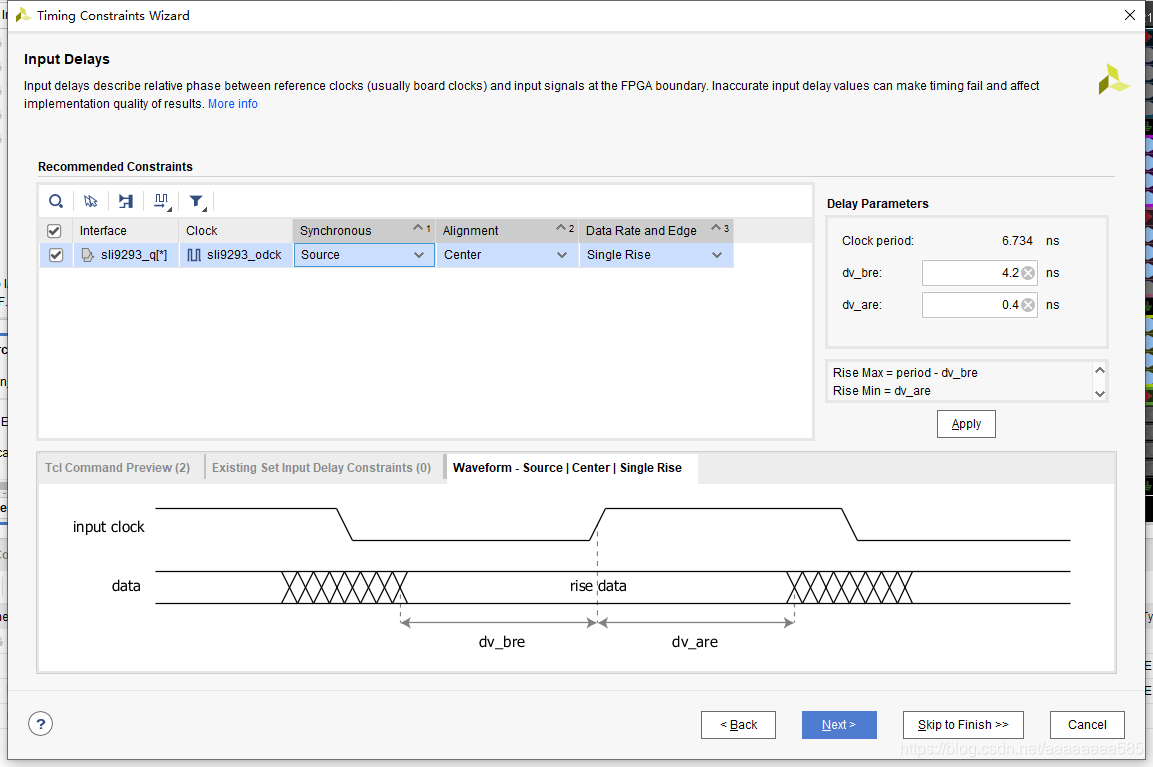

vivado的时序约束向导中的input delays约束方法2:

界面中dv_bre对应的延时值为手册中的Tsu,dv_are 对应芯片手册中的Thd

XDC约束语法如下:

set_input_delay -clock [get_clocks {sli9293_odck}] -min 0.4 [get_ports {sli9293_q[*]}]

set_input_delay -clock [get_clocks {sli9293_odck}] -max 2.534 [get_ports {sli9293_q[*]}]

五、总结

min = hold time

max = T - setup time

max - min = 数据抖动时间