仅供同学参考,严禁用作商业用途 如发现将追究责任

2023-5-14 属鼠经历了计算机组成原理考试 现将本人真题回忆如下:欢迎大家补充,并期待大家一起参与这个开源的项目。

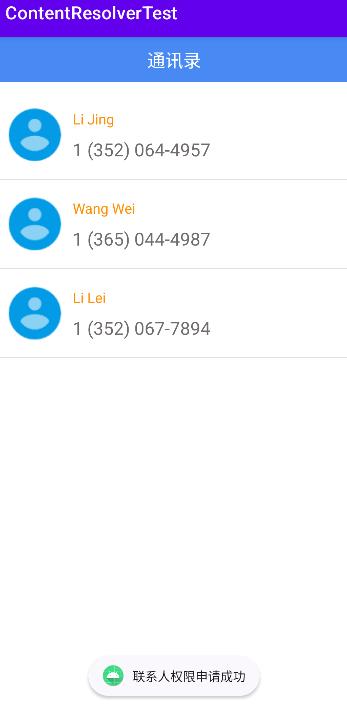

致谢:真诚感谢草履虫同学提供的图片

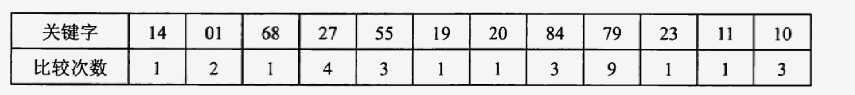

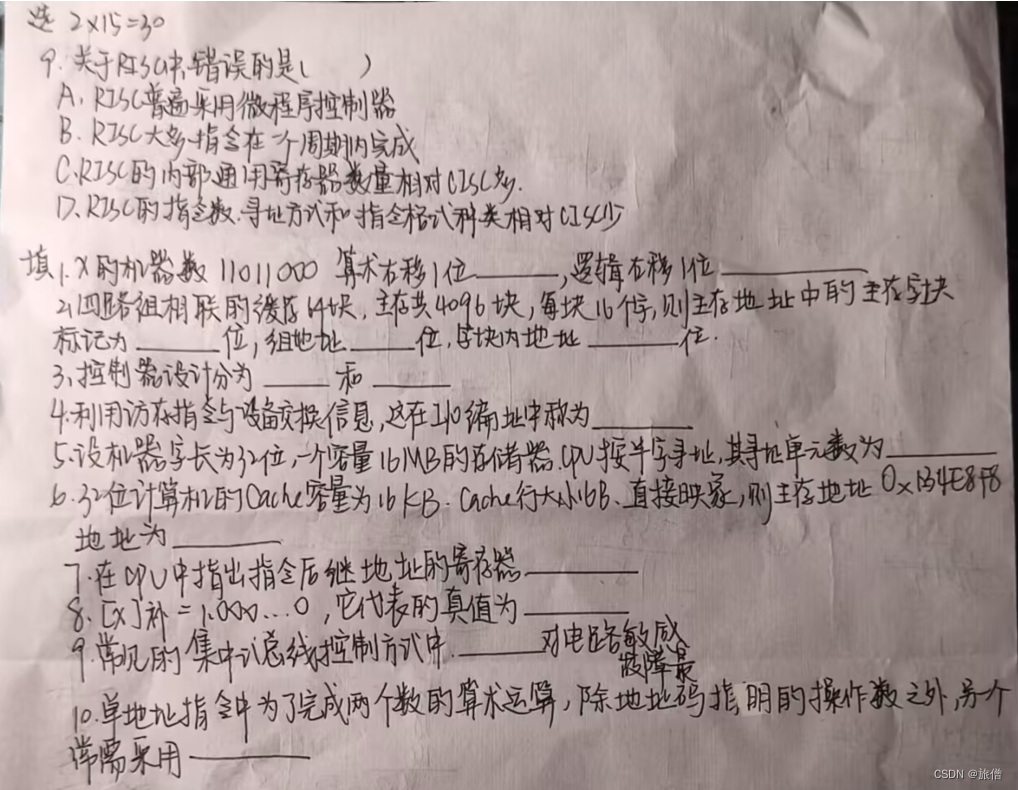

15个选择部分回忆如下 :

- 原来的计算机工作周期是20s,改进之后指令周期变成原来的70%,CPI变成1.2倍,问周期是啥 我写的是16.8

- 原码和补码的比较 很简单 大概是补码的范围 负数可以用补码做加法

- DMA工作时候CPU是否可以和主存交换信息 DMA传输完毕之后发出中断 就是DMA的过程

- 为啥要把设计指令和数据cache A减少缺失率 B提高命中率 C减少流水线访问冲突 D减少访问时间。

- CPU执行 指令的地址是哪个给出? A PC B程序员 C指令的地址码字段 D操作系统

- 采用单流水的方式 有取指令 间址 执行三个阶段 指令12个指令的时间 A14 B 15...选项忘了。

- 虚拟内存考的是下列哪一种情况不能出现 TLB命中/不命中 cache命中/不命中 主存命中/不命中。

- 微指令控制器的位置:ACPu B主存 Ccache D忘了

- 中断向量是啥 A中断服务程序的入口地址...... B程序的首地址.....之类的选项

- RISC经典指令集

- 数据通路组成的一些东西 有没有中断系统 时序逻辑比如寄存器 组合逻辑比如 是由控制信号联系的... 老师最后发的PPT里

- 一个32K*8的芯片需要几个小芯片连接 课本上的位扩展和字扩展

- 定义 偏移寻址 是一个类似一个基地址加上一个偏移的寻址方式 下列不是偏移寻址的是 A:间接寻址 B基质寻址 C变质寻址 D相对寻址

- 同微指令相比 硬布线的特点 速度快/慢 电路逻辑设计是复杂还是简单

- 给一个主存地址和字长 按半字寻址的范围。

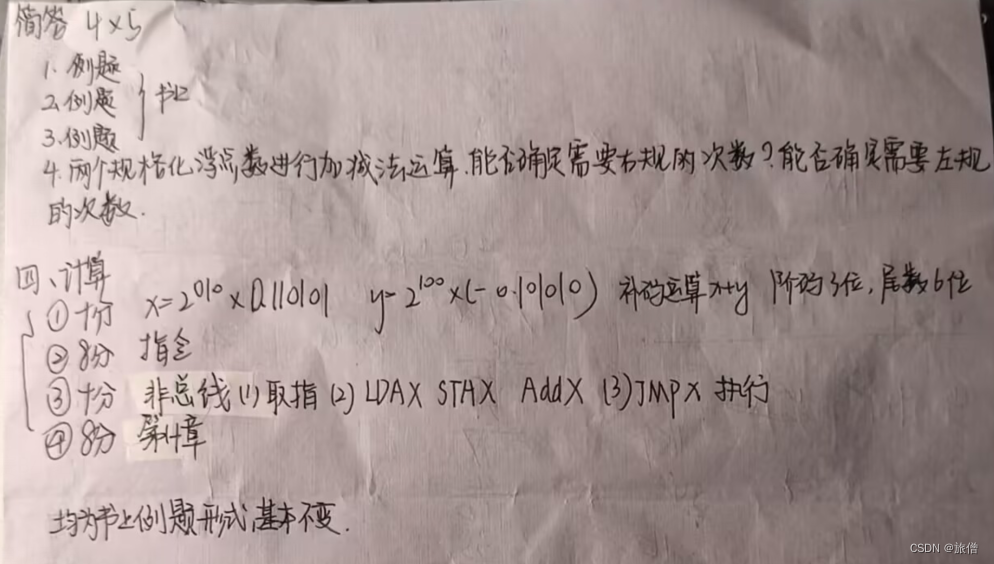

大题

- 多重中断设置屏蔽字 和画出CPU执行流程图

- 64位总线给周期求 数据传输率

- 浮点数补码表示的加法

- 增加cahce命中率提高了多少

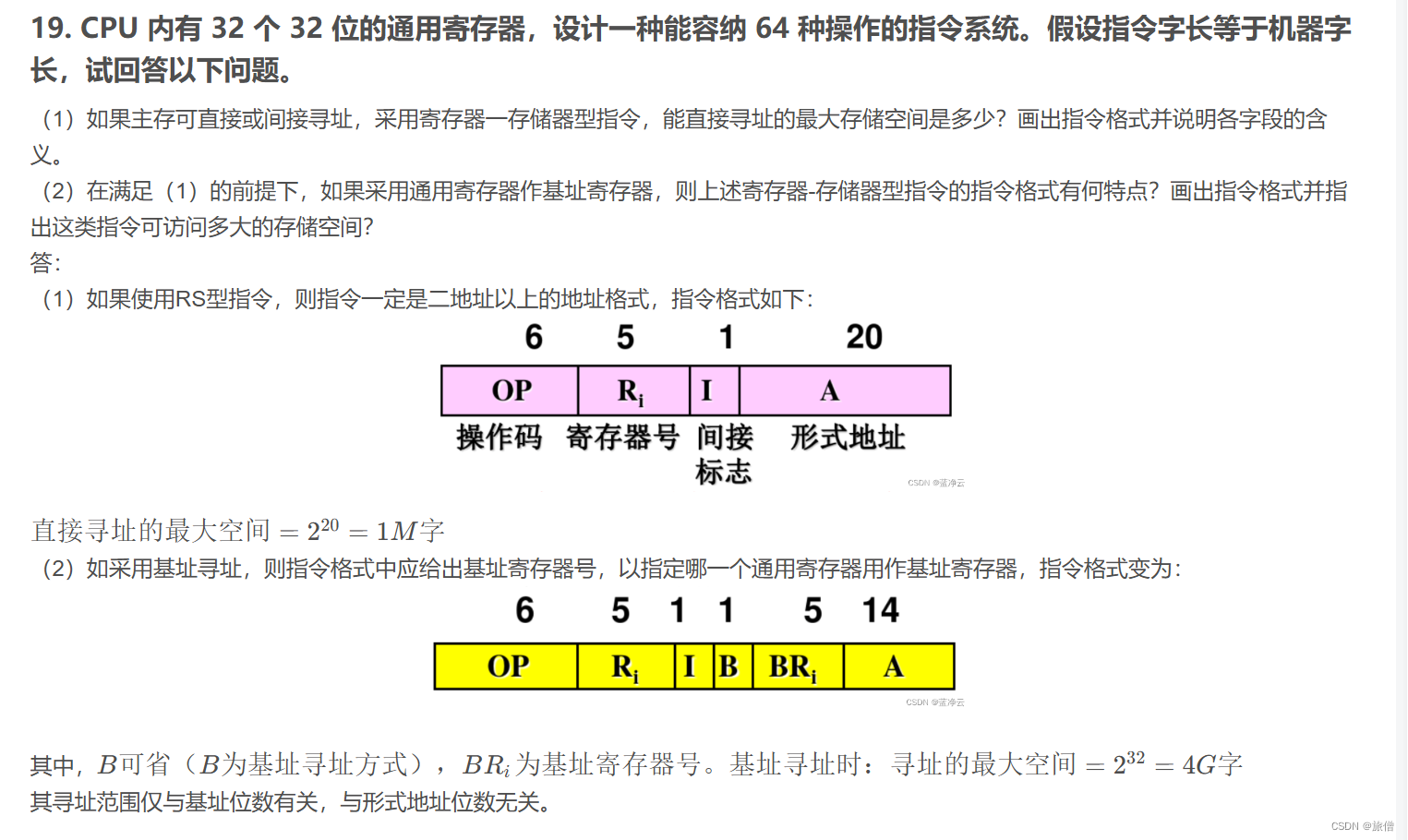

- 设计指令的格式

最后一个是芯片连接题 就是课件的第一个例题

最后一个是芯片连接题 就是课件的第一个例题

自己的一些感悟:

- 还是要上课听课 有些东西光看慕课是没有的比如虚拟内存慕课上是没有的,

- 还有就是光做题是没用的 一定要明白是为啥 题永远做不完

- 题量 因为都是保留原味 所以要见多识广 比如指令那个题是晚上问大佬的

- 我的建议考完是对答案的 印象深刻

- 习惯从平时养成 比如最后我手忙脚乱 那个芯片逻辑门记错了 一点数电的知识需要平时积累

- 好好做实验 实验是检验真理的唯一标准