本文使用的测试代码如下

(1条消息) stm3274hc595外扩io调试工程,软件代码2片74hc595级联外扩IO资源-CSDN文库

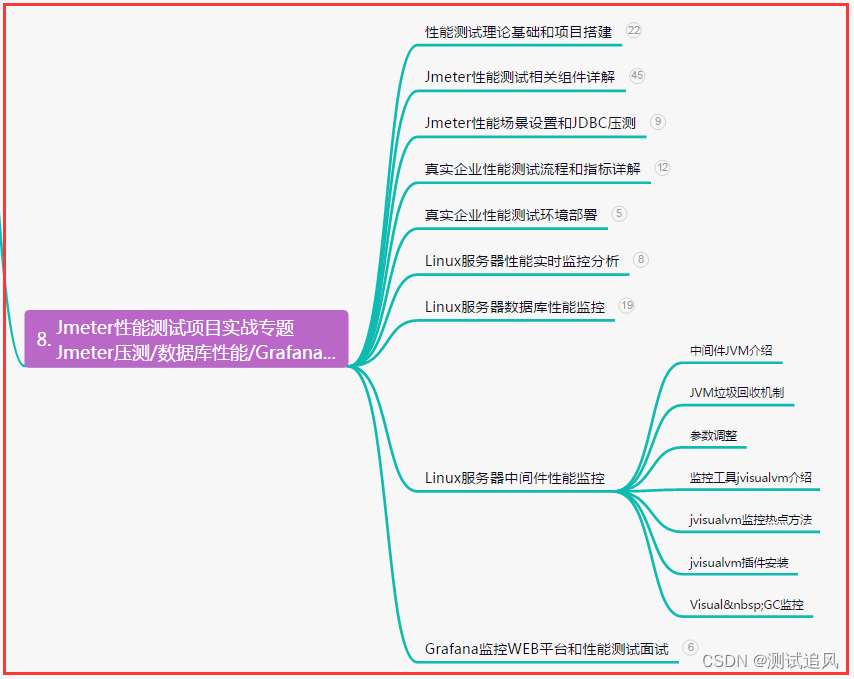

有个项目对成本比较敏感,又想用ST的片子,输出管脚比较多,就考虑外扩IO,也有一些外扩IO的片子但是用下来成本就比较高了,还好这些都是一些输出IO,没有什么特别要求,例如输出PWM之类的。

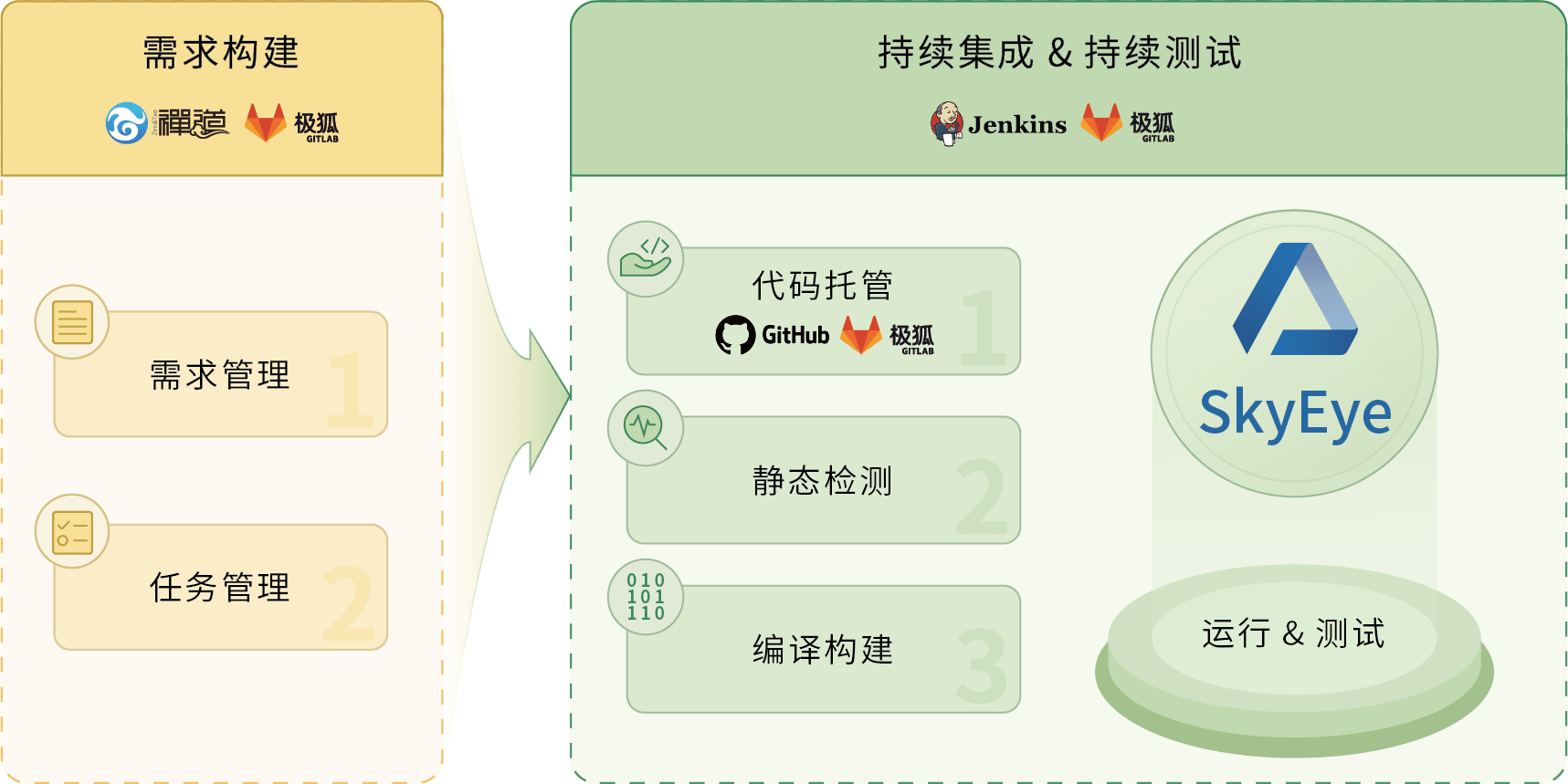

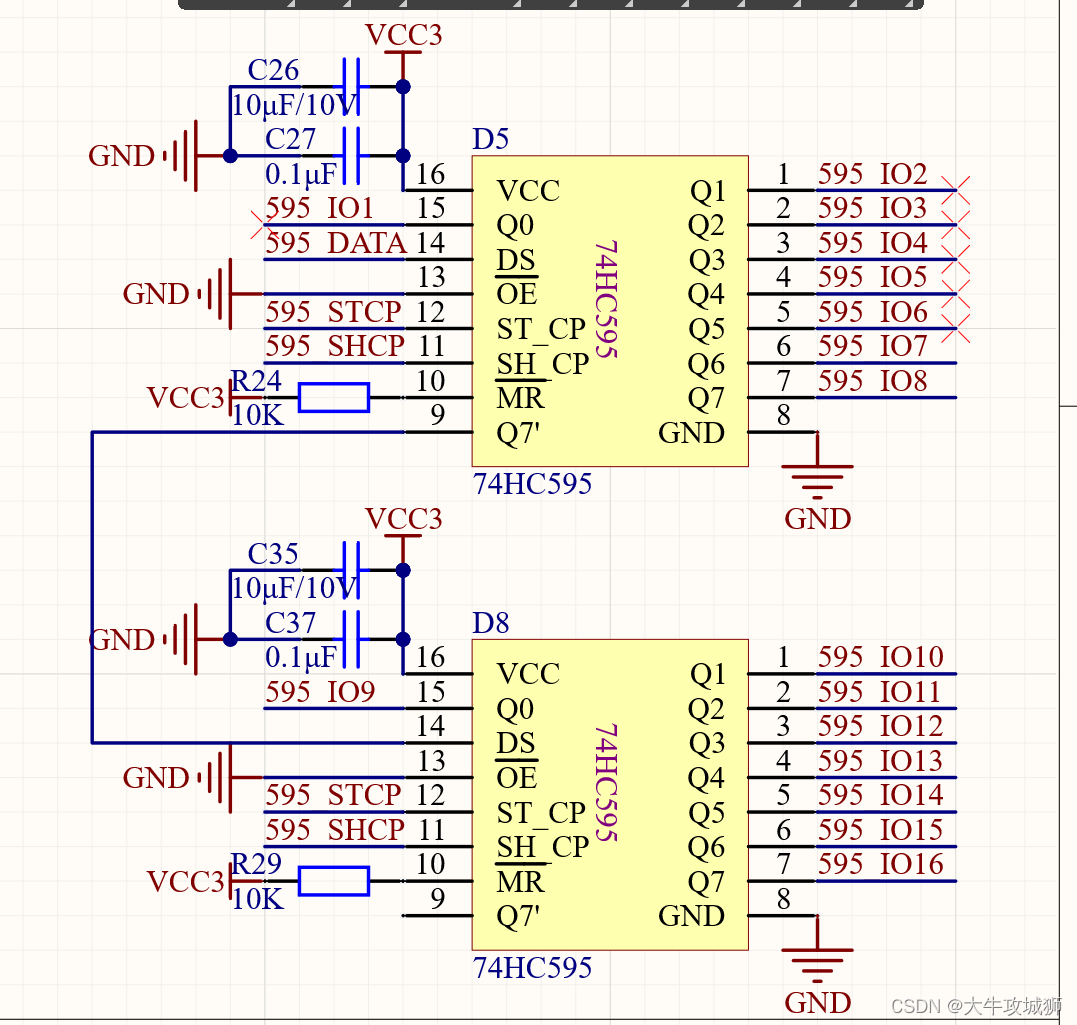

这里采用两片74hc595进行级联,外扩16路IO,原理图如下所示

74hc595的基本资料,网上比较多了,这里做个简单说明

管脚说明:

14脚:DS(SER),串行数据输入引脚

13脚:OE,输出使能控制脚,它是低电才使能输出,所以接GND

12脚:RCK(STCP),存储寄存器时钟输入引脚。上升沿时,数据从移位寄存器转存到存储寄存器。

11脚:SCK(SHCP),移位寄存器时钟引脚,上升沿时,移位寄存器中的bit 数据整体后移,并接受新的bit(从SER输入)。

10脚:MR,低电平时,清空移位寄存器中已有的bit数据,一般不用,接 高电平即可。

9 脚 :串行数据出口引脚。当移位寄存器中的数据多于8bit时,会把已有的bit“挤出去”,就是从这里出去的。用于595的级联。

Q0~Q7:并行输出引脚

使用参数:

VCC:2V~6V,5V最好

IQn:± 35mA

注意事项:

第一个从SER送入的bit将会从Q7出去。

原理图

主函数进行测试

//测试输出管脚,周期拉高拉低

HC595Init(0);

HAL_Delay(1000);

HC595Init(0xffff);

HAL_Delay(1000);

74hc595写入数据函数

static void HC595SendData(uint16_t OutData)

{

unsigned char i;

for (i = 0; i < 16; i++) //

{

SHCP595(0); //时钟线底

//hc595Dly(50);

if ((OutData & 0x8000) == 0x8000) //

{

DATA595(1); //

}

else

{

DATA595(0); //

}

OutData = OutData << 1; //

SHCP595(1); //

//hc595Dly(50);

}

//上升沿输出数据

STCP595(0);

//hc595Dly(50);

STCP595(1);

}调试过程发现,拉高拉低时序过程中不用加入延时函数

这样加快了对hc595的写入,如果移植改函数,需要注意一下时钟的主频,我这里使用的时钟主频是72M

如下图所示

使用的stm32cubemx版本如下

本文使用的测试代码如下

(1条消息) stm3274hc595外扩io调试工程,软件代码2片74hc595级联外扩IO资源-CSDN文库