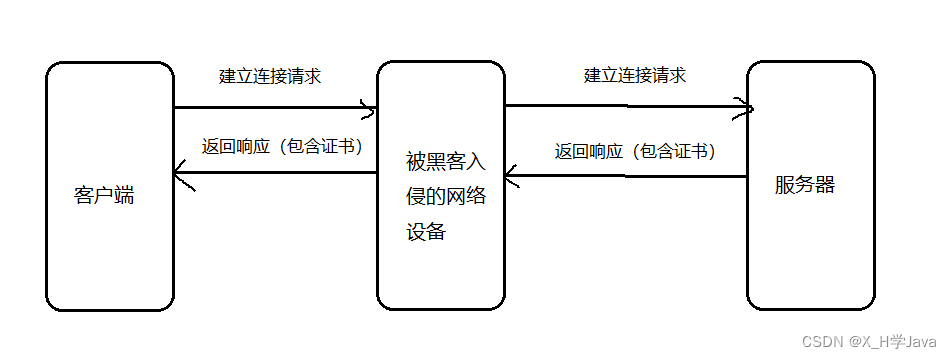

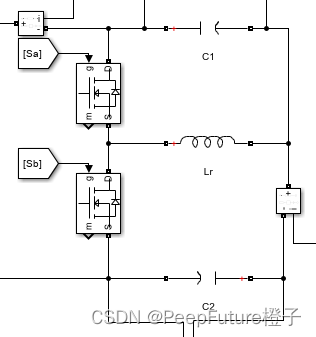

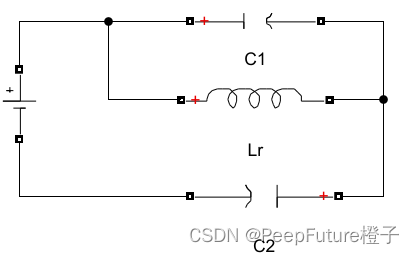

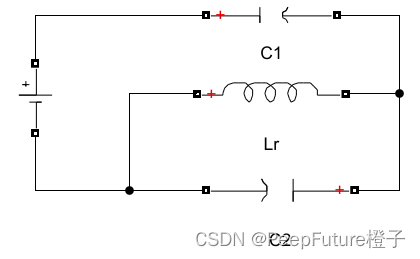

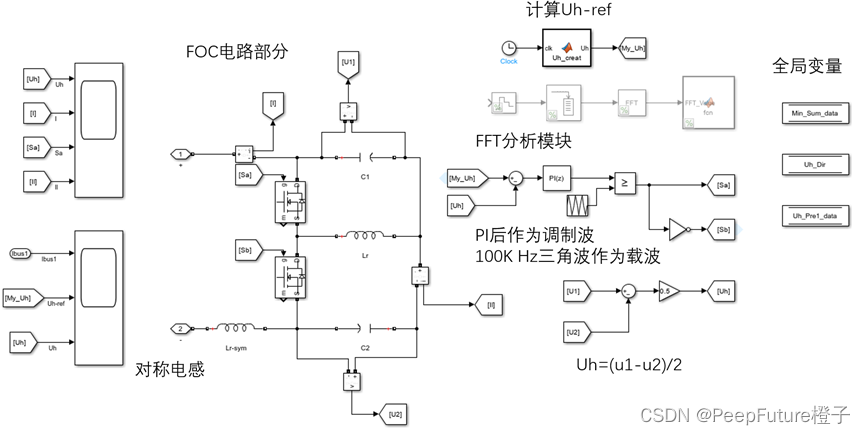

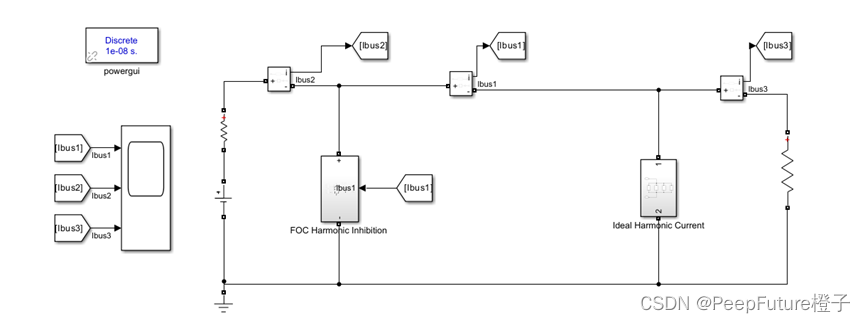

Foc电路如下图

当Sa导通时 Dc电压全被C2吃了 Lr电流向→

当Sb导通时 Dc电压全被C1吃了 Lr电流向←

假设C1=C2=C,开关频率接近无穷、占空比为50%时

Uc1=Uc2=Udc/2、Ilr=0

当占空比D>50%,Uc2增大,Ilr→增大

当占空比D<50%,Uc1增大,Ilr←增大

高频条件下相当于用SPWM控制的可变电流源

参数搭建

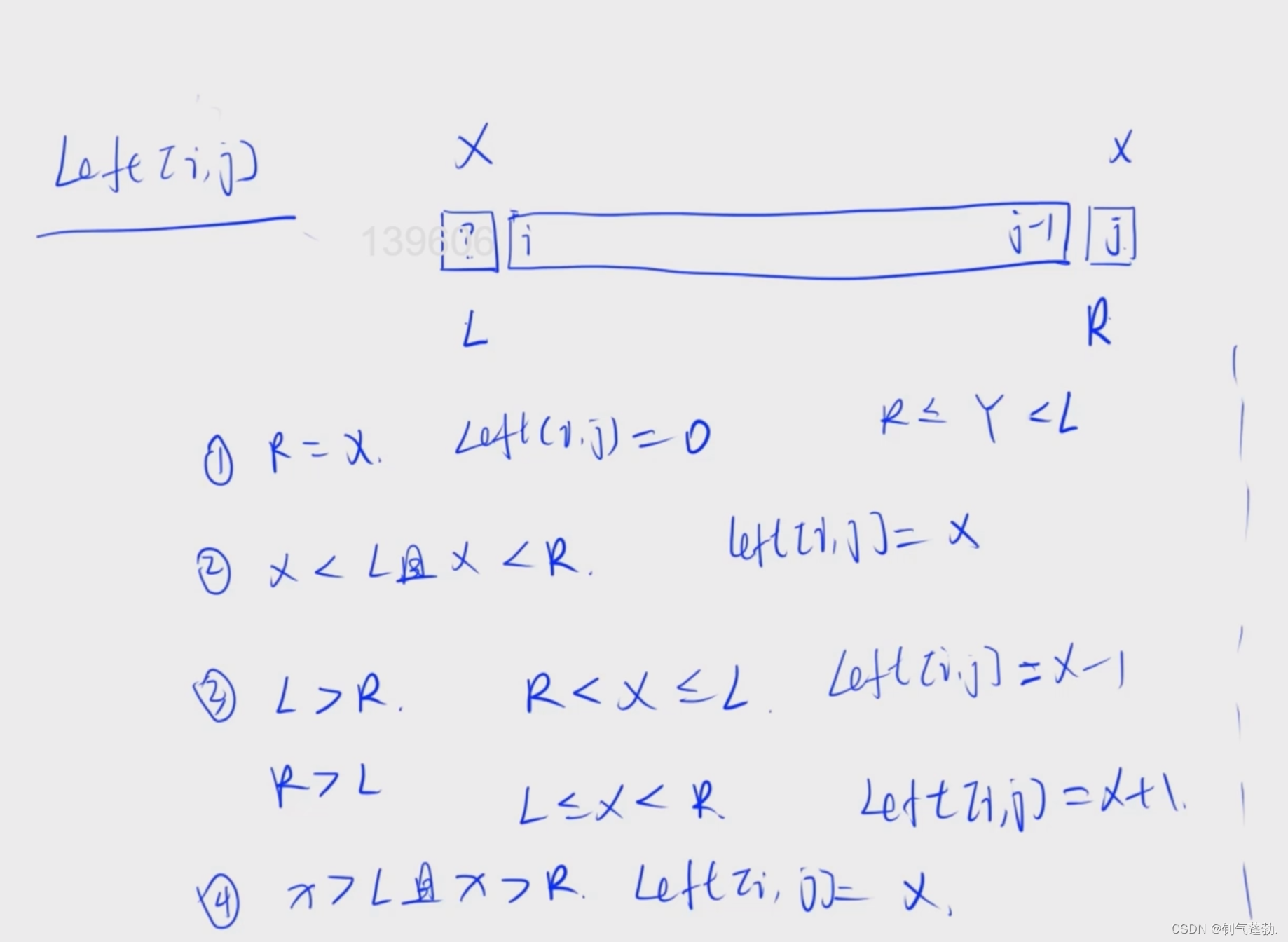

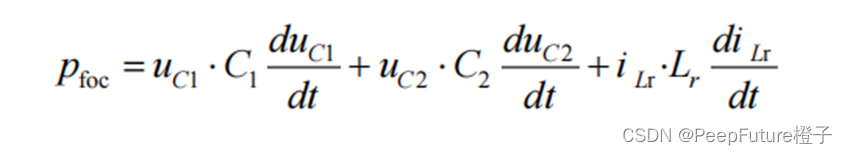

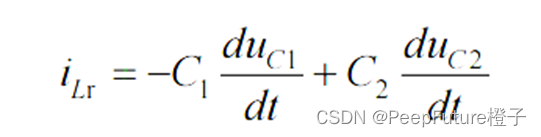

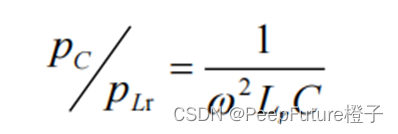

根据FOC电路可以得到以下关系式

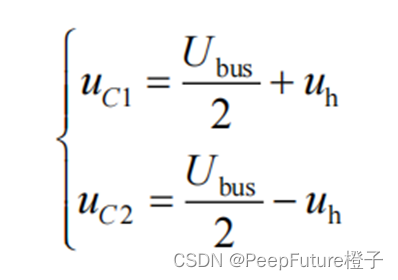

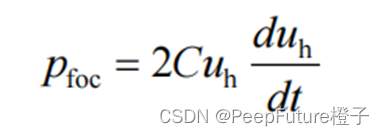

为了方便分析,我们引入Uh变量,此处引入Uh就是后面需要SPWM的调制波

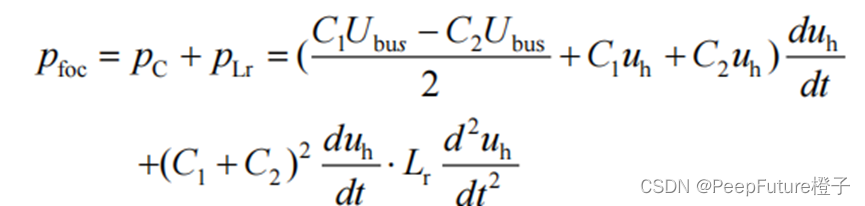

那么联立上面式子可以算出

为了方便计算,取C1=C2=C

又因为上式Lr、C取值都是1e-6级别,而频率为50Hz、100Hz级别,故PLr远小于Pc。那么可以将PLr忽略不计。

有了上面2个条件后,Pfoc可以化简为下式

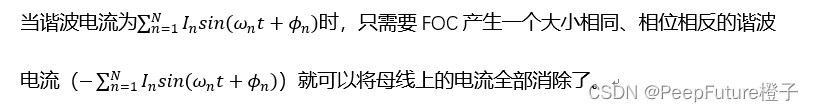

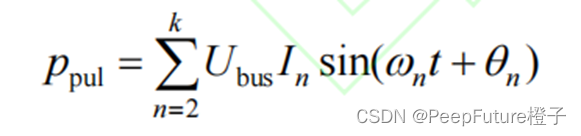

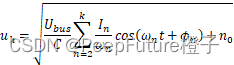

我们假设母线上的脉动功率为下式

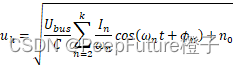

因为使得母线上的脉动功率与Pfoc上的瞬时功率大小相同,相位相反,那么联立求解Uh得到下式:

![]()

![]()

现在得到了Uh的通解(下式)

但是因为开根,相位信息丢失了,故要做波形变化

![]()

这里使用的策略是当前采样点大于某个阈值,上次采样点小于某个阈值,且时间不为0,那么可以判定上一个采样点是0点。

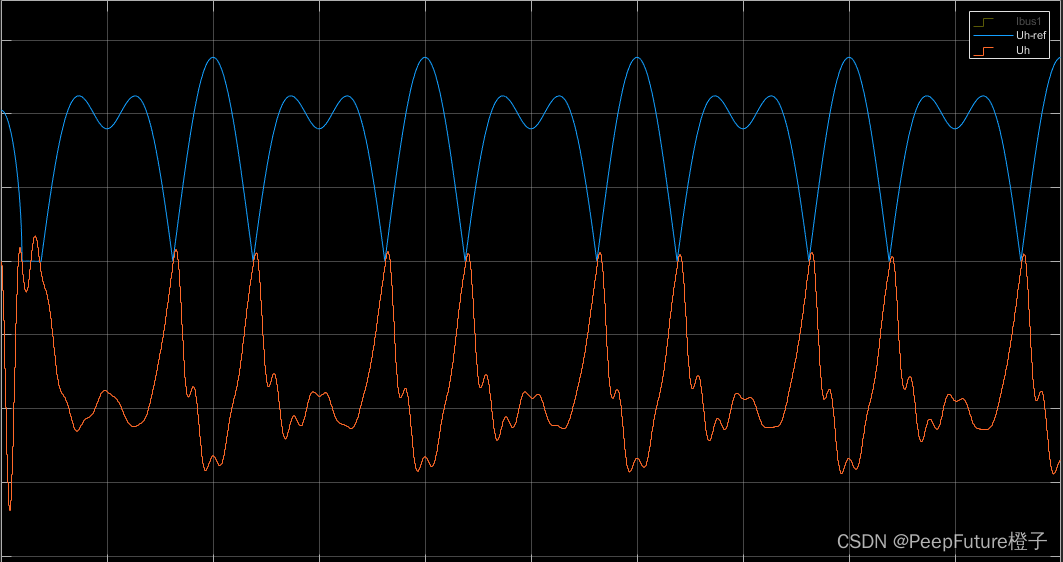

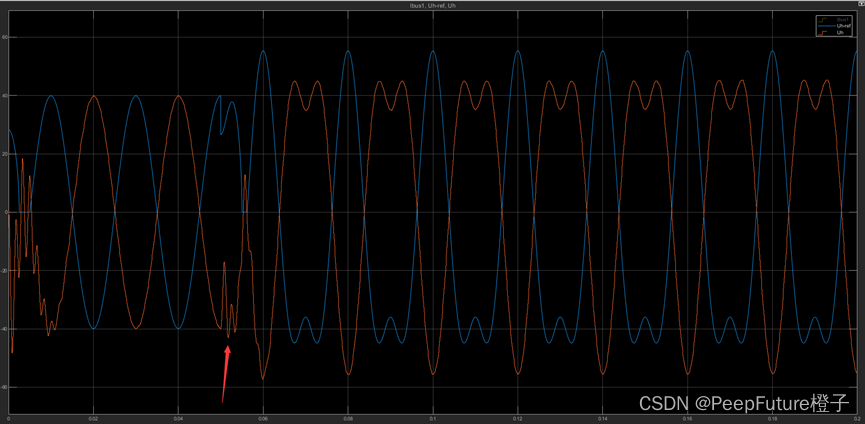

波形未变化(Uh和Uh-ref)

波形变化(Uh和Uh-ref)

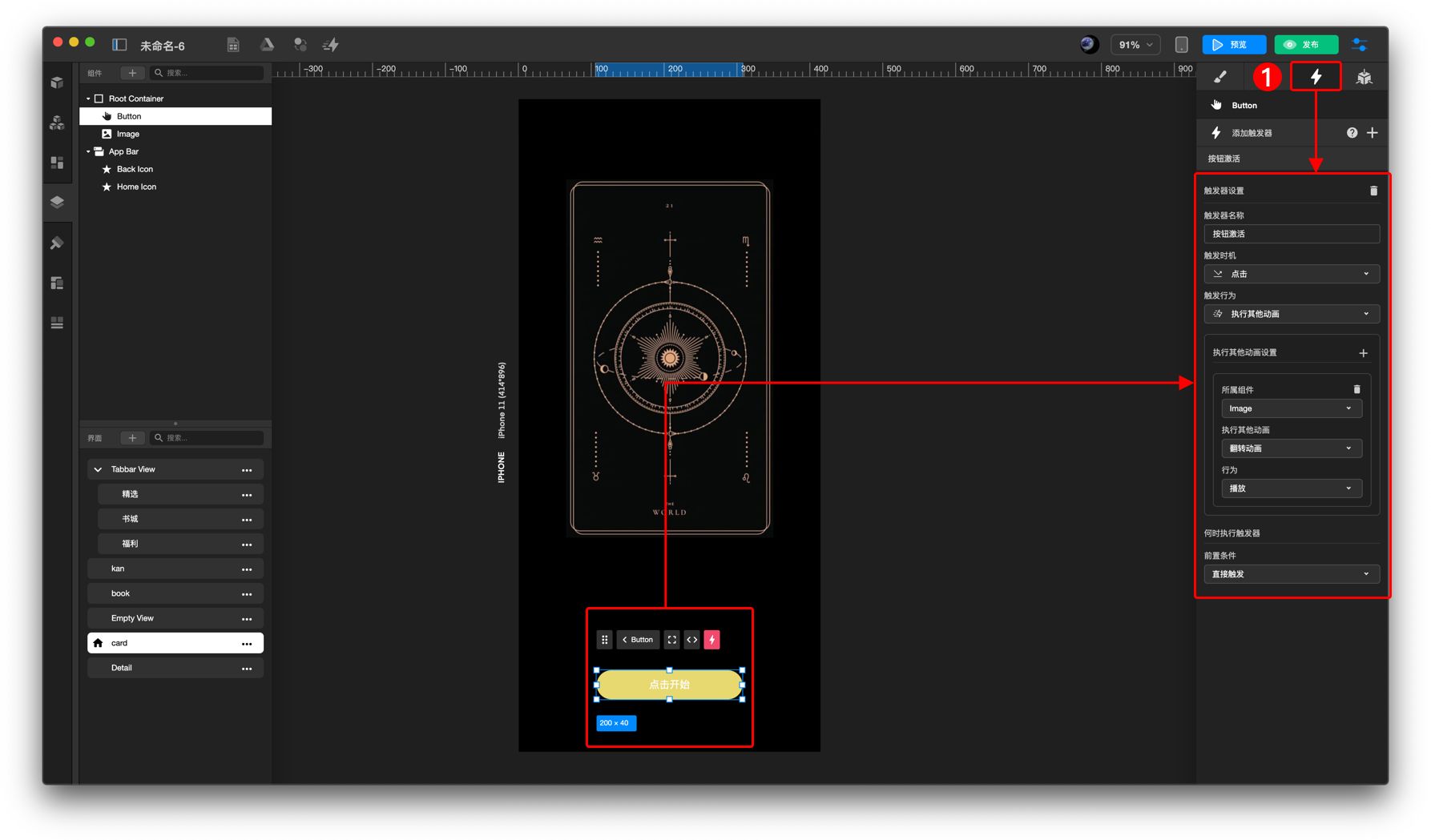

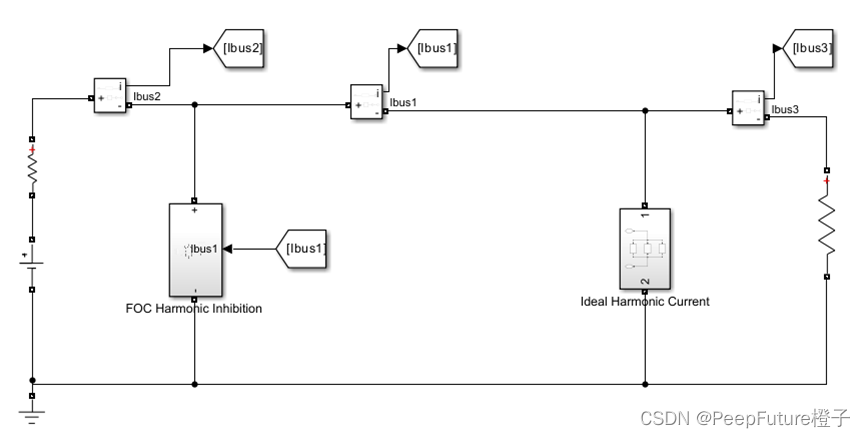

整体系统仿真框图

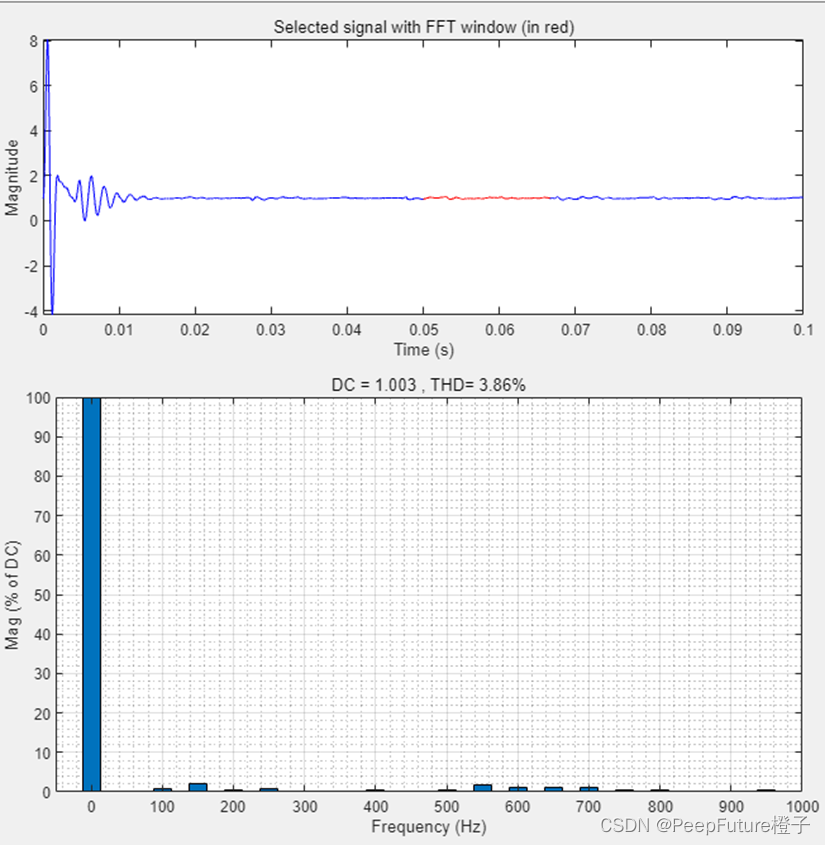

仿真效果

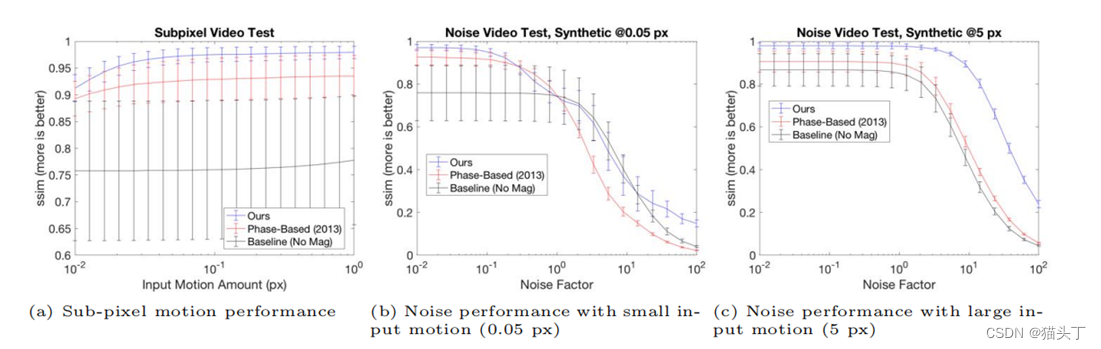

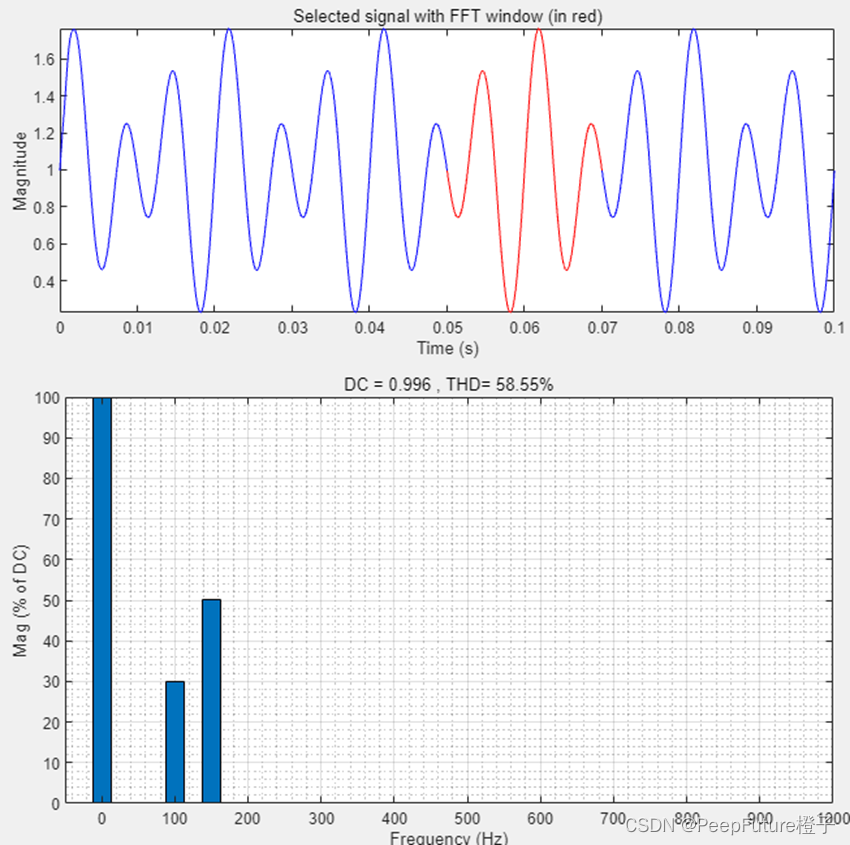

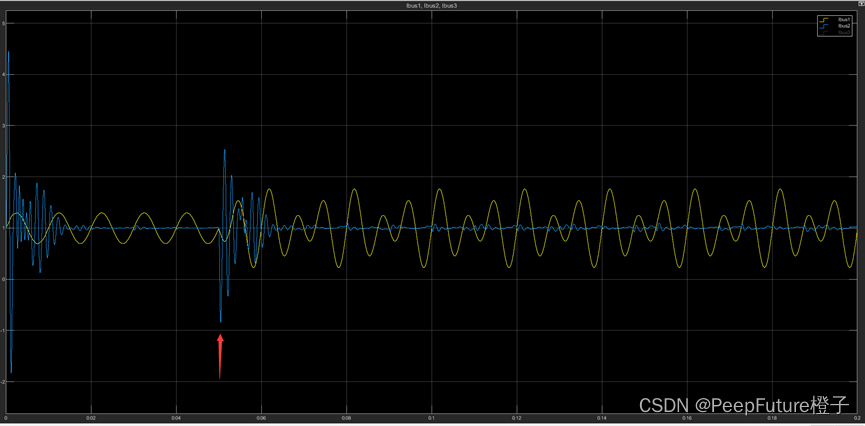

下图是FOC电路未抑制的母线电流

下图是FOC电路抑制后的母线电流

二次谐波由 0.3A(30.12%)降低到 0.007A(0.72%)

三次谐波由 0.5A(50.21%)降低到 0.022A(2.22%)

![]()

![]()

动态性能

原本只有2次谐波,在0.05s时加入3次谐波后抑制效果如上图,可以看到大概过0.02s后母线谐波电流又被重新抑制下去,也就是一个周期动态抑制母线谐波电流。

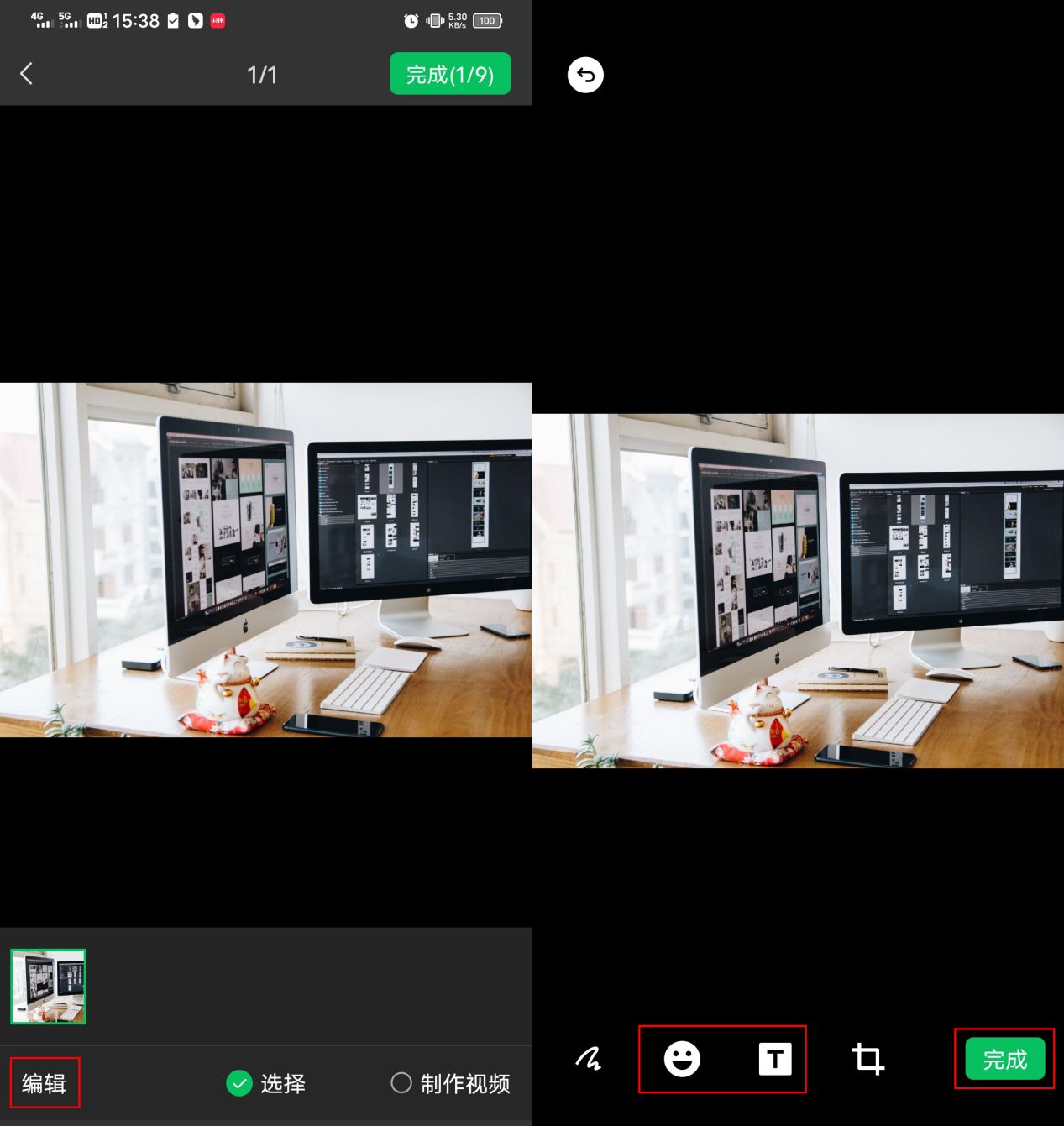

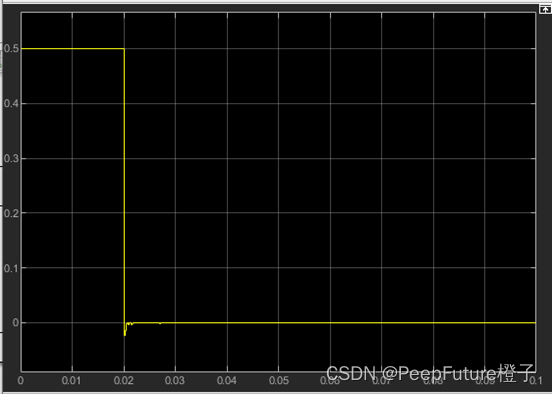

效率分析:

下图是P(有功):除开第一周期给电容充电(偏置电压 Ubus/2后 不消耗任何有功)

系统总体效率:99.71%,主要消耗在电源内阻和线路电阻上。