存储一致性是为了保证多线程背景下的访存顺序,多线程的语句是可以交错执行,使得顺序不同产生不同的执行结果。

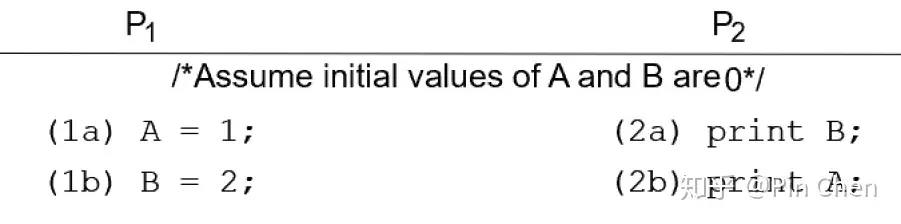

下面P2的输出结果可能是什么?

P1, P2两个线程的语句是可以交叉执行的,比如1a, 2a, 2b, 1b;一个线程内的语句,也是可以混序执行的,如P1: 1b, 1a,这取决于编译器和执行情况。所以,P2 print B, print A,会有0 0, 2 1, 0 1, 2 0四种结果。

若不控制mem consist,P2 print的B A会千奇百怪,甚至会有B 2, A 0。线程内内不遵循程序序,线程间也不

加控制,导致语句执行顺序为 1b 2a 2b 1a。

Sequential Consistency (SC)

-

所有线程的内存访问执行的顺序必须与程序中指令顺序一致

-

发出写操作后,发出线程等待写操作完成后再发出下一个内存操作

-

发出读操作后,发出线程等待读操作完成,并等待返回值的写操作完成后,然后再发出下一个操作

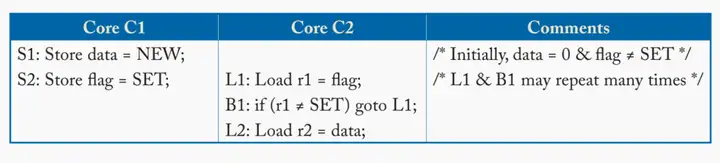

例子1

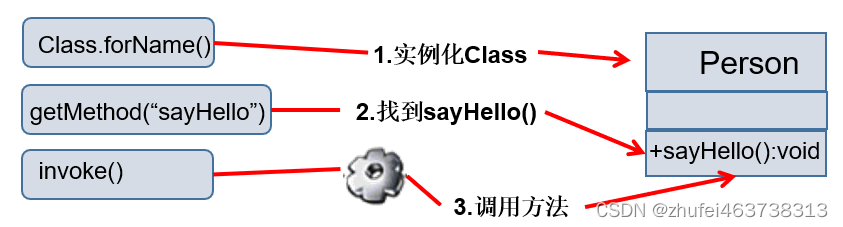

左边是核心C1的程序指定顺序,右边是核心C2的程序指定顺序,中间是实际的内存访问顺序。简而言之,不管是从哪个核心的角度,内存访问的顺序都是遵循程序指定顺序的 。

对于上述程序而言,只要是服从顺序一致性内存模型,最后程序的结果寄存器r2都能够拿到值NEW,唯一不能确定的是执行指令L1的次数。

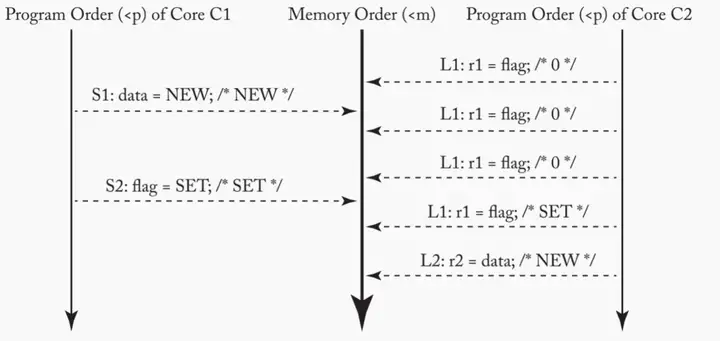

例子2

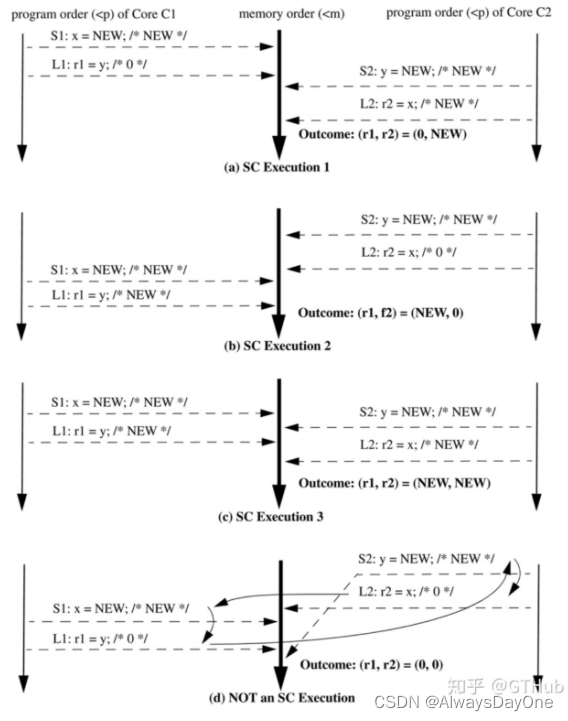

以下为sc与非sc满足的例子:

左侧为Core 1,右侧为Core 2的指令顺序。只有d出现线程内部访存顺序不符合程序指令顺序,就是不符合SC的。

参考

https://zhuanlan.zhihu.com/p/161275959?utm_id=0

https://zhuanlan.zhihu.com/p/521775447