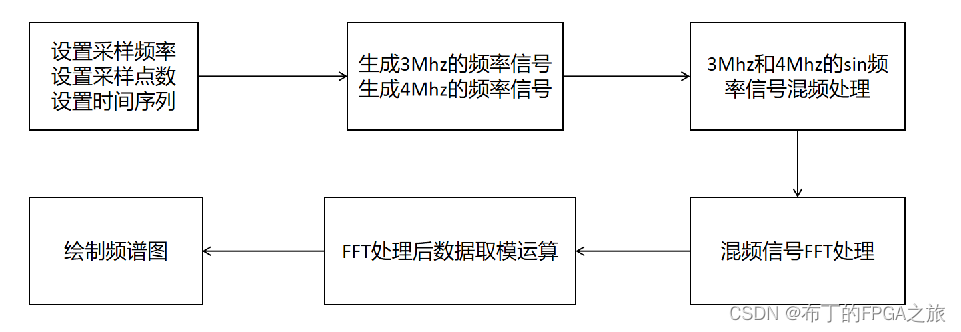

一 、FFT设计验证思路

1、基于Matlab与FPGA的混频sin信号的FFT验证,分别在Matlab和FPGA开发环境上实现相同的FFT功能设计。

2、Matlab平台开发,使用自带的fft函数与相关操作函数,绘制出混频sin信号,经过fft功能处理后的频谱图。

3、FGPA平台开发,通过dds ip核和乘法ip核,生成与Matlab相同配置的混频sin信号,借助于fft ip核实现fft的功能,对于输出的fft数据,寻找1024点中的四个峰值,并与Matlab的频谱图比对,从而确定FPGA开发验证的结果。

二、Matlab FFT功能设计开发

1、Matlab开发平台

①1024点FFT功能,采样频率50M;

②输入数据,3Mhz和4Mhz的sin信号混频;

③matlab自带fft公式计算fft数据;

④对fft数据取模运算,并绘图

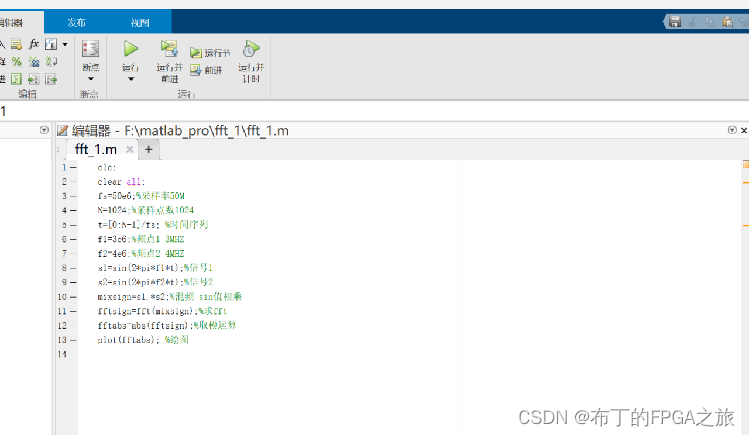

2、Matlab源码

clc;

clear all;

fs=50e6;%采样率50M

N=1024;%采样点数1024

t=[0:N-1]/fs; %时间序列

f1=3e6;%频点1 3MHZ

f2=4e6;%频点2 4MHZ

s1=sin(2pif1t);%信号1

s2=sin(2pif2t);%信号2

mixsign=s1.*s2;%混频 sin值相乘

fftsign=fft(mixsign);%求fft

fftabs=abs(fftsign);%取模运算

plot(fftabs); %绘图

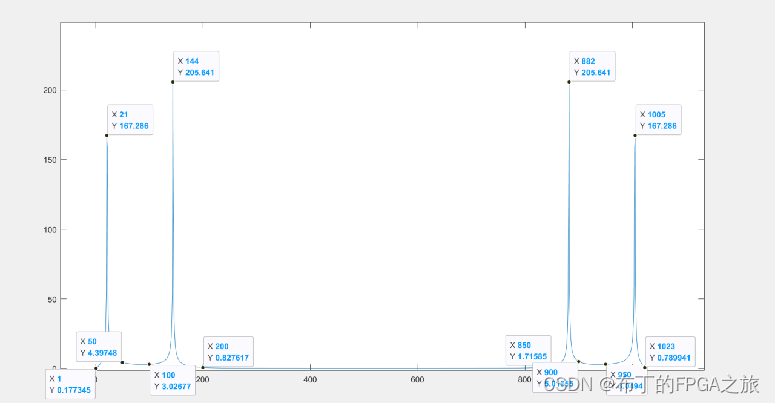

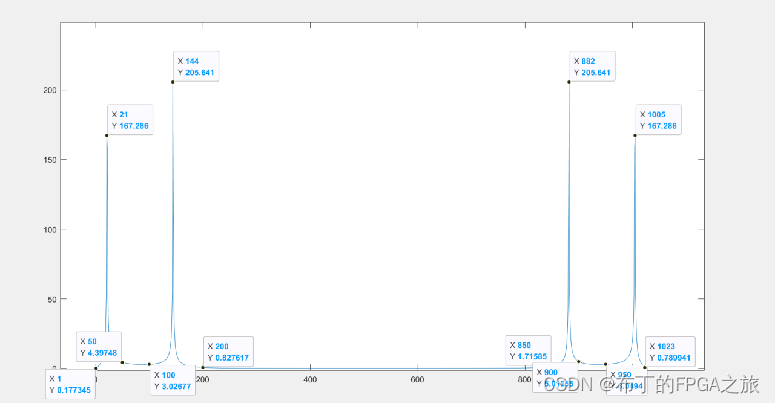

3、Matlab绘制频谱图结果

对频谱图的四个峰值横坐标结果以及所出的范围进行标识,用于FPGA平台的FFT处理结果验证比对。

第一个峰值:21,搜索范围:1——50;

第二个峰值:144,搜索范围:100——200;

第三个峰值:882,搜索范围:850——900;

第四个峰值:1005,搜索范围:950——1023;

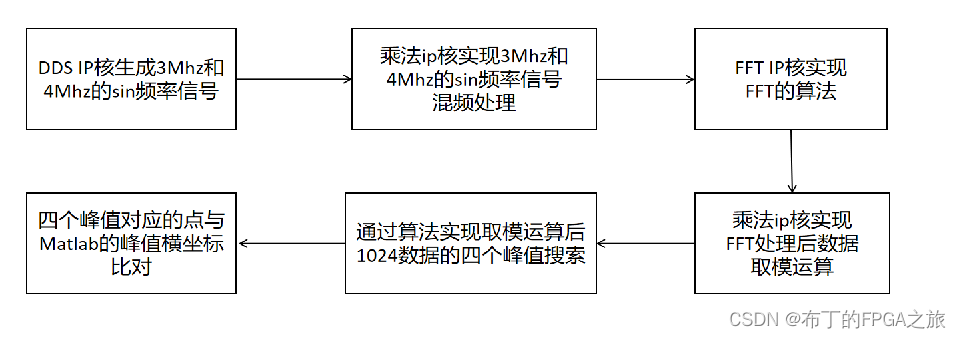

三、FPGA FFT功能设计开发

1、vivado开发平台(vivado 2019.2,其余版本按照步骤生成新工程即可)

①DDS IP核生成3Mhz和4Mhz的sin频率信号;

②乘法ip核实现3Mhz和4Mhz的sin频率信号混频处理;

③FFT IP核实现FFT的算法;

④乘法ip核实现FFT处理后数据取模运算;

⑤通过算法实现取模运算后1024数据的四个峰值搜索;

⑥四个峰值对应的点与Matlab的峰值横坐标比对

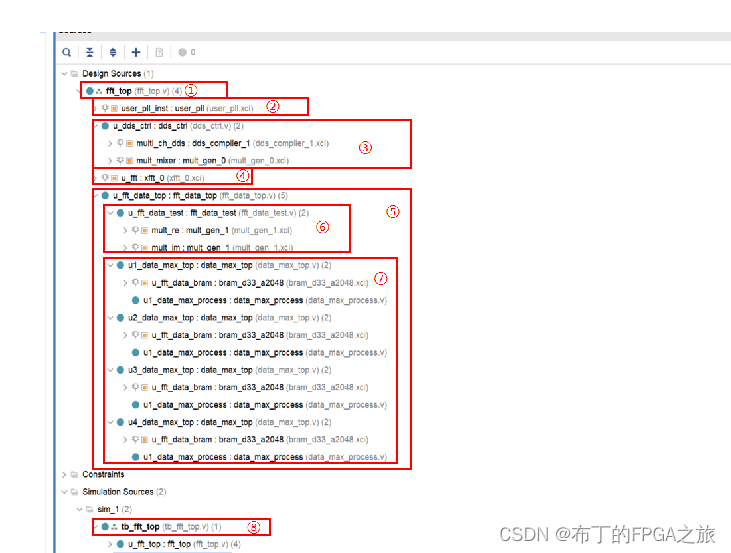

2、FFT工程设计

①顶层TOP,fft_top.v;

②内部时钟ip核用于产生50M和100M时钟;

③dds_ctrl控制模块,DDS IP核实现3Mhz和4Mhz的sin频率信号,以及乘法ip核实现3Mhz和4Mhz的sin频率信号混频处理;

④FFT IP核实现FFT的算法;

⑤FFT数据处理顶层模块,将四个峰值对应的点与Matlab的峰值横坐标比对;

⑥乘法ip核实现FFT处理后数据取模运算;

⑦通过算法实现取模运算后1024数据的四个峰值搜索;

⑧仿真文件

3、FFT工程设计中IP核配置

①时钟ip

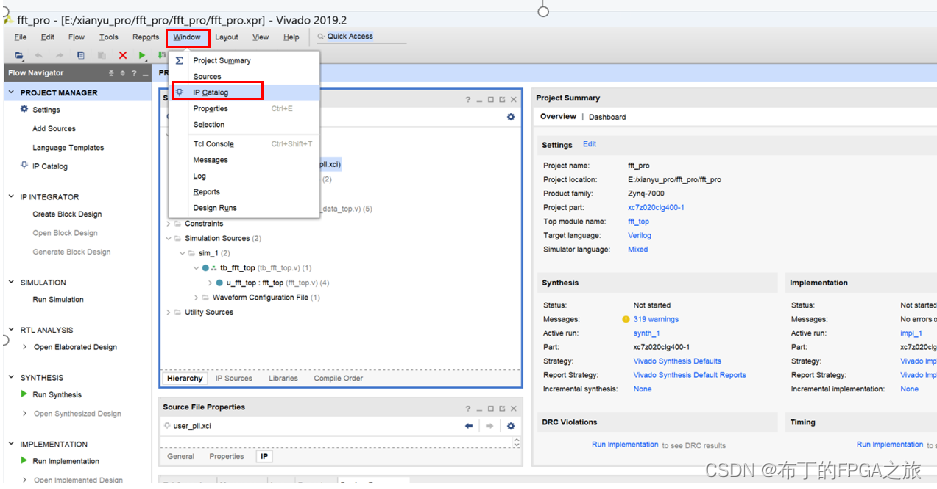

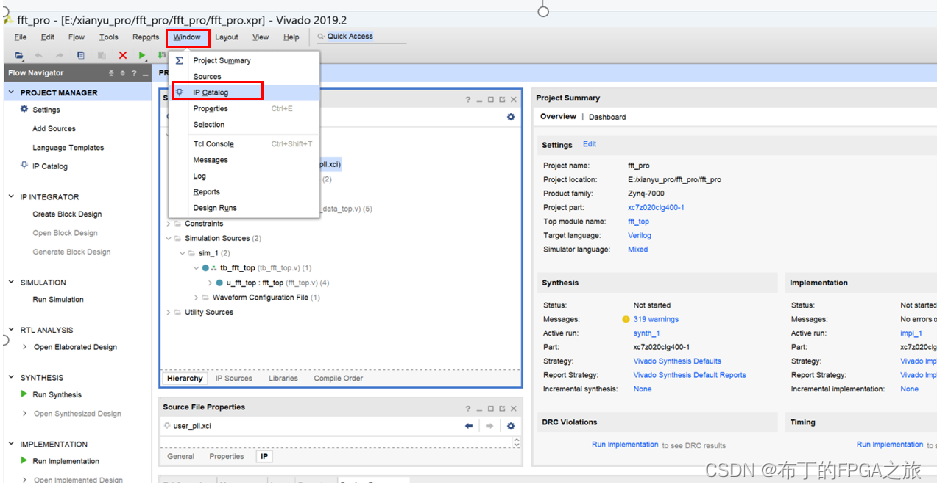

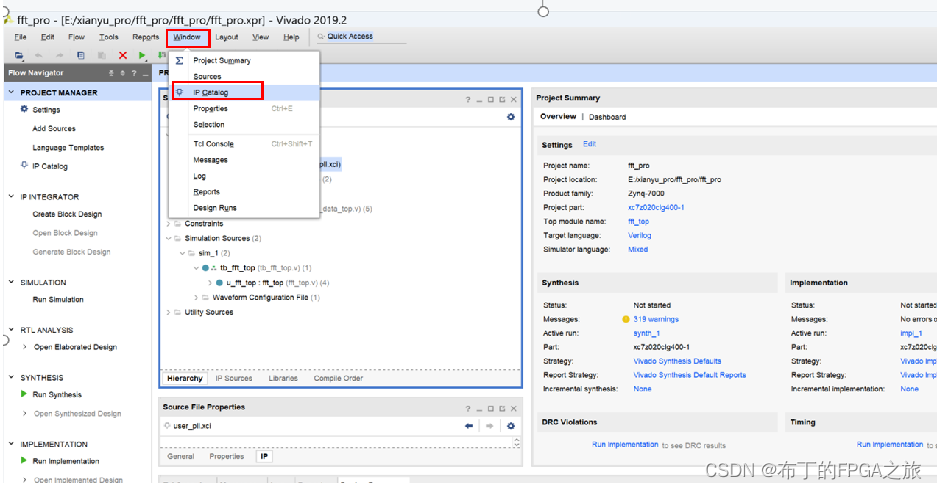

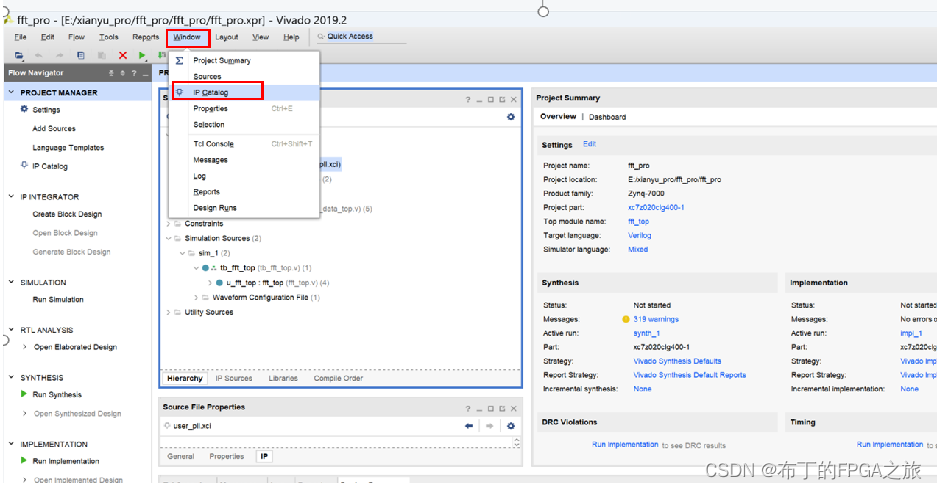

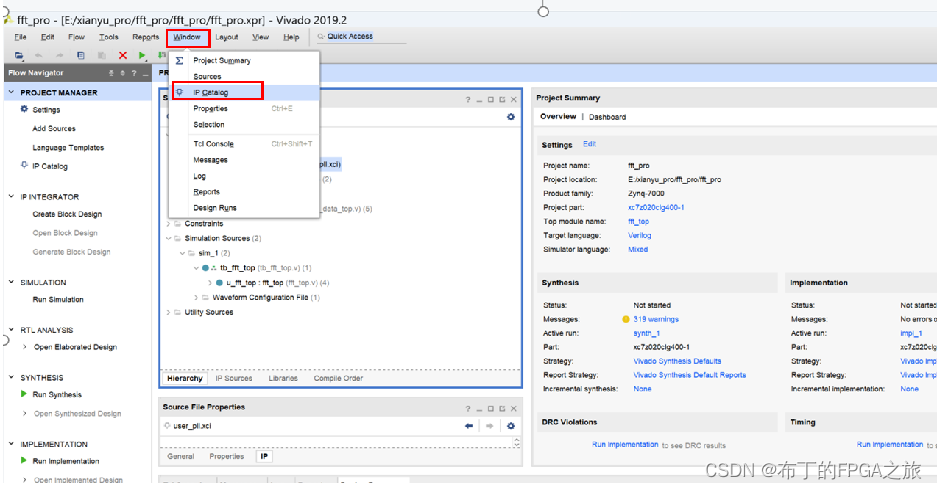

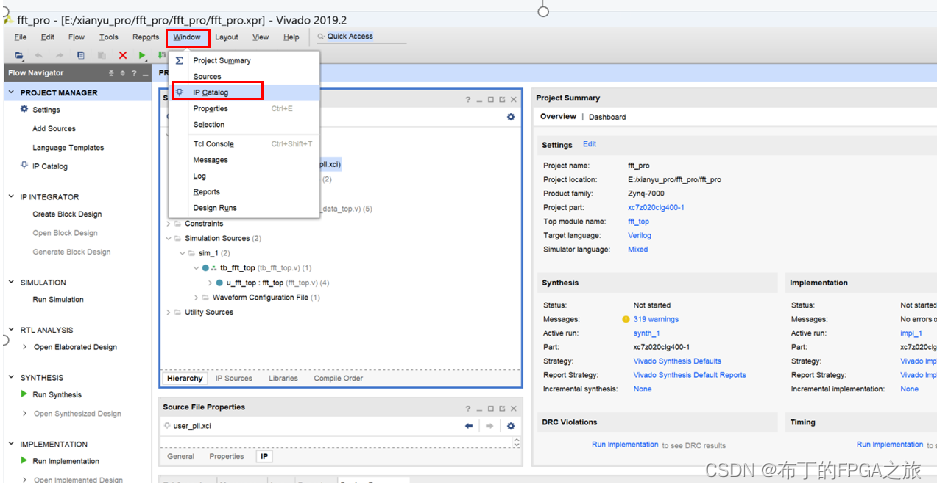

步骤1:打开IP Catalog,点击Window下IP Catalog

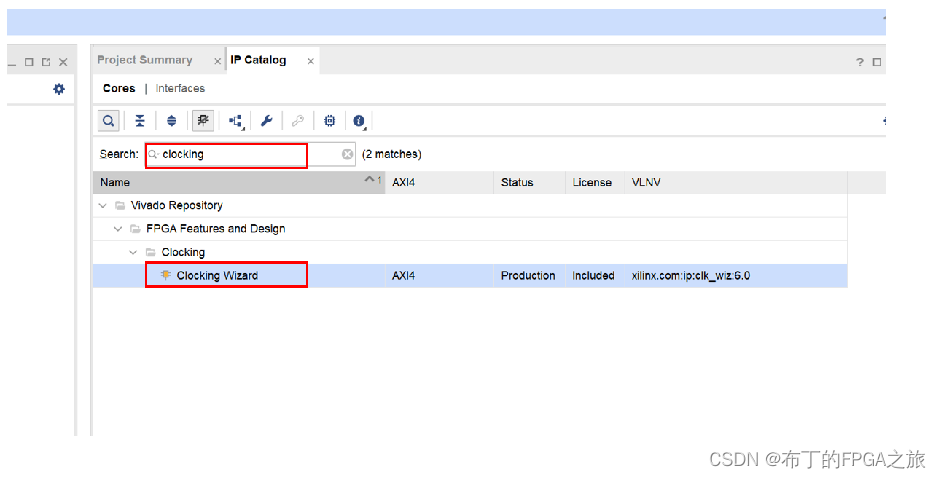

步骤2:查找时钟IP核 Clocking Wizard,搜索输入

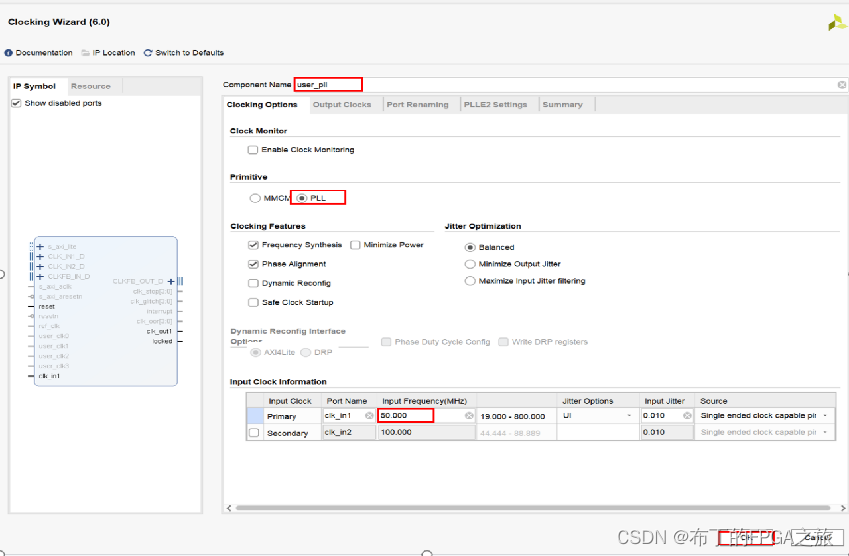

步骤3:时钟IP核 Clocking Wizard配置——Clocking Options,修改名称,选择PLL模式,设置输入时钟50M,可根据实际工程配置

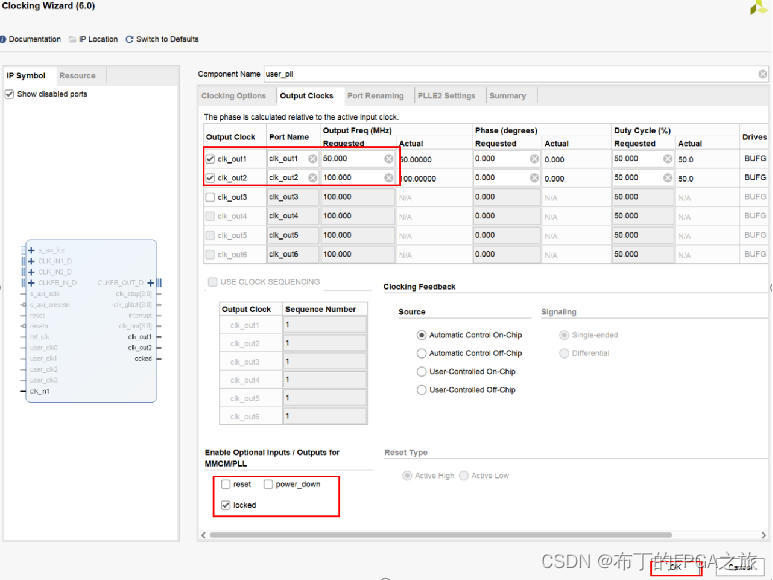

步骤4:时钟IP核 Clocking Wizard配置——Output Clocks,设置输出50M和100M,复位信号不使用,使用locked作为内部复位

②DDS ip

步骤1:打开IP Catalog,点击Window下IP Catalog

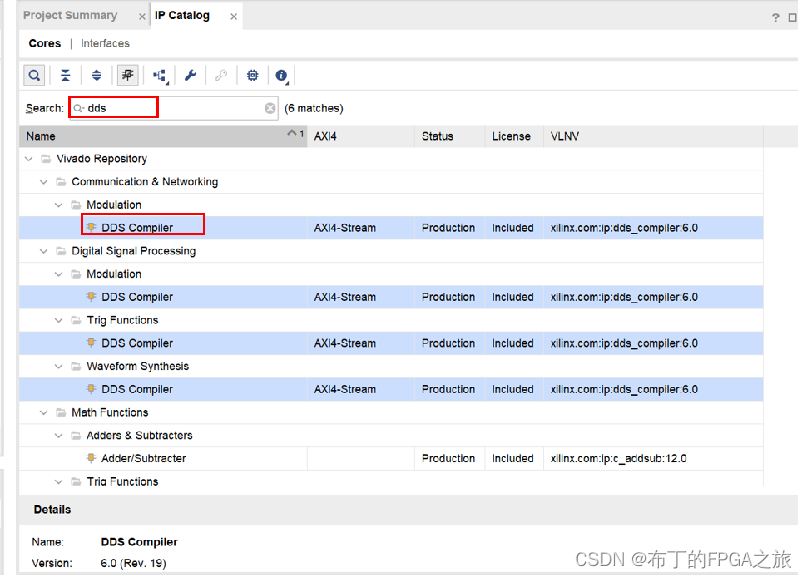

步骤2:查找dds IP核 dds compiler,搜索输入

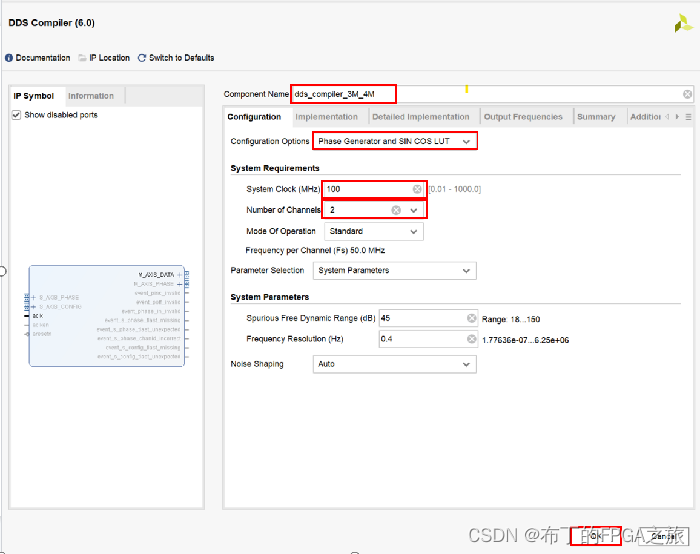

步骤3:dds IP核dds compiler配置——Configuration,修改名称,设置选择Phase Generator and SIN COS LUT,设置输入系统时钟100M,两路通道3M和4M

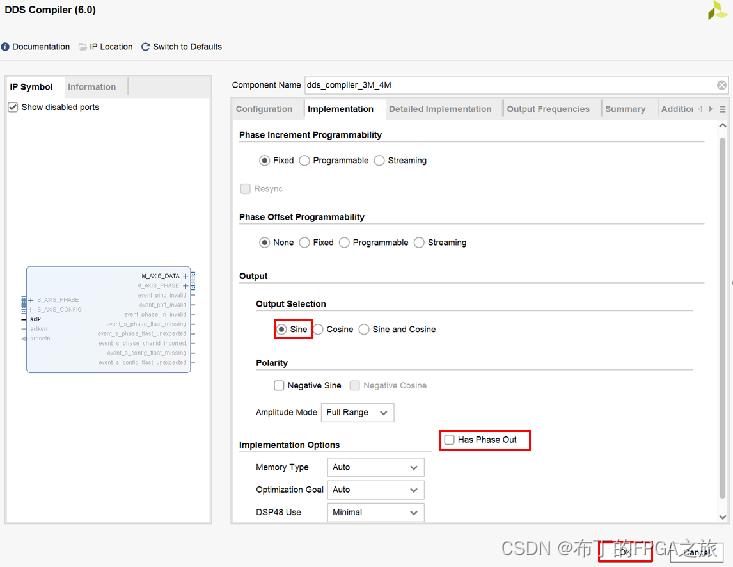

步骤4:dds IP核dds compiler配置——Implementation,Output 选择Sine模式,对比Matlab中sin信号,相位输出不使能

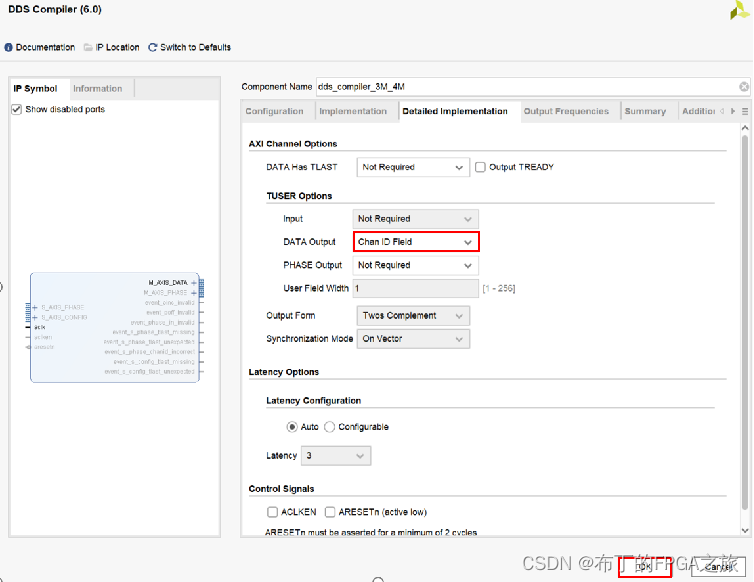

步骤5:dds IP核dds compiler配置——Detailed Implementation,DATA Output 选择Chan ID Field,对应两路输出3M和4M的sin信号

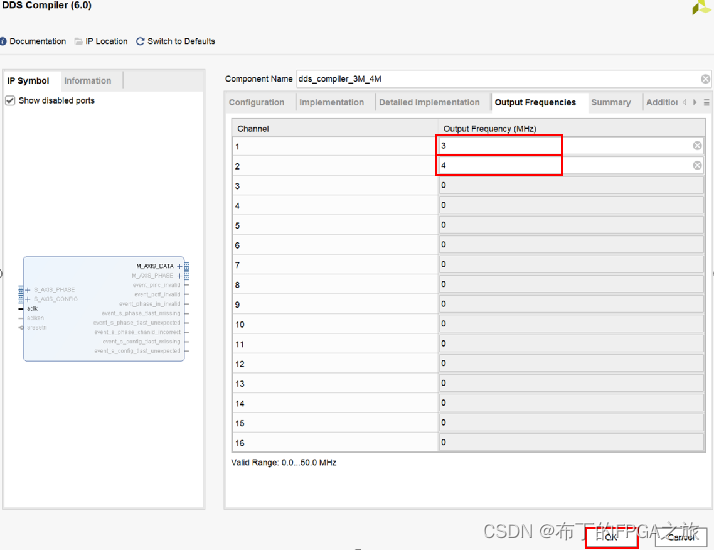

步骤6:dds IP核dds compiler配置——Output Frequencies,设置两路输出信号的频率3M和4M

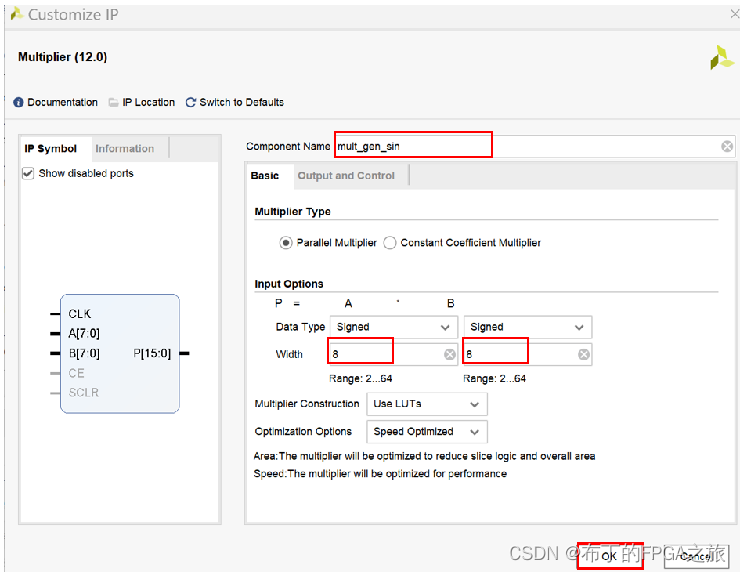

③乘法 ip(88)

步骤1:打开IP Catalog,点击Window下IP Catalog

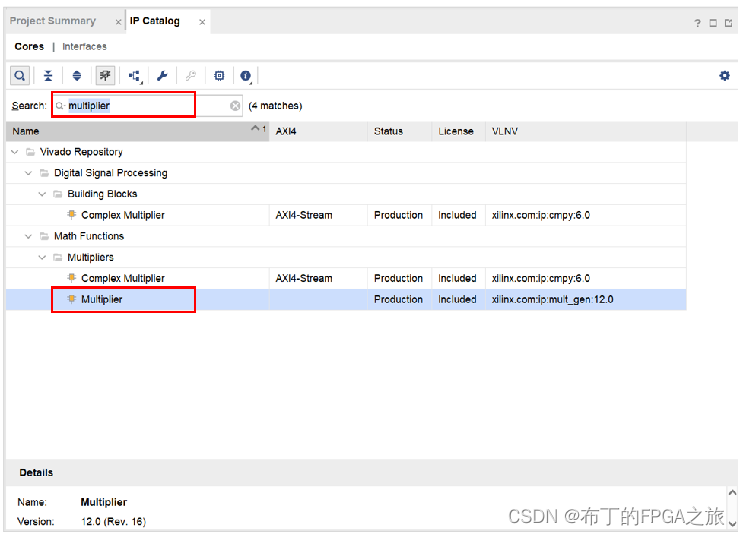

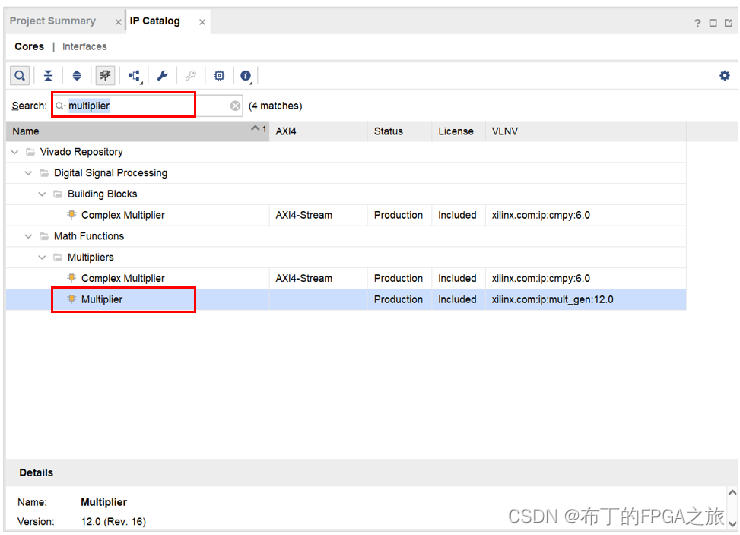

步骤2:查找乘法 IP核 multiplier,搜索输入

步骤3:乘法 IP核 multiplier配置——Basic,修改名称,设置输入数据的位宽8

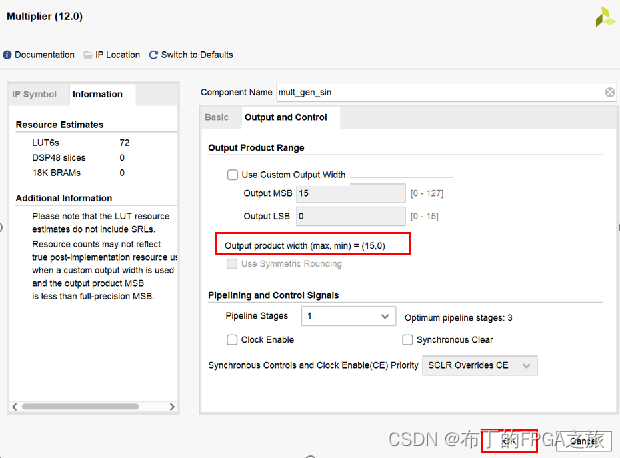

步骤4:乘法 IP核 multiplier配置——Output and Control,无需设置,只需要关注输出数据的最高位MSB和最低位LSB,方便其他模块使用乘法ip的输出数据

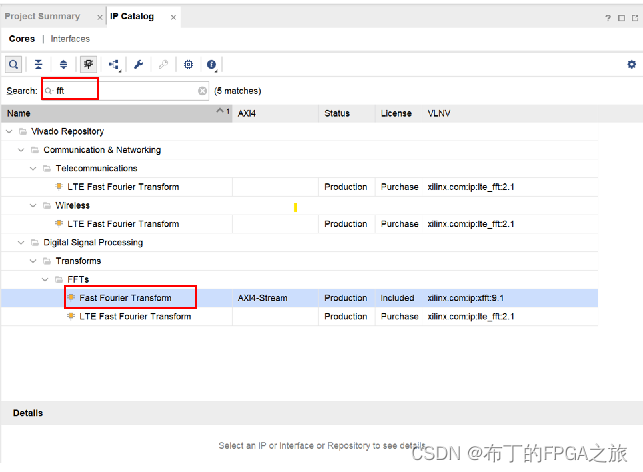

④fft IP核 Fast Fourier Transform

步骤1:打开IP Catalog,点击Window下IP Catalog

步骤2:查找fft IP核 Fast Fourier Transform,搜索输入

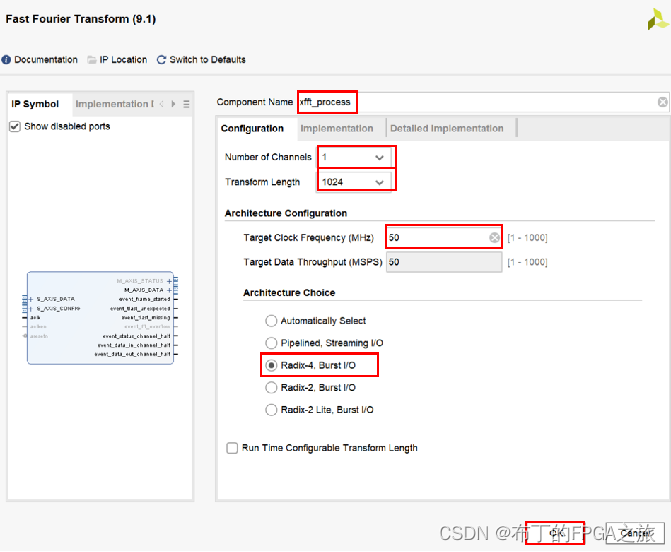

步骤3:fft IP核配置——Configuration,修改名称,设置通道,传输的数据1024,设置Target Clock Frequency,采样率50M,选择基4突发结构

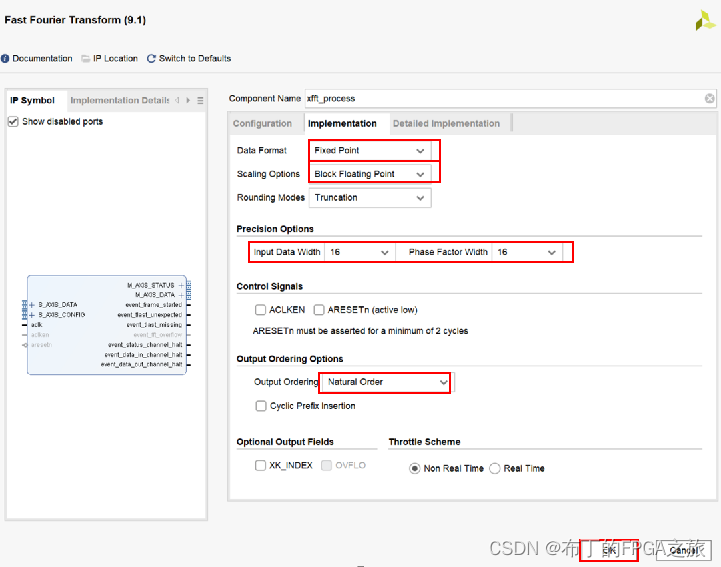

步骤4:fft IP核配置——Implementation,数据格式选择定点数类型,放缩设置为块浮点模式, 输出 FFT 结果选择顺序输出

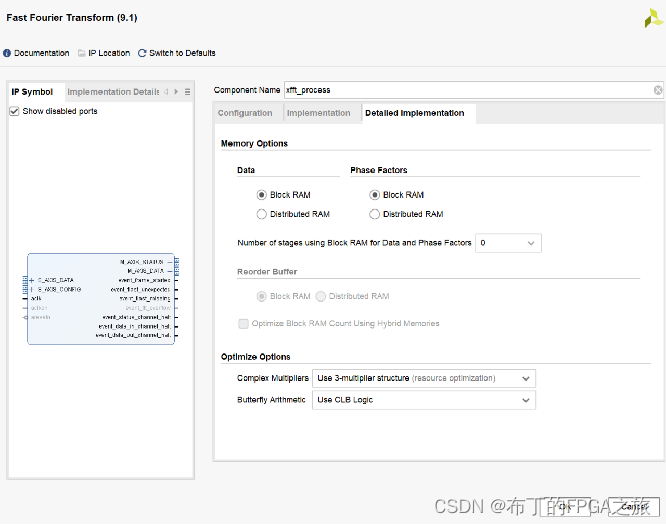

步骤5:fft IP核配置——Detailed Implementation

步骤6:fft IP核——Implementation Details

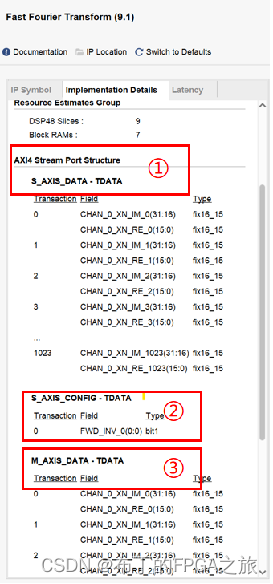

①输入给fft ip核的axi4_stream接口的计算数据,fft ip作为slaver,来自dds ctrl;CHAN_0_XN_IM_0(31:16)是复数的虚部,CHAN_0_XN_RE_0(15:0)是复数的实部;

FFT混频信号只使用实部的信号,低 16 位赋值为乘法器输出值, 高 16 位赋值为 0;

②输入给fft ip核的axi4_stream接口的配置数据,fft ip作为slaver,1-正变换,0-逆变换

代码里需要设置配置数据为1,快速傅里叶正变换;

③fft ip核输出的axi4_stream接口的结果数据,fft ip作为master

将fft ip输出的数据的实部和虚部进行平方(通过乘法核实现)再相加

即可得到FFT处理后的频谱图

⑤乘法 ip(1616)

步骤1:打开IP Catalog,点击Window下IP Catalog

步骤2:查找乘法 IP核 multiplier,搜索输入

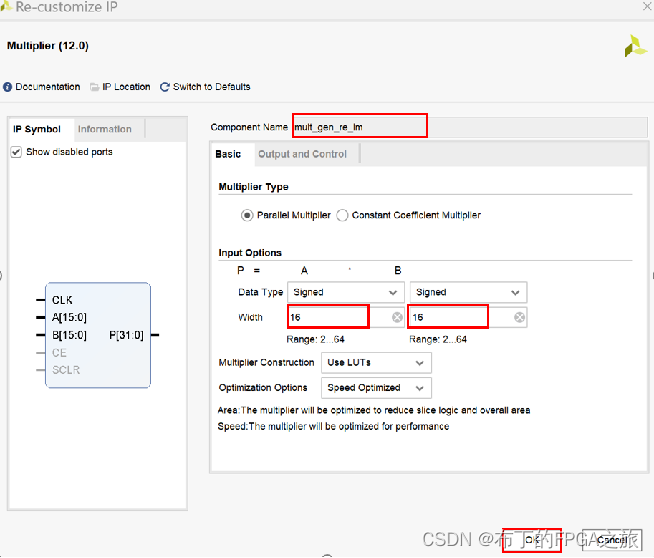

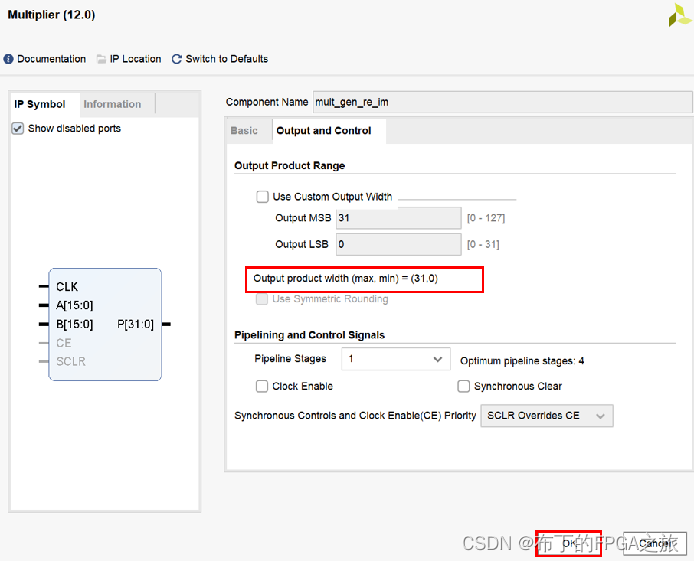

步骤3:乘法 IP核 multiplier配置——Basic,修改名称,设置输入数据的位宽16

步骤4:乘法 IP核 multiplier配置——Output and Control,无需设置,只需要关注输出数据的最高位MSB和最低位LSB,方便其他模块使用乘法ip的输出数据

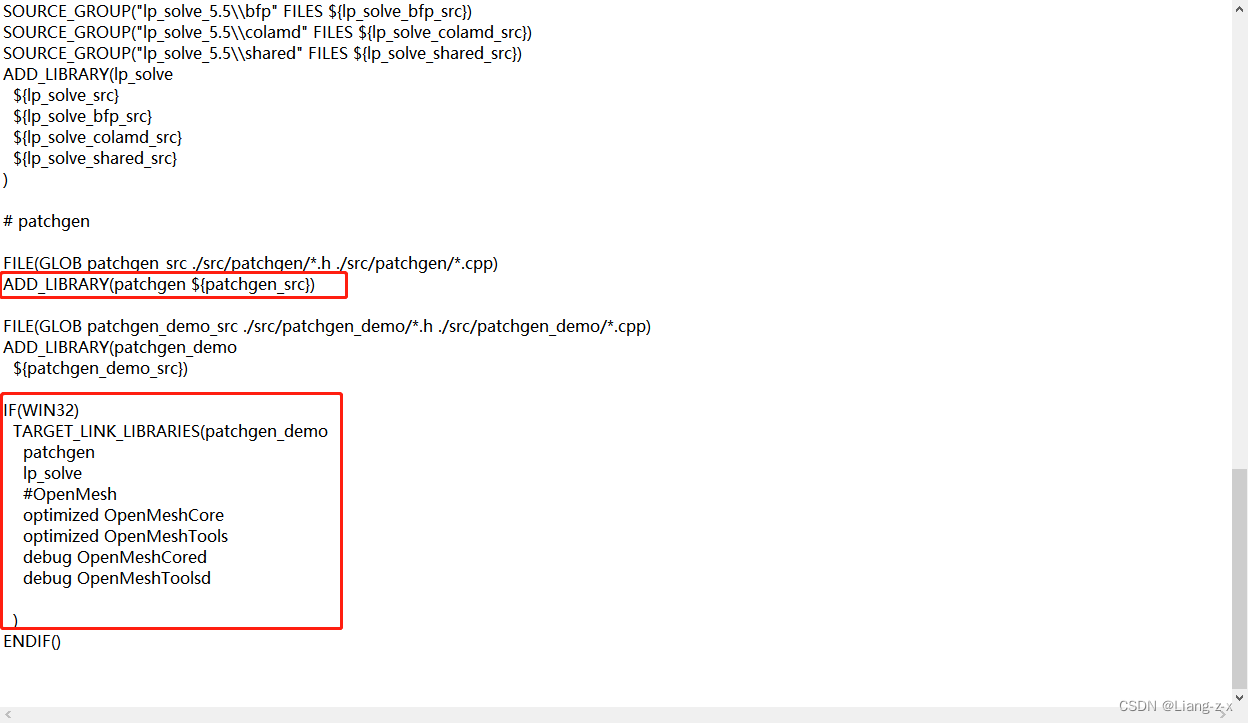

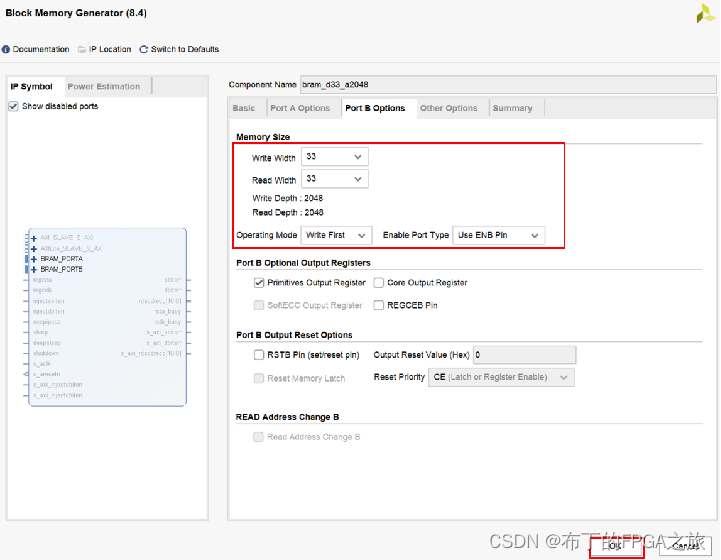

⑥Block Memory Generator ip

步骤1:打开IP Catalog,点击Window下IP Catalog

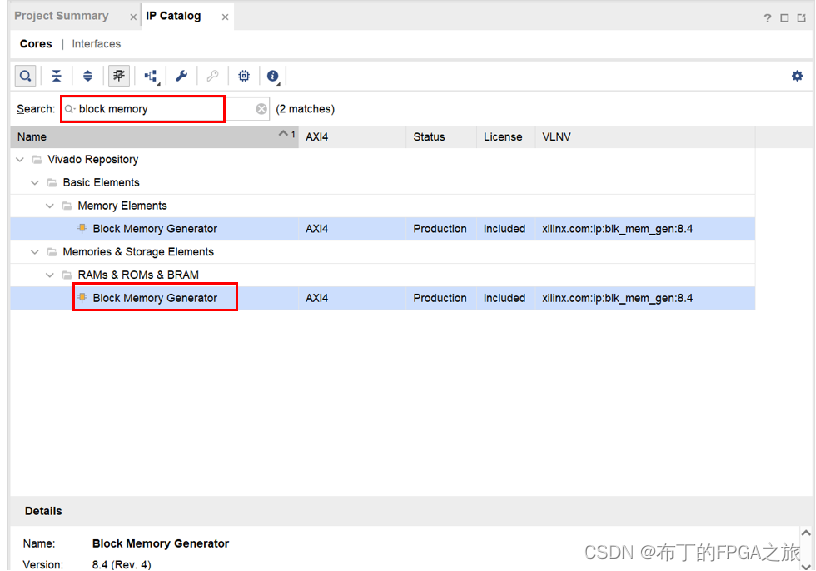

步骤2:查找块BRAM IP核 Block Memory Generator,搜索输入

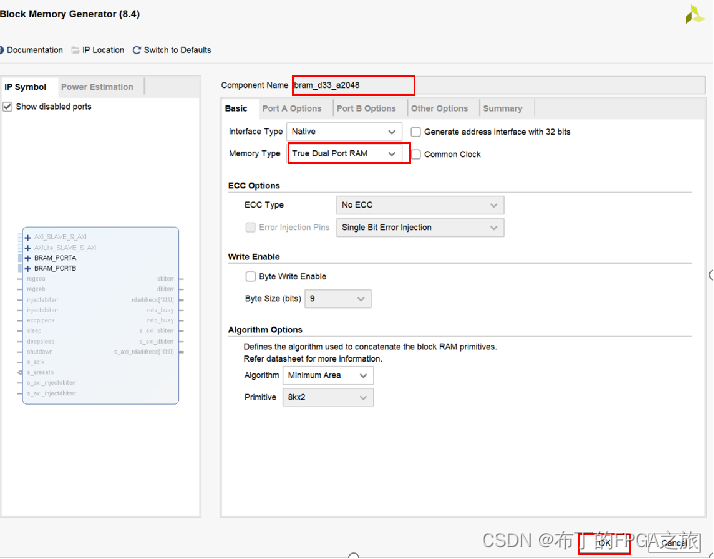

步骤3:块BRAM IP核 Block Memory Generator配置——Basic,设置Memory Type为真双端口

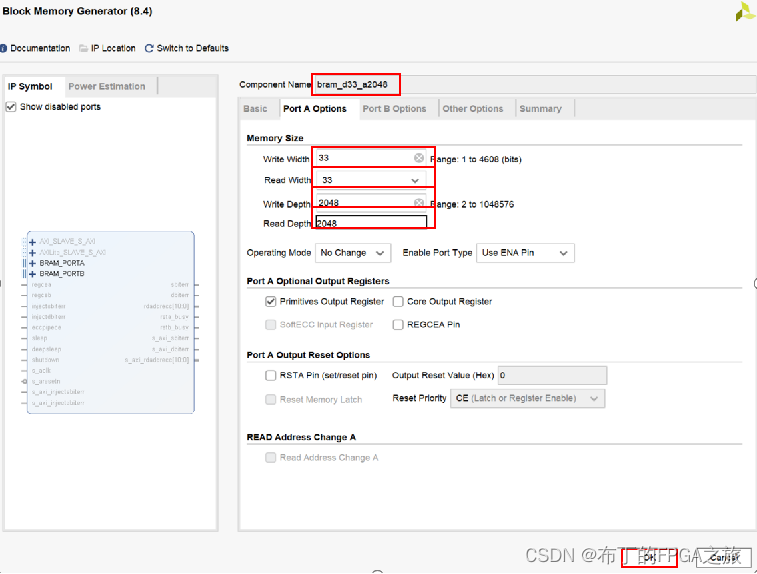

步骤4:块BRAM IP核 Block Memory Generator配置——Port A Options,设置写端口数据位宽33,深度2048;读端口数据位宽33,深度2048

步骤5:块BRAM IP核 Block Memory Generator配置——Port B Options,写端口数据位宽33,深度2048;读端口数据位宽33,深度2048(自动更新)

四、Matlab FFT功能与FPGA FFT功能结果比对

1、Matlab结果,四个峰值横坐标结果以及所出的范围进行标识

第一个峰值:21,搜索范围:1——50;

第二个峰值:144,搜索范围:100——200;

第三个峰值:882,搜索范围:850——900;

第四个峰值:1005,搜索范围:950——1023;

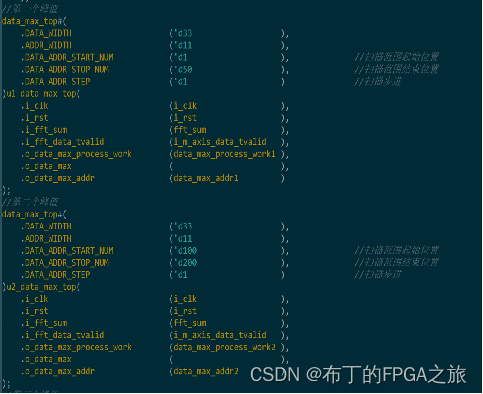

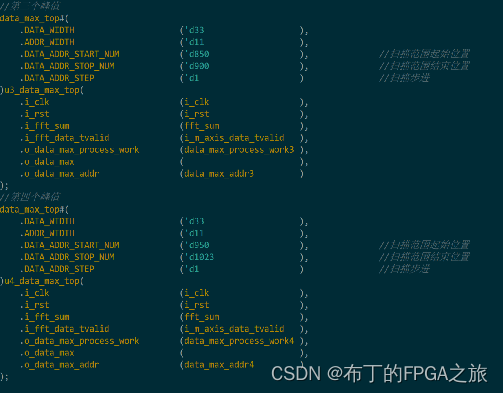

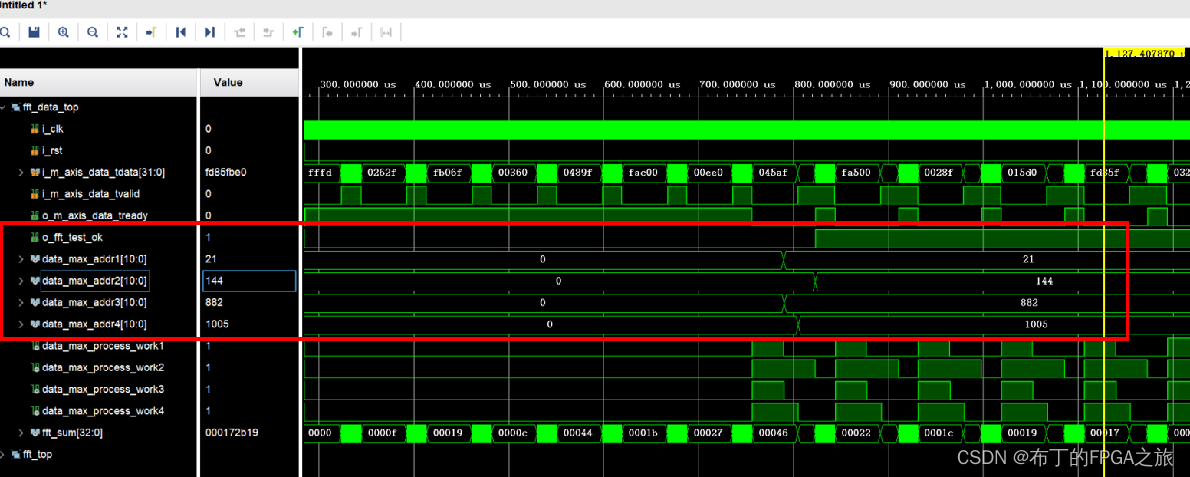

2、FPGA设置以及结果

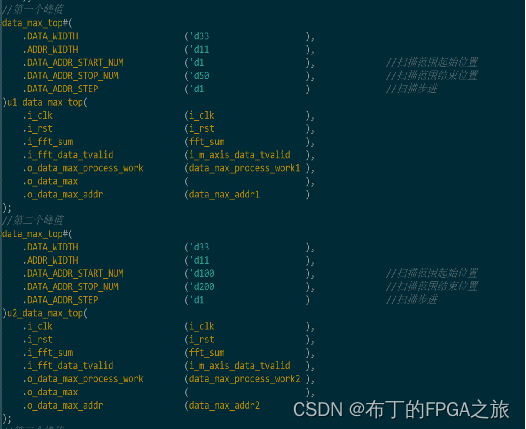

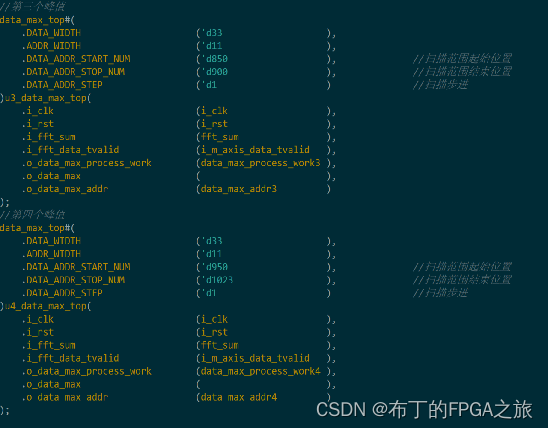

根据Matlab的结果,对应FPGA代码设置四个峰值的范围

3、FPGA仿真结果

第一个峰值:21;第二个峰值:144;第三个峰值:882;第四个峰值:1005;

五、FPGA最大值搜索算法及代码分析

1、搜索算法的调用及参数赋值

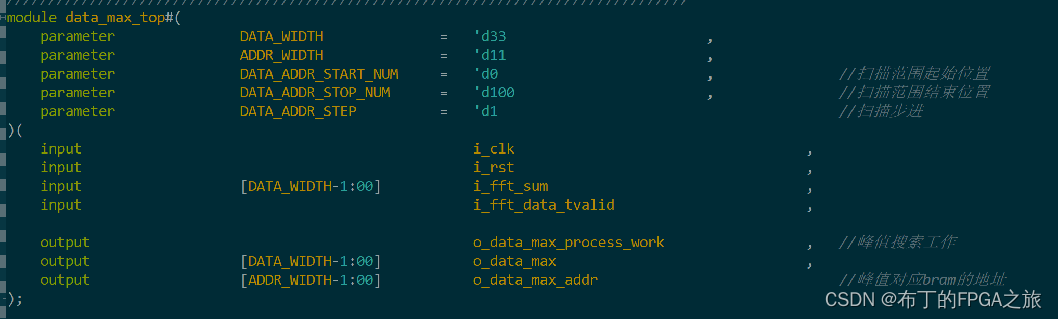

2、最大值搜索算法top的参数及端口——data_max_top

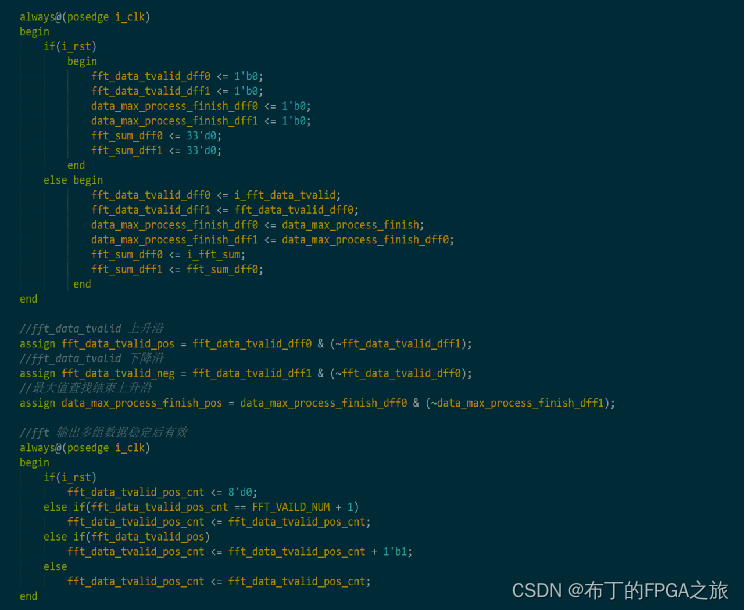

3、关键信号锁存及边沿检测

①每组1024个fft数据有效信号

(i_fft_data_tvalid)

②fft输出10组数据稳定后有效计数(fft_data_tvalid_pos_cnt)

③fft_data_tvalid 上升沿

(fft_data_tvalid_pos)

④fft_data_tvalid 下降沿

(fft_data_tvalid_neg)

⑤最大值查找结束信号

(data_max_process_finish)

⑥最大值查找结束上升沿

(data_max_process_finish_pos)

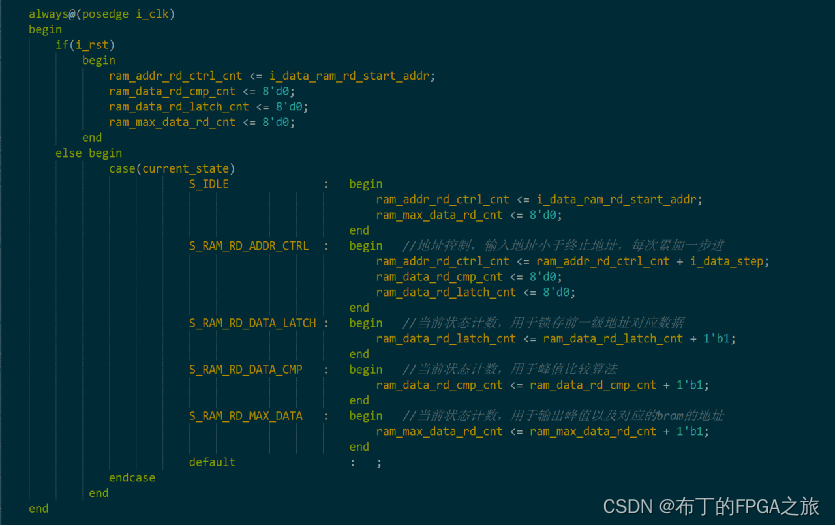

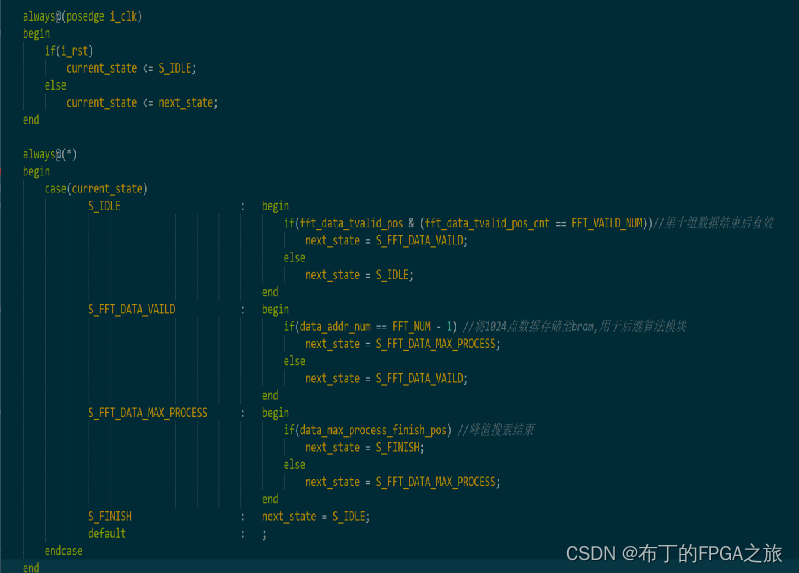

4、三段式状态机(第一段和第二段)

S_IDLE:空闲状态

S_FFT_DATA_VAILD:FFT数据有效

S_FFT_DATA_MAX_PROCESS:最大值数据存储处理过程

S_FINISH:算法处理结束

①第一段时序逻辑,状态锁存;

②第二段组合逻辑,用于状态跳转;

③第十组数据结束后并且下一组fft数据有效开始,状态由S_IDLE跳转至S_FFT_DATA_VAILD;

④S_FFT_DATA_VAILD:将1024点数据存储至bram,用于后继算法模块;

⑤峰值搜索结束,整个算法跳转至结束

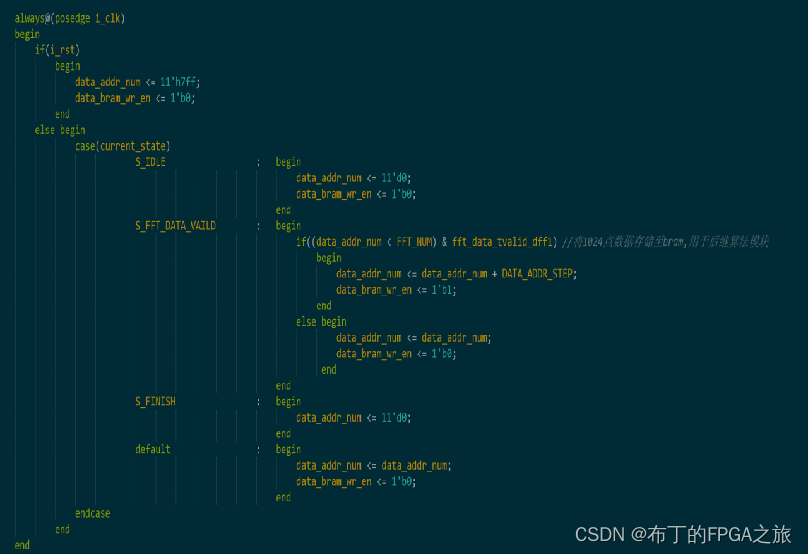

5、三段式状态机(第三段)

第三段时序逻辑处理,用RAM作为fft有效数据的存储,对应RAM的写地址、使能信号

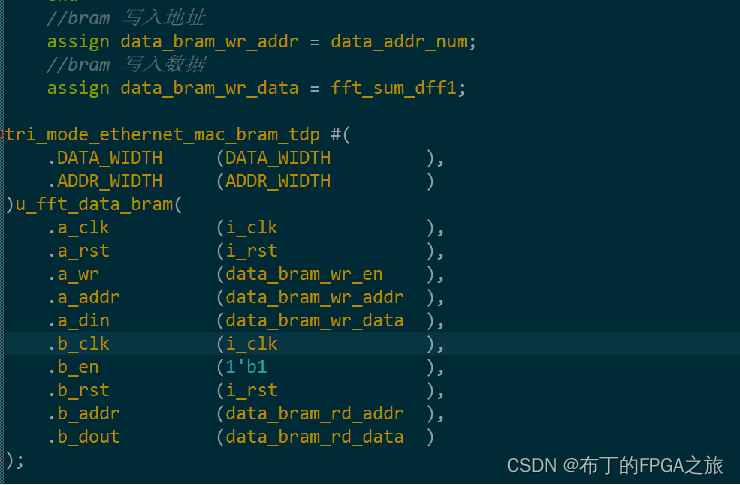

6、FFT有效数据的存储——RAM

采用lut逻辑搭建的RAM,数据位宽33,深度位宽11(2048数据>1024数据)

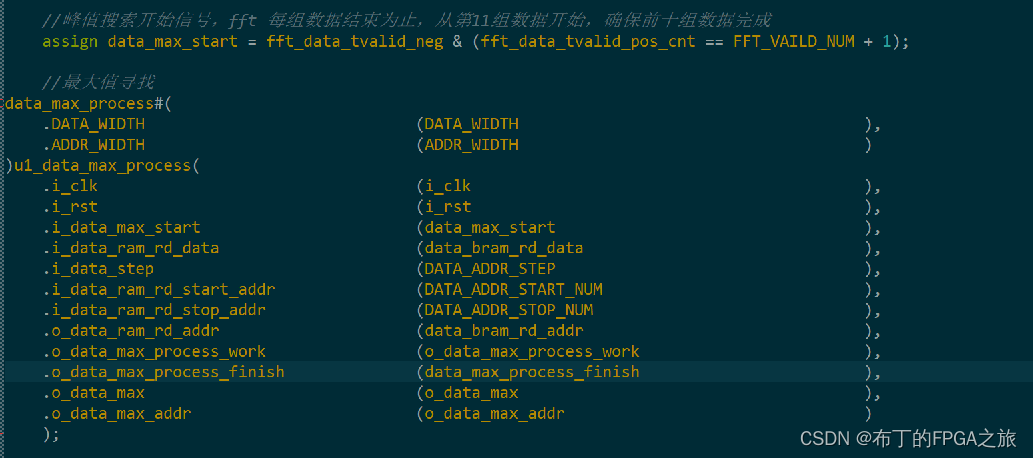

7、数据最大值处理(data_max_process)调用例化

峰值搜索开始信号,fft 每组数据结束为止,从第11组数据开始,确保前十组数据完成

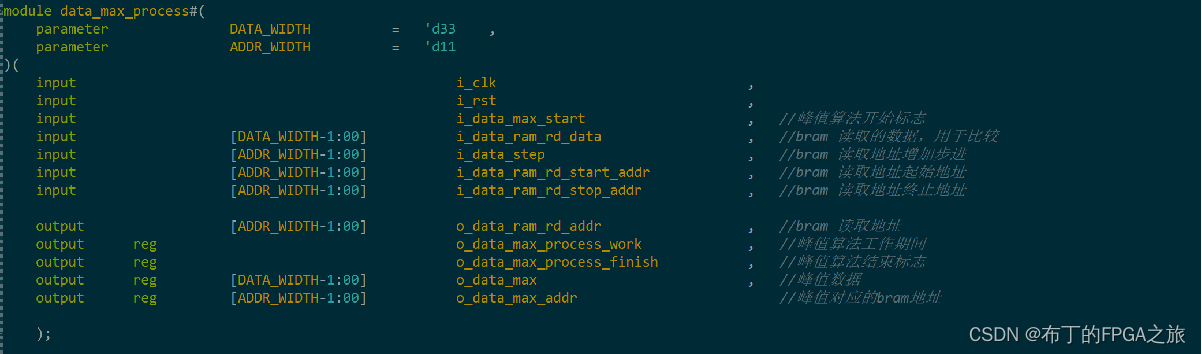

8、数据最大值处理的参数及端口——data_max_process

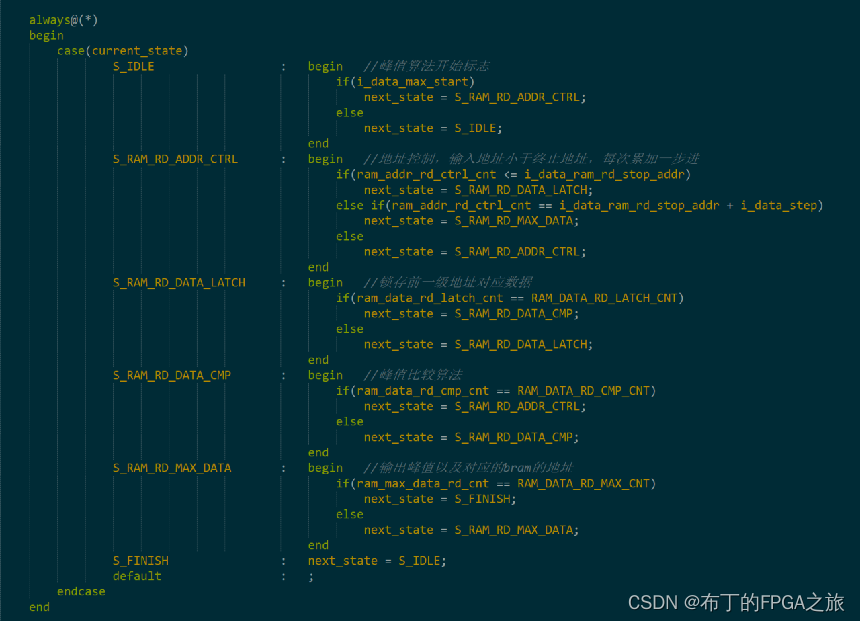

9、算法状态机(第二段)

①S_IDLE:峰值算法开始标志

②S_RAM_RD_ADDR_CTRL:地址控制,输入地址小于终止地址,每次累加一步进

③S_RAM_RD_DATA_LATCH:锁存前一级地址对应数据

④S_RAM_RD_DATA_CMP:峰值比较算法

⑤S_RAM_RD_MAX_DATA:输出峰值以及对应的bram的地址

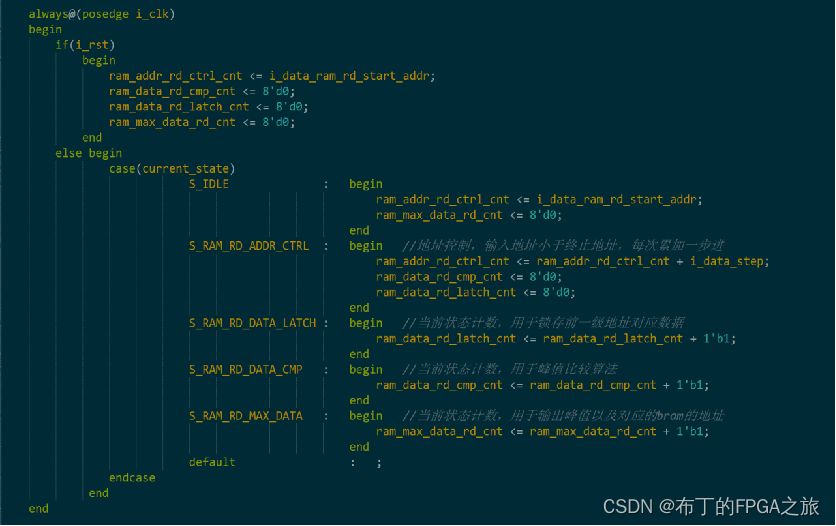

10、算法状态机(第三段计数)

①S_RAM_RD_ADDR_CTRL:地址控制,输入地址小于终止地址,每次累加一步进

②S_RAM_RD_DATA_LATCH:当前状态计数,用于锁存前一级地址对应数据

③S_RAM_RD_DATA_CMP:当前状态计数,用于峰值比较算法

④S_RAM_RD_MAX_DATA:当前状态计数,用于输出峰值以及对应的bram的地址

11、算法状态机(第三段比较)

①S_RAM_RD_DATA_LATCH:锁存前一级地址对应数据③S_RAM_RD_DATA_CMP:峰值比较算法,不断跟前一次数值比较,将大的数值赋给data_middle

④S_RAM_RD_MAX_DATA:输出峰值以及对应的bram的地址