文章目录

- 1、简介

- 2、框图

- 3、寄存器

- 4、地址

1、简介

C6678中共有16个GPIO,GPIO0~GPIO15。这些引脚的功能如下

- 通用输入输出管脚

- 中断&EDMA事件管脚

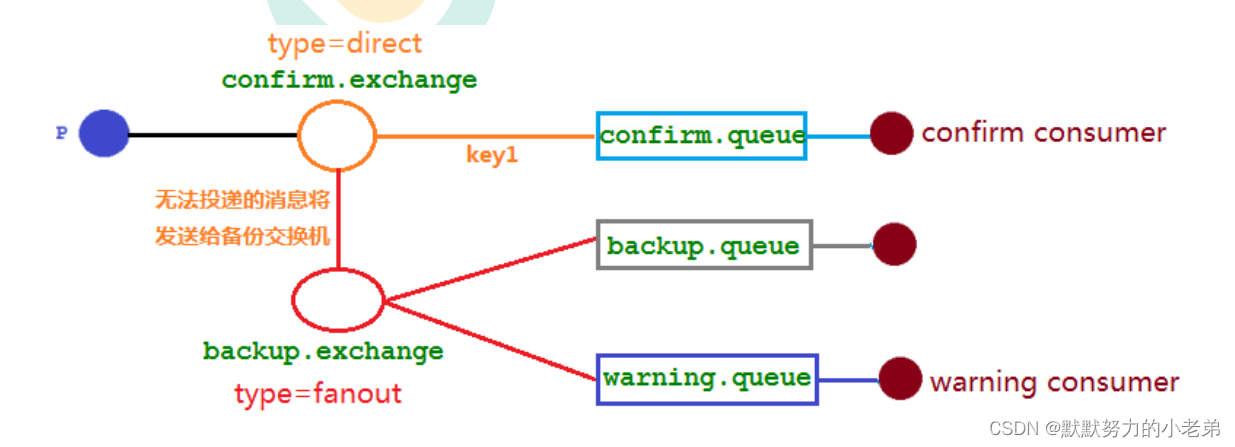

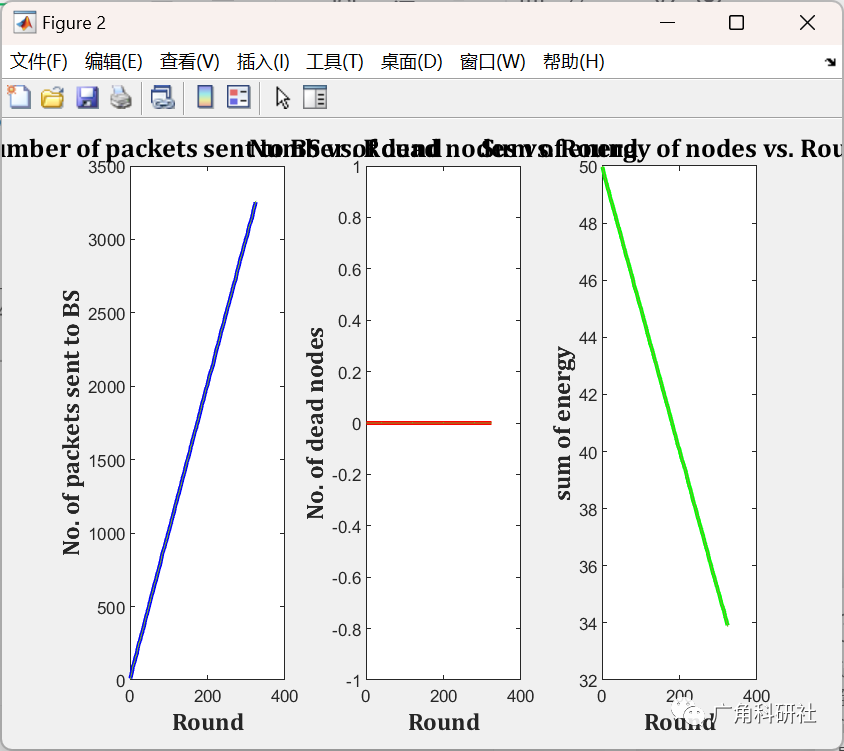

2、框图

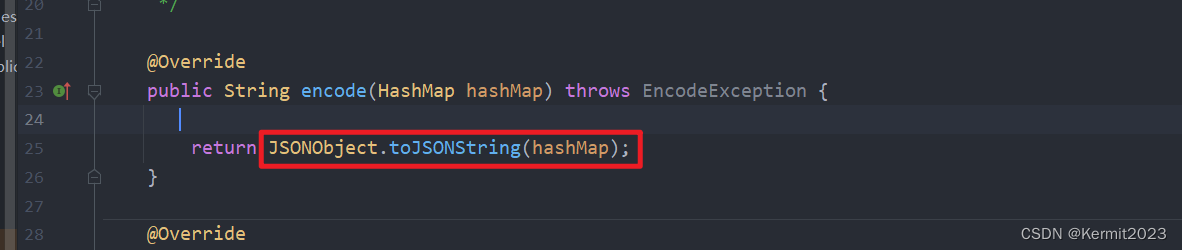

1、GPIO作为通用输入输出时,用到的寄存器为DIR、SET_DATA、OUT_DATA、CLR_DATA、IN_DATA

2、GPIO管脚配置为中断&EDMA事件模式时,用到的寄存器为SET_RIS_TRIG、RIS_TRIG、CLR_RIS_TRIG、SET_FAL_TRIG、FAL_TRIG、CLR_FAL_TRIG。另外可以看出,在中断或EDMA模式的时候,可以忽略管脚的输入输出配置

3、外设时钟为CPU/6

3、寄存器

Direction Register (DIR)

控制GPIO管脚是输入还是输出,其中,对应bit置0表示该管脚配置为输出管脚;对应bit置1表示该管脚配置为输入管脚

Set Data Register (SET_DATA)

给SET_DATA寄存器对应位置1,将使该管脚输出高电平。写0则没有影响

Clear Data Register (CLR_DATA)

给CLR_DATA寄存器对应位置1,将使该管脚输出低电平。写0则没有影响

Output Data Register (OUT_DATA)

给OUT_DATA寄存器对应位置1,则输出高,写0则输出低。在配置为输入状态下没有影响。对SET_DATA和CLR_DATA寄存器操作其实都相当于间接操作这个寄存器

Input Data Register (IN_DATA)

在输入模式下,读取该寄存器获取管脚的状态

Set Rising Edge Interrupt Register (SET_RIS_TRIG)

在相应位写1,会在上升沿触发GPIO中断和EDMA事件。 写0则没有影响

Clear Rising Edge Interrupt Register (CLR_RIS_TRIG)

在相应位写1,会清除SET_RIS_TRIG相应的位。 写0则没有影响

Set Falling Edge Interrupt Register (SET_FAL_TRIG)

在相应位写1,会在下降沿触发GPIO中断和EDMA事件。 写0则没有影响

Clear Falling Edge Interrupt Register (SET_FAL_TRIG)

在相应位写1,会清除SET_FAL_TRIG相应的位。 写0则没有影响

Interrupt Per-Bank Enable Register (BINTEN)

只有该寄存器最低位置1时GPIO管脚才可以作为中断源。写0则禁用中断。

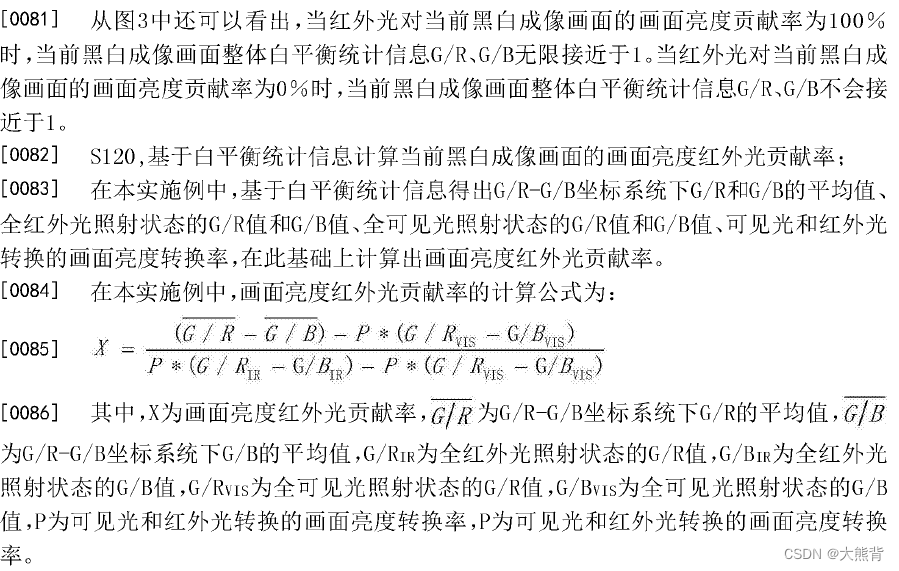

GPIO的中断触发方式可以是上升沿、下降沿或者上升沿下降沿都触发

4、地址

BINTEN_REG 0x02320008

DIR 0x02320010

OUT_DATA 0x02320014

SET_DATA 0x02320018

CLR_DATA 0x0232001C

IN_DATA 0x02320020

SET_RIS_TRIG 0x02320024

CLR_RIS_TRIG 0x02320028

SET_FAL_TRIG 0x0232002C

CLR_FAL_TRIG 0x02320030

/*在调试的过程中可以查看寄存器的地址来确定管脚的状态。比如输入模式下,可以通过查看地址0x02320020的值来看管脚是否接收正确*/

![[Git] Git零基础?带你快速入门,示例练习上手](https://img-blog.csdnimg.cn/846ce01a535542518c724237577f2968.gif#pic_center)