学习目标:

- 理解动态随机存取存储器的基本原理和工作机制。

- 掌握动态随机存取存储器的读写操作及时序。

- 理解动态随机存取存储器的存储单元结构和电路设计。

- 熟悉动态随机存取存储器的刷新技术及其影响因素。

- 理解动态随机存取存储器与静态随机存取存储器的异同。

- 掌握动态随机存取存储器的容量扩展技术和多模式存储器的设计思想。

- 了解动态随机存取存储器的应用场景及其发展趋势。

学习步骤:

学习动态随机存取存储器(DRAM)时,我会遵循以下步骤:

-

学习DRAM的基本原理:了解DRAM存储器单元的组成,以及如何读取和写入数据。

-

理解DRAM的读/写时序:学习DRAM的读/写时序,了解时钟信号如何控制DRAM操作,并学习如何选择合适的时序参数以满足系统要求。

-

掌握DRAM芯片的布局:了解DRAM芯片的物理布局,包括存储阵列、行地址译码器、列地址译码器、I/O线路和控制逻辑。

-

学习DRAM控制电路的设计:学习如何设计DRAM控制电路,包括行地址译码器、列地址译码器和预充电电路等。

-

了解DRAM刷新技术:学习DRAM的刷新原理和操作,包括自刷新和外部刷新,以确保数据的稳定性和一致性。

-

掌握DRAM的性能参数:了解DRAM的性能参数,如访问时间、带宽、刷新周期等,以及它们之间的相互关系,以满足系统性能需求。

-

学习DRAM的容量扩展技术:了解DRAM的容量扩展技术,包括多芯片选择器(MCS)、双数据率(DDR)和动态RAM(DRAM)的堆叠等。

-

掌握DRAM的故障排除技巧:学习如何排除DRAM的故障,包括使用测试工具和技术手段来诊断和解决问题。

总的来说,学习DRAM需要掌握其基本原理、读/写时序、芯片布局、控制电路设计、刷新技术、性能参数、容量扩展技术以及故障排除技巧等方面的知识。需要通过理论学习、实验操作、参考资料等多种方式进行综合学习,才能深入理解和掌握DRAM的工作原理和应用。

3.3.1 DRAM存储元的工作原理

我的理解:

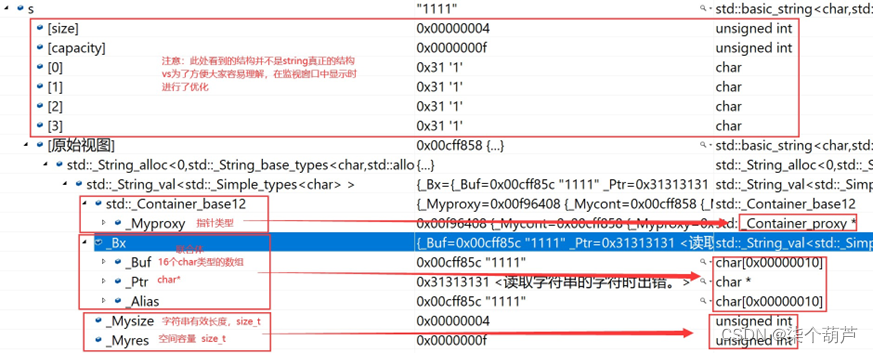

DRAM(Dynamic Random Access Memory)存储元是计算机中常用的一种存储器类型。其存储单元由一个电容和一个开关晶体管组成,电容中存储着一个电荷,该电荷代表着存储的数据,当需要访问该存储单元时,电荷会被读取或写入。

DRAM存储元的工作原理可以分为三个步骤:

- 写入数据

当需要写入数据时,DRAM存储单元的地址线会将地址信号发送到存储芯片中,控制线将写入命令发送到内存芯片,该命令会使晶体管变为导通状态,将数据写入电容中。在写入数据之前,需要将电容中的电荷清空。

- 读取数据

当需要读取数据时,DRAM存储单元的地址线会将地址信号发送到存储芯片中,控制线将读取命令发送到内存芯片,该命令会使晶体管变为导通状态,读取电容中的电荷。读取完数据后,需要将电容中的电荷清空,以便存储下一次数据。

- 刷新数据

由于电容的电荷会逐渐漏电,导致存储的数据出现错误,因此需要定期刷新电容中的电荷,以维持数据的准确性。DRAM存储器会周期性地发出刷新信号,将所有存储单元中的电荷读出并再次写入,以保证数据的正确性。

以上就是DRAM存储元的工作原理。由于DRAM存储器具有容量大、价格低廉等优点,因此被广泛应用于计算机系统中的主存储器。

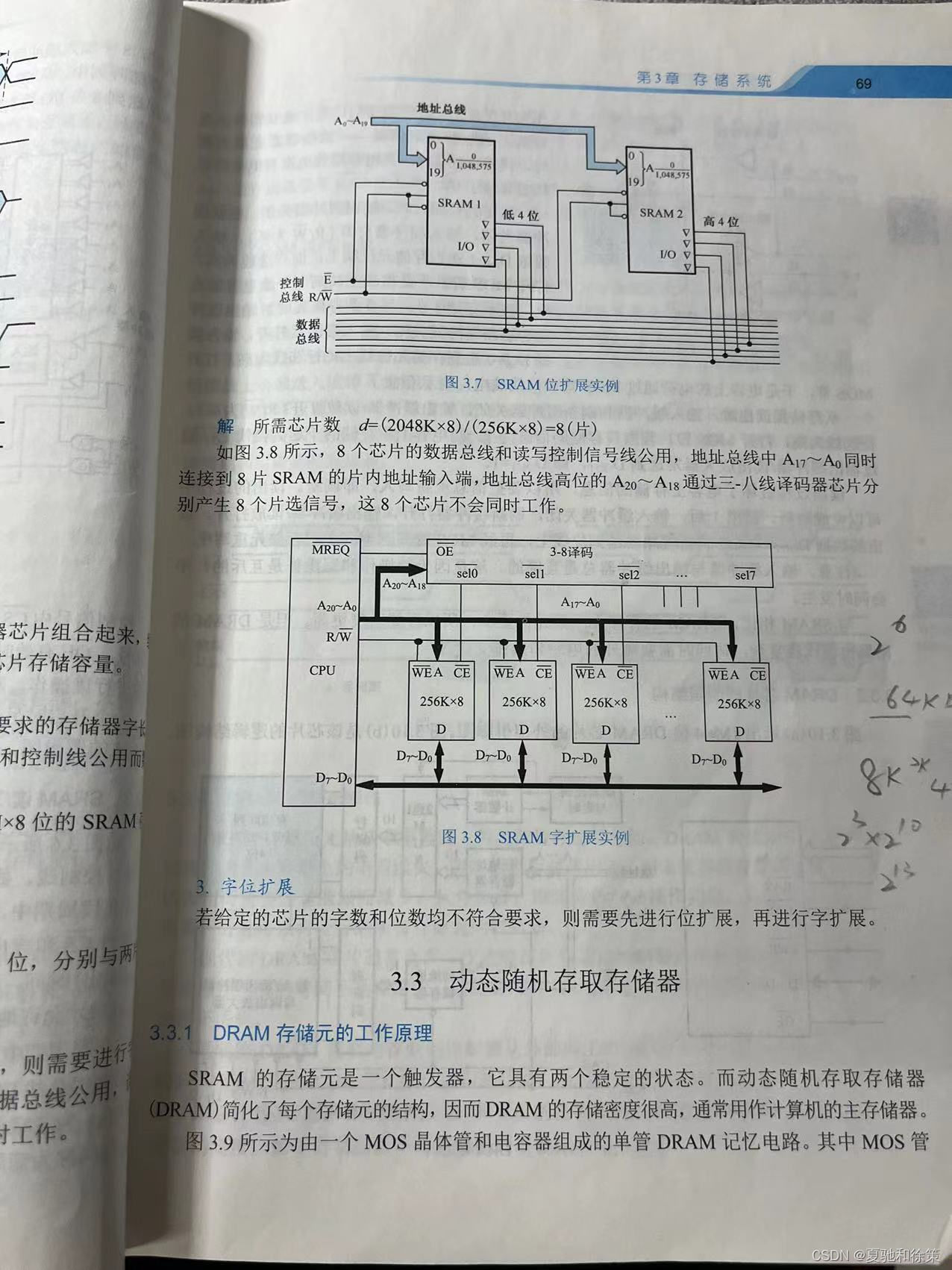

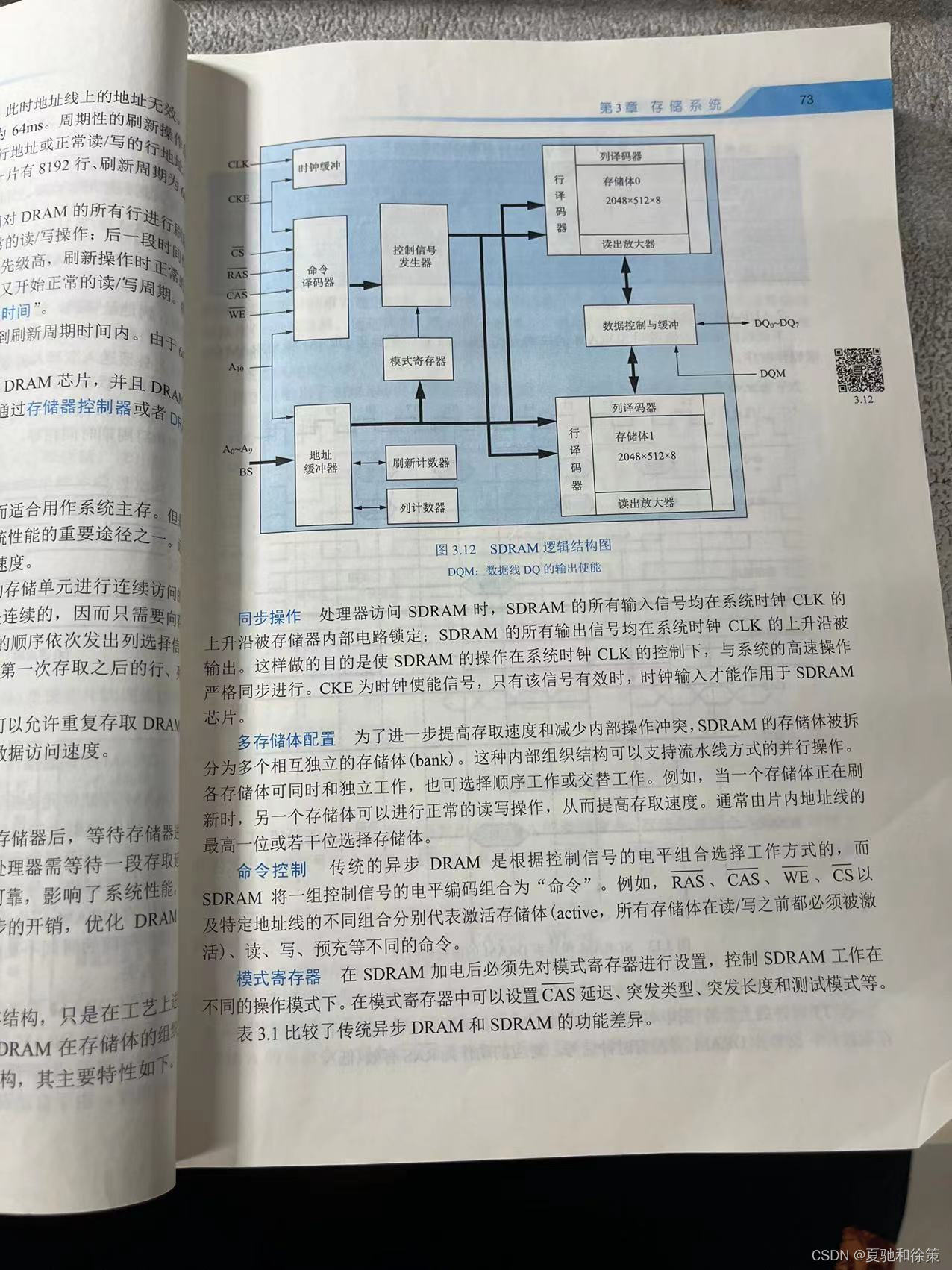

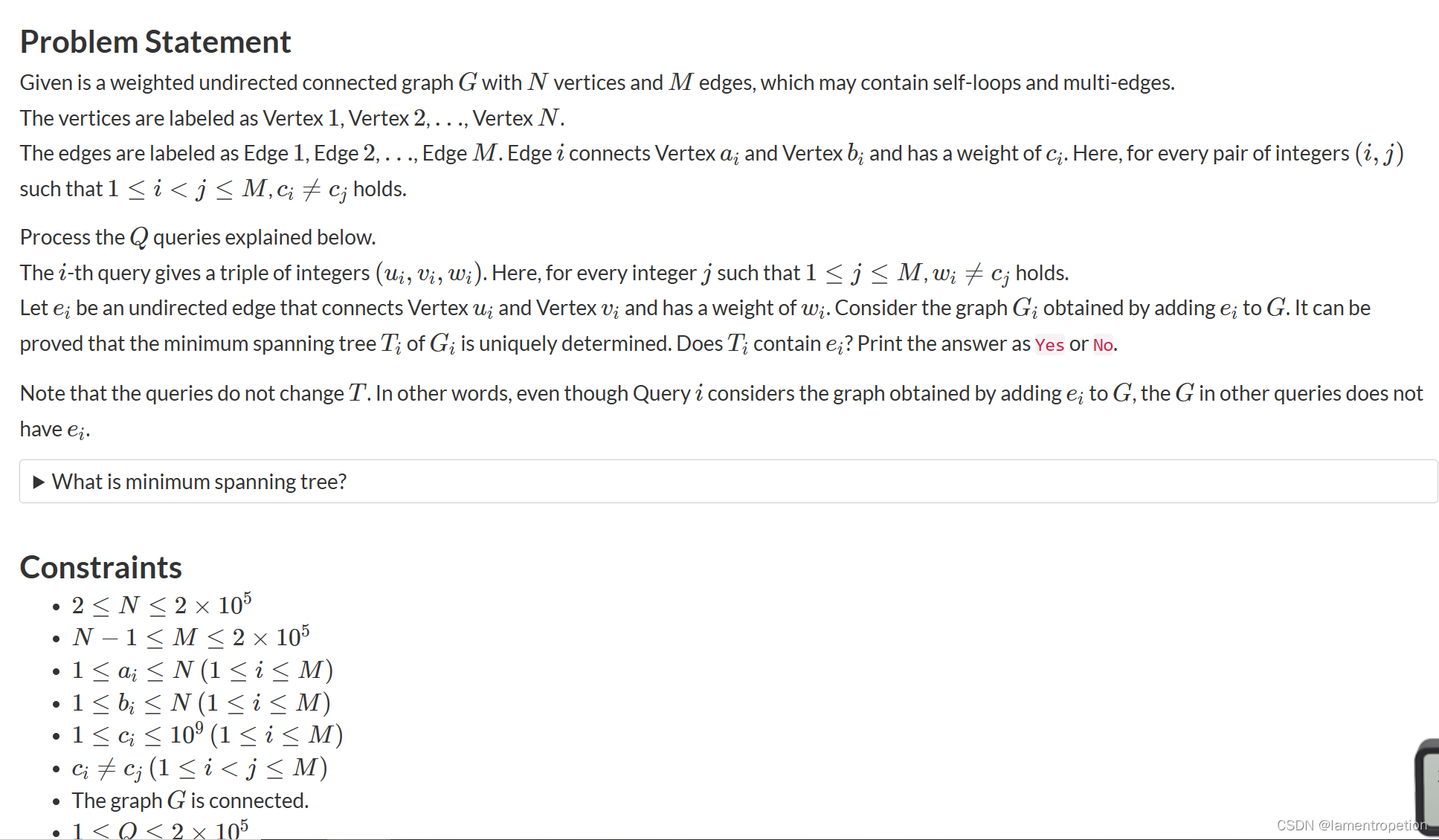

3.3.2 DRAM芯片的逻辑结构

DRAM芯片的逻辑结构包括了DRAM芯片中存储单元的排列方式、控制信号的输入输出方式等。

DRAM芯片的存储单元是由一些存储电容和访问晶体管组成的。在一个DRAM芯片中,存储单元通常被排列成一个二维数组的形式,每一行被称为一个“行”,每一列被称为一个“列”。每个存储单元可以通过行地址和列地址来访问,也就是通过行列地址可以唯一地确定一个存储单元。

在访问一个DRAM芯片中的存储单元时,需要先通过行地址选择一个行,然后再通过列地址选择一个列,最后才能读取或写入数据。DRAM芯片内部会通过行地址解码器和列地址解码器来选择相应的行和列,然后将数据读取或写入到这个存储单元。

DRAM芯片还需要一些控制信号来控制读写操作。例如,读写控制信号用于控制读取或写入操作,时序控制信号用于确定读写操作的时序。在DRAM芯片内部,这些控制信号会被解码并转换为相应的操作信号,以控制存储单元的读写操作。

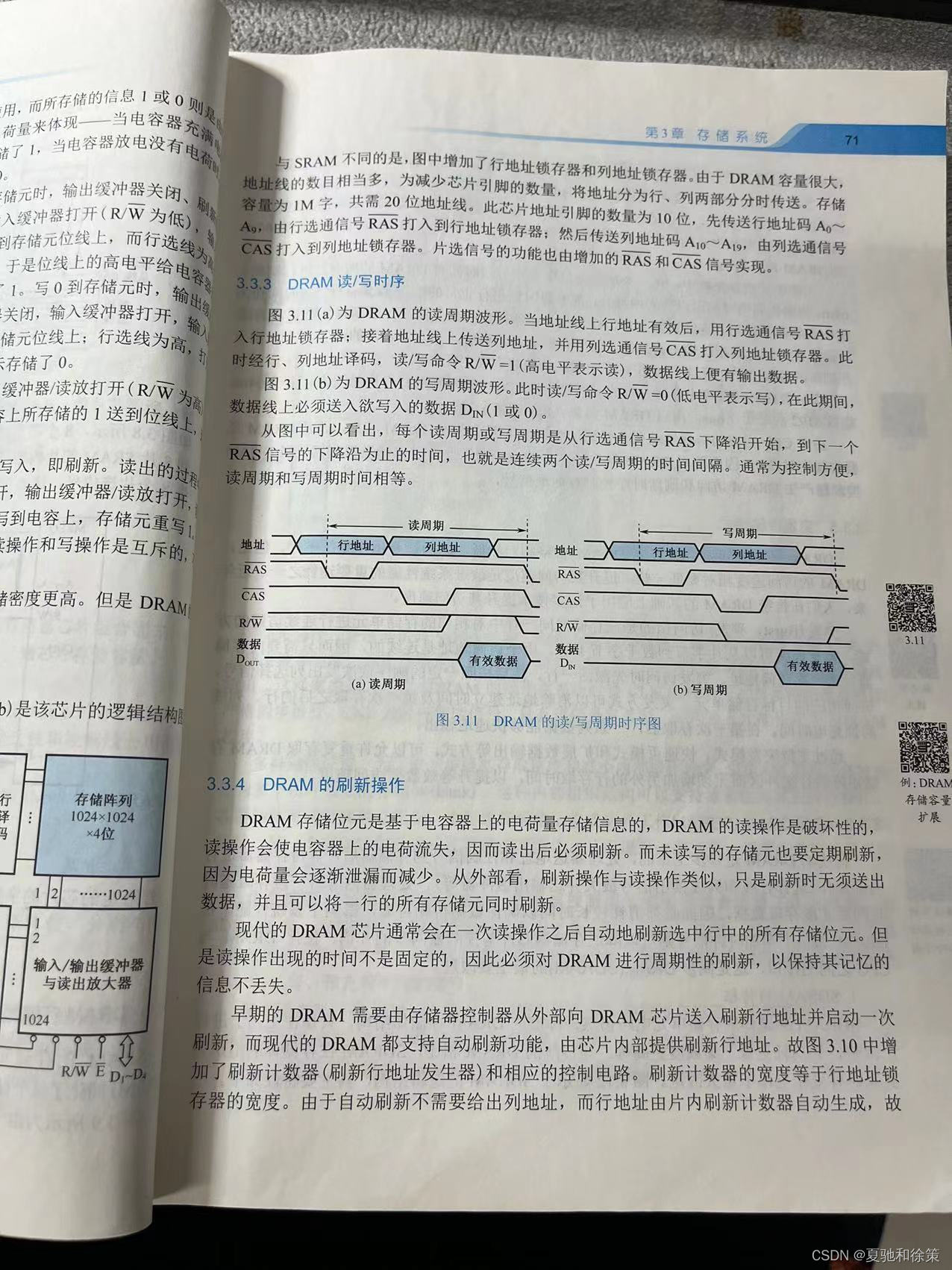

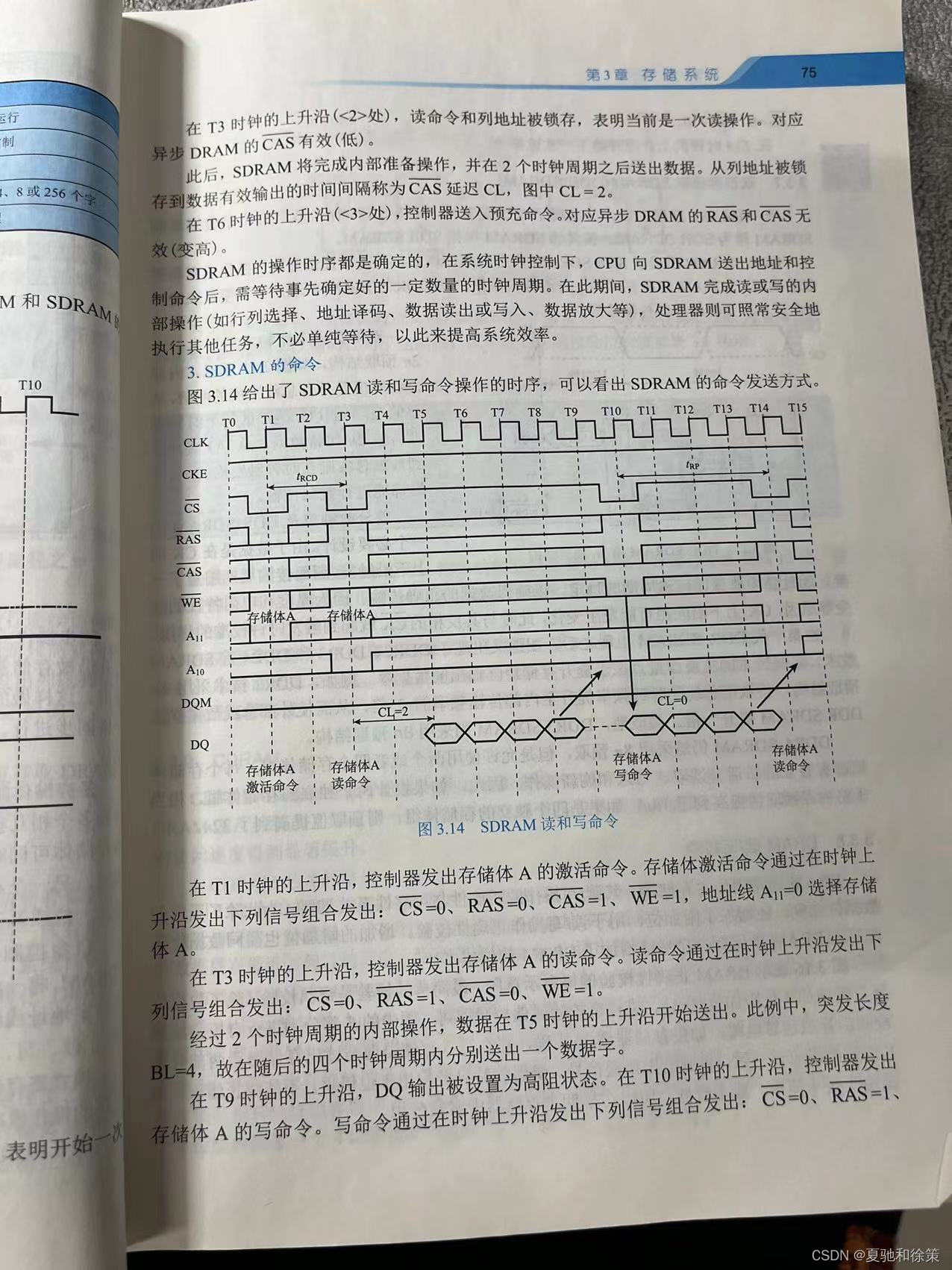

3.3.3 DRAM读/写时序

DRAM的读/写时序是指控制DRAM存储元进行读写操作时的时序规定。通常包括时钟脉冲的产生、地址信号的输入、数据的读写等过程。

在进行DRAM读操作时,首先需要给出一个读指令和相应的行地址和列地址。DRAM将指定行的所有存储元中的数据读出并预先放置到内部的读缓冲区。然后,在下一次时钟上升沿时,DRAM将数据从读缓冲区中输出并传输给CPU或其他外部设备。整个读操作需要一定的时序,包括行地址的输入时间、预充电时间、数据输出时间等。

在进行DRAM写操作时,首先需要给出一个写指令和相应的行地址和列地址。DRAM将指定行的所有存储元的内部存储单元置位待写,并将数据存储到写缓冲区中。在下一次时钟上升沿时,DRAM将写缓冲区中的数据写入到指定行的所有存储元中。整个写操作同样需要一定的时序,包括行地址的输入时间、预充电时间、数据输入时间等。

为了保证DRAM读/写时序的正确性,需要根据具体的DRAM芯片和外部控制器的规格书进行时序设计。常见的时序参数包括行选通延迟(tRAS)、行预充电时间(tRP)、列选通延迟(tCAS)、列写入延迟(tCWL)等。在实际的系统设计中,需要根据时序参数和时钟频率等因素综合考虑来确定DRAM的读/写时序。

3.3.4 DRAM的刷新操作

DRAM(Dynamic Random Access Memory)是一种动态随机存取存储器,其存储单元为存储电容器,需要定期刷新以防止电荷漏失。刷新规则是指在何时、何地、如何刷新DRAM存储器中的内容。

具体来说,DRAM存储器需要定期刷新其存储单元中的电荷,以保持数据的可靠性。刷新规则包括两种类型:基于时间的刷新和基于请求的刷新。

基于时间的刷新:DRAM存储器需要周期性地对存储单元进行刷新操作。这个周期称为刷新周期(Refresh Cycle),也就是DRAM存储器要多长时间才会对其中的数据进行一次刷新。在刷新周期中,DRAM存储器会按照预先设定的刷新顺序,依次对每个存储单元进行刷新操作。刷新周期的长度取决于DRAM存储器的工作频率和内部结构,通常为64ms至16ms之间。

基于请求的刷新:也称自适应刷新(Auto-Refresh),DRAM存储器在空闲时会检查存储单元的状态,如果有需要刷新的单元,则会进行刷新操作。基于请求的刷新方式能够减少刷新操作对系统性能的影响,但需要额外的控制电路来实现。

总体来说,刷新规则是DRAM存储器必须遵循的重要规定,对保证数据的可靠性具有重要作用。

3.3.5 突发传输模式

突发传输模式(Burst Mode)是指在一次访问中连续地从DRAM存储单元中读取或写入多个数据。与传统的单个数据读/写相比,突发传输模式可以有效提高数据传输速率和系统性能,减少因频繁读/写单个数据而引起的延迟和功耗开销。

在突发传输模式下,DRAM芯片会自动连续输出或接收多个数据,因此不需要每个数据都进行读/写时序控制。突发传输模式的长度可以根据具体的实现进行设置,通常为4、8或16个数据。

在DRAM突发传输模式中,首先需要发送一个预充电命令(Precharge),将所有行预充电,为后续的读/写操作做好准备。然后,通过发送一个列地址和一个列地址有效命令(CAS)来选择一个列,并将该列中的多个数据连续输出或写入。最后,发送另一个预充电命令以清除该行,并进行下一次读/写操作。

需要注意的是,在突发传输模式下,DRAM芯片内部的自动刷新操作可能会干扰传输,因此需要特殊处理来保证稳定性。

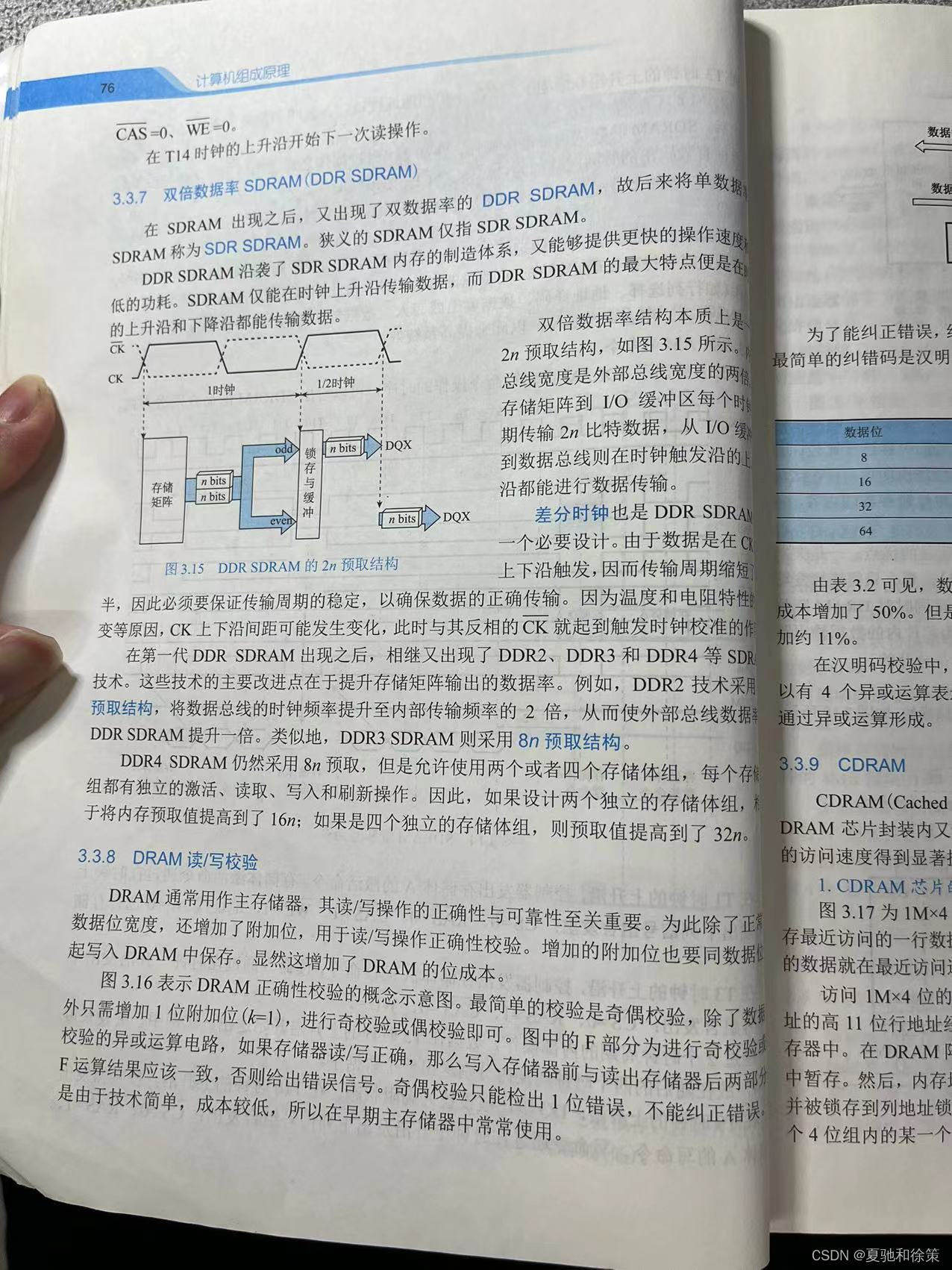

3.3.6 同步DRAM

SDRAM(Synchronous Dynamic Random Access Memory,同步动态随机存取存储器)是一种内存芯片,它使用同步时钟信号来提高数据传输速率和效率。

与传统的DRAM不同,SDRAM在内部使用了一组复杂的控制和同步逻辑,以支持高速的读/写访问。这些逻辑包括一个内部时钟发生器,它用于在读/写访问期间生成时序信号;还有一个地址和命令管线,它用于加速命令和地址的传输。

SDRAM还使用了突发传输模式(burst mode),这意味着它可以在一次读/写命令中传输多个数据项,从而减少命令和地址信号的传输次数,提高传输效率。突发传输模式还可以减少对SDRAM总线的竞争,从而提高总线效率。

SDRAM也有不同类型的规格,例如DDR、DDR2、DDR3和DDR4等,它们具有不同的传输速率和时序要求,可以根据实际应用需求选择。

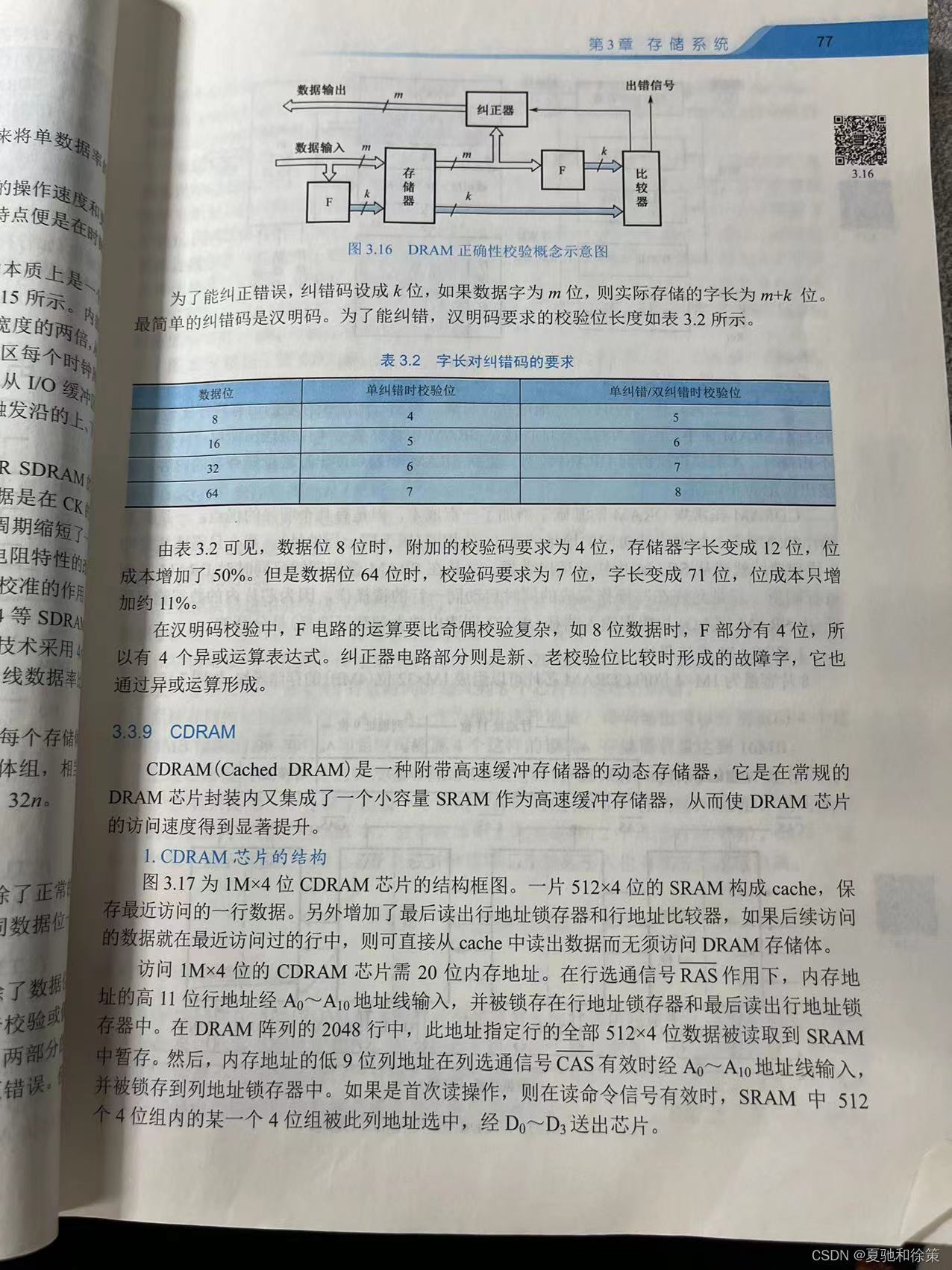

3.3.8 DRAM读/写校验

DRAM读写校验是一种用于检测DRAM读写操作是否正确的技术。由于DRAM存储单元的可靠性较低,可能会出现硬件错误,比如位翻转,而这些错误可能会导致程序崩溃或数据损坏。为了检测这些错误,DRAM读写校验技术会在DRAM读写操作完成后,对读取或写入的数据进行校验和计算,并将校验和与原始数据一起存储在另外的存储单元中。当需要使用这些数据时,系统会重新计算校验和,并将其与之前存储的校验和进行比较。如果校验和不匹配,就说明数据已经被修改或者存在硬件错误,需要进行相应的处理,比如重新读取或者报错提示。

常用的DRAM读写校验技术包括ECC(错误检测与纠正)和Parity(奇偶校验)等。ECC技术能够检测和纠正单个或多个比特的错误,它需要在存储器中额外存储一些纠错码(校验码),来检测和纠正存储单元中的错误。Parity技术则是通过将一个奇偶校验位添加到每个字节或字中,来检测和纠正单个比特错误。ECC技术通常比Parity技术更可靠,但是它也需要更多的存储空间和计算开销。

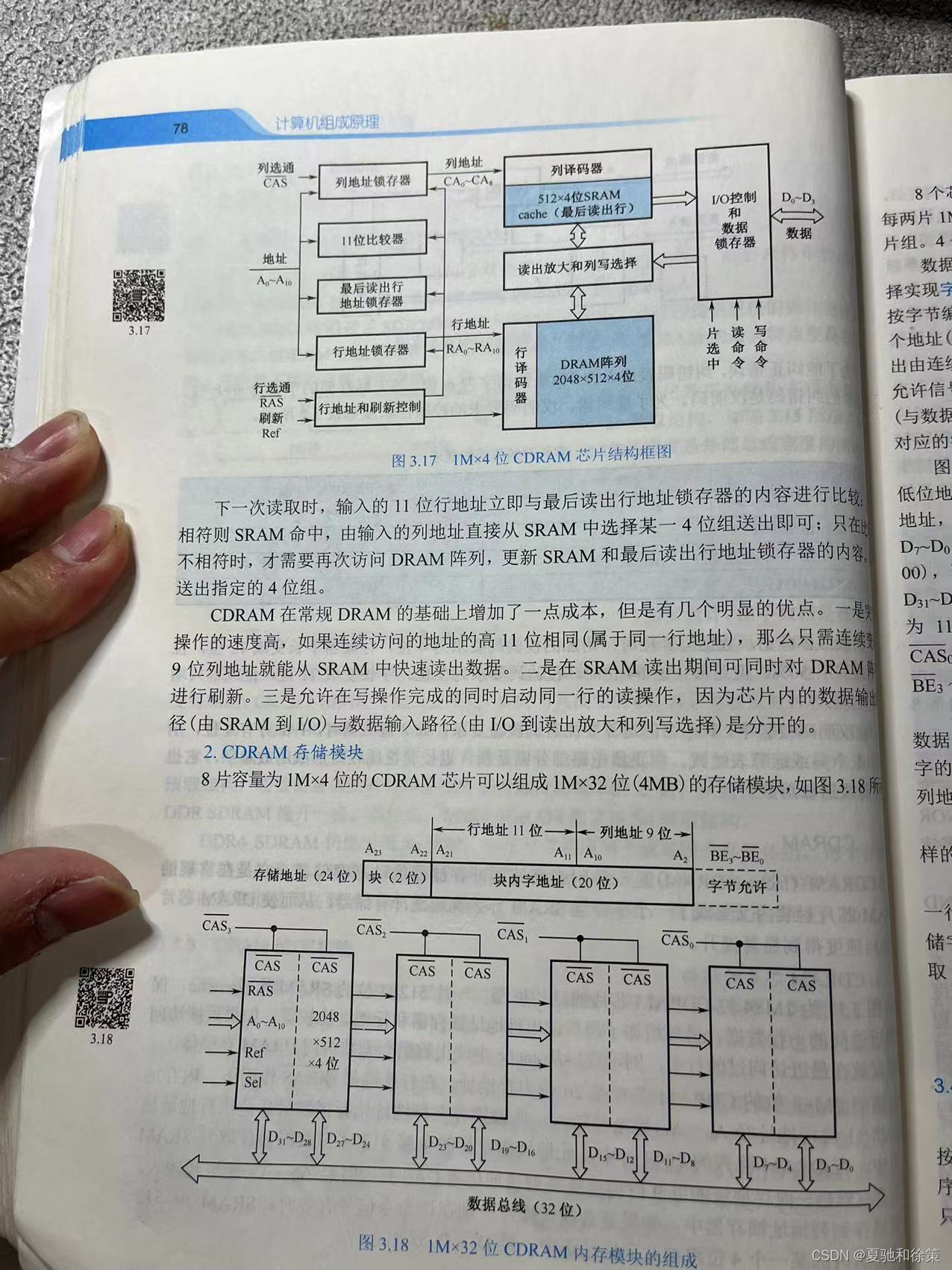

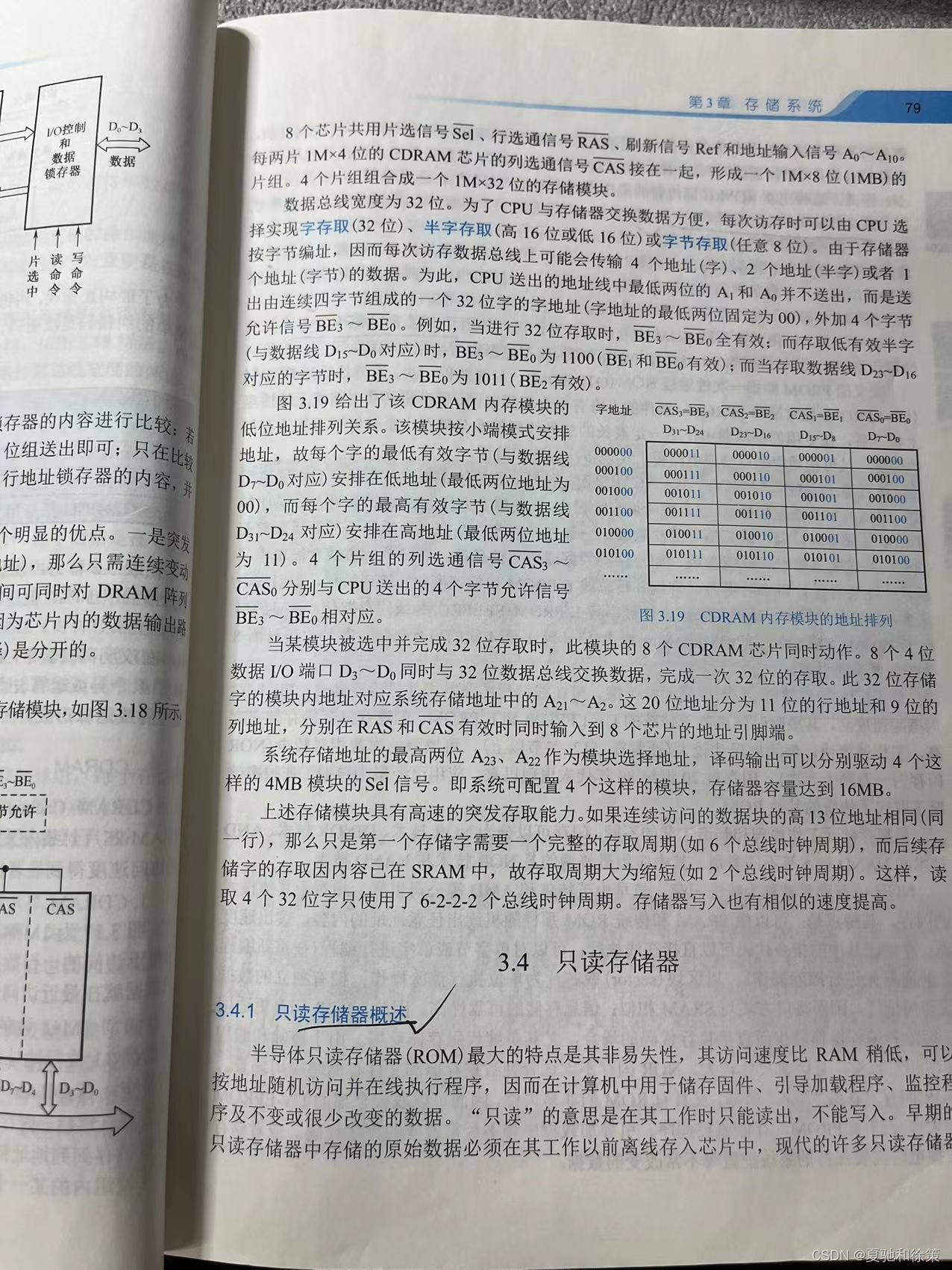

3.3.9 CDRAM

CDRAM是一种基于DRAM技术的存储器,其名称是“Cache DRAM”的缩写,它被设计用于高速缓存存储器中。与传统的DRAM不同,CDRAM使用了一种特殊的高速缓存控制逻辑,可以将常用的数据缓存到高速缓存中,以提高系统性能。以下是CDRAM的一些特点:

-

高速缓存:CDRAM具有内部高速缓存,可以存储常用数据,以加速读取速度。

-

数据预取:CDRAM可以在读取数据时同时预取下一个数据,以进一步加快访问速度。

-

高速数据传输:CDRAM支持高速数据传输,使得数据能够更快地传输到处理器。

-

缓存失效:当内部高速缓存无法命中时,CDRAM将自动读取主存中的数据并将其缓存到高速缓存中,以加快后续访问速度。

-

双倍速刷新:CDRAM支持双倍速刷新,可以加快DRAM的刷新速度,减少系统的延迟。

总的来说,CDRAM是一种高性能存储器,主要用于高速缓存存储器中。它具有高速缓存、数据预取、高速数据传输等特点,能够显著提高系统性能。

总结:

动态随机存储器(DRAM)是计算机中最常用的内存类型之一,其工作原理和结构与静态随机存储器(SRAM)有所不同。以下是DRAM学习中的重点和难点和易错点的总结:

重点:

- DRAM存储元的工作原理和逻辑结构。

- DRAM的读/写时序和刷新规则。

- 突发传输模式和如何提高DRAM的数据传输效率。

- SDRAM和DDR SDRAM的特点和区别。

难点:

- DRAM存储元的内部电荷如何被读取和写入。

- DRAM的刷新规则和如何在刷新时保持数据的可靠性。

- DRAM的读写时序的复杂性和如何进行时序分析和优化。

- 如何解决DRAM的存储密度和功耗之间的矛盾。

易错点:

- 配置DRAM时序参数时的错误。

- 配置DRAM时传输模式和频率的错误。

- DRAM刷新规则和刷新周期的错误配置。

- DRAM的数据传输错误和数据完整性问题。

了解和掌握以上重点和难点以及避免易错点,将有助于更好地理解和应用DRAM技术。

![[oeasy]python0145_版本控制_git_备份还原](https://img-blog.csdnimg.cn/img_convert/af1665be24a9537f9a9bec1c4b2da1d8.png)

![[计算机图形学]相机与透镜(前瞻预习/复习回顾)](https://img-blog.csdnimg.cn/55ce0064aa1b4ac2ac9166dca4d818c1.png)