1、Cortex M3 内核 & 芯片

ARM公司提供内核(如Cortex M3,简称CM3,下同)授权,完整的MCU还需要很多其他 组件。芯片公司(ST、NXP、TI、GD、华大等)在得到CM3内核授权后,就可以把CM3内核用 在自己的硅片设计中,添加:存储器,外设,I/O以及其它功能块。不同厂家设计出的单片机会 有不同的配置,包括存储器容量、类型、外设等都各具特色,因此才会有市面上各种不同应用 的ARM芯片。Cortex M3内核和芯片的关系如图5.3.1.1所示:

可以看到,ARM公司提供CM3内核和调试系统,其他的东西(外设(IIC、SPI、UART、TIM等)、存储器(SRAM、FLASH等)、I/O等)由芯片制造商设计开发。这里ST公司就是STM32F103芯片的制造商。

2、STM32F103ZET6 内部系统结构

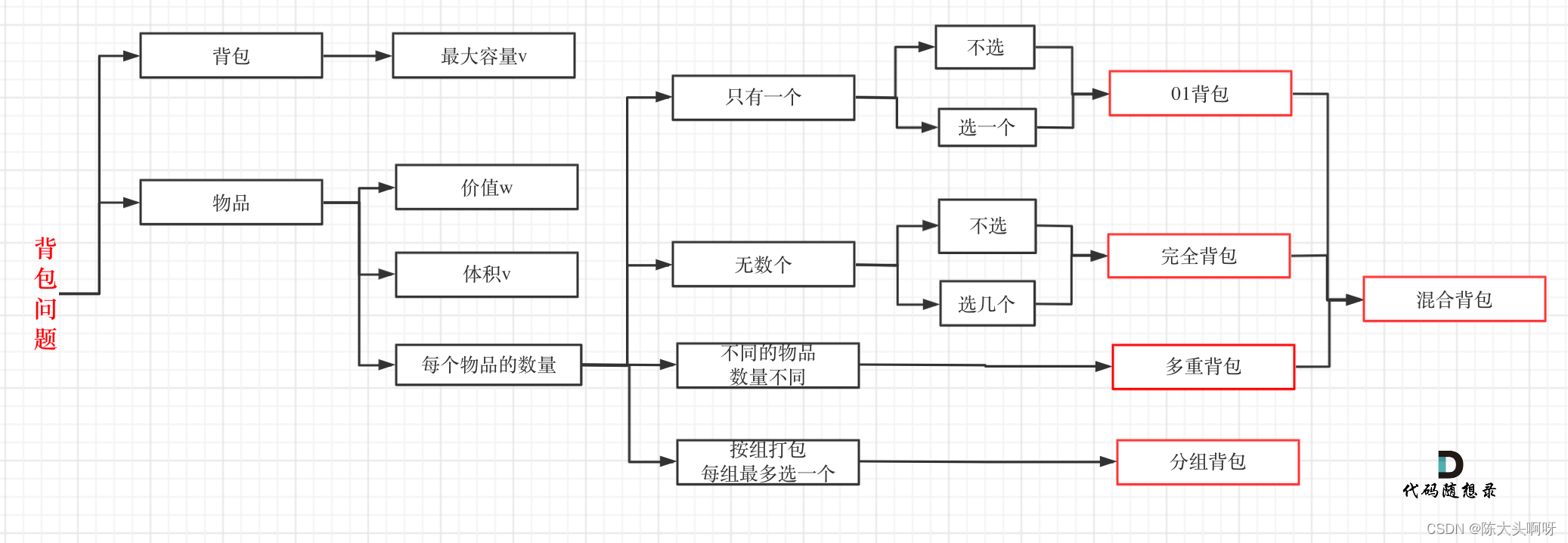

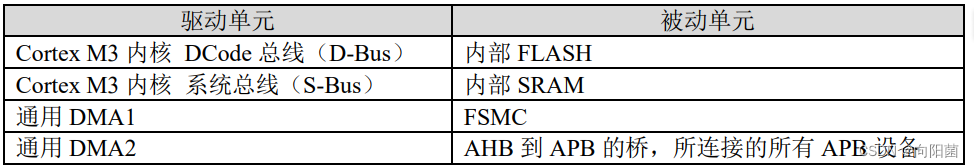

STM32F103的系统主要由:四个驱动单元(可以主动发起通信,图中①区域)和四个被动 单元(只能被驱动工作,图中②区域)组成,如表5.3.2.1所示:

这里的驱动/被动单元都是指连接了总线矩阵的部分,未连接总线矩阵的部分,则不算作驱 动/被驱动单元。接下来我们介绍一下这些单元。

1. I Code 总线(I - Bus)

这是Cortex M3内核的指令总线,连接闪存指令接口(如:FLASH),用于获取指令。由于 该总线功能单一,并没有直接连接到总线矩阵,因此被排除在驱动单元之外。

2. D Code 总线(D - Bus)

这是Cortex M3内核的数据总线,连接闪存存储器数据接口(如:SRAM、FLASH等),用 于各种数据访问,如常量、变量等。

3. 系统总线(S - Bus)

这是Cortex M3内核的系统总线,连接所有外设(如:GPIO、SPI、IIC、TIM等),用于控 制各种外设工作,如配置各种外设相关寄存器等。

4. DMA 总线

DMA是直接存储访问控制器,可以实现数据的自动搬运,整个过程不需要CPU处理。如可 以实现DMA传输内存数据到DAC,输出任意波形,传输过程不需要CPU参与,可以大大节省CPU

支,从而更高效的处理事务。STM32F103ZET6内部有2个DMA控制器,可以实现内存到外设、 外设到内存、内存到内存的数据传输。

5. 内部 FLASH

内部FLASH即单片机的硬盘,用于代码/数据存储,CPU通过ICode总线经FLASH接口访问 内部FLASH,FLASH最高访问速度是24Mhz,因此以72M速度访问时,需要插入2个时钟周期延 迟。

6. 内部 SRAM

内部SRAM即单片机的内存,用于数据存储,直接挂载在总线矩阵上面,CPU通过DCode总 线实现0等待延时访问SRAM,最快总线频率可达72Mhz,从而保证高效高速的访问内存。

7. FSMC

FSMC即灵活的静态存储控制器,实际上就是一个外部总线接口,可以用来访问外部SRAM、

NAND/NOR FLASH、LCD等。它也是直接挂在总线矩阵上面的,以方便CPU快速访问外挂器件。

8. AHB/APB 桥

AHB总线连接总线矩阵,同时通过2个APB桥连接APB1和APB2,AHB总线速度最大为

72Mhz,APB2总线速度最大也是72Mhz,但是APB1总线速度最大只能是36Mhz。这三个总线上 面挂载了STM32内部绝大部分外设。

9. 总线矩阵

总线矩阵协调内核系统总线和DMA主控总线之间的访问仲裁,仲裁利用轮换算法,保证各 个总线之间的有序访问,从而确保工作正常。

3、存储器映射

STM32是一个32位单片机,他可以很方便的访问4GB以内的存储空间(2^32 = 4GB),因此

Cortex M3内核将图5.3.2.1中的所有结构,包括:FLASH、SRAM、外设及相关寄存器等全部组 织在同一个4GB的线性地址空间内,我们可以通过C语言来访问这些地址空间,从而操作相关外 设(读/写)。数据字节以小端格式(小端模式)存放在存储器中,数据的高字节保存在内存的高 地址中,而数据的低字节保存在内存的低地址中。

存储器本身是没有地址信息的,我们对存储器分配地址的过程就叫存储器映射。这个分配 一般由芯片厂商做好了,ST将所有的存储器及外设资源都映射在一个4GB的地址空间上(8个 块),从而可以通过访问对应的地址,访问具体的外设。其映射关系如图5.3.3.1所示:

ST将4GB空间分成8个块,每个块512MB,如上图所示,从图中我们可以看出有很多保留区 域(Reserved),这是因为一般的芯片制造厂家是不可能把4GB空间用完的,同时,为了方便后 续型号升级,会将一些空间预留(Reserved)。

4、寄存器映射

给存储器分配地址的过程叫存储器映射,寄存器是一类特殊的存储器,它的每个位都有特 定的功能,可以实现对外设/功能的控制,给寄存器的地址命名的过程就叫寄存器映射。

举个简单的例子,大家家里面的纸张就好比通用存储器,用来记录数据是没问题的,但是 不会有具体的动作,只能做记录,而你家里面的电灯开关,就好比寄存器了,假设你家有8个灯, 就有8个开关(相当于一个8位寄存器),这些开关也可以记录状态,同时还能让电灯点亮/关闭, 是会产生具体动作的。为了方便区分和使用,我们会给每个开关命名,比如厨房开关、大厅开 关、卧室开关等,给开关命名的过程,就是寄存器映射。

当然STM32内部的寄存器有非常多,远远不止8个开关这么简单,但是原理是差不多的,每 个寄存器的每一个位,一般都有特定的作用,涉及到寄存器描述,大家可以参考《STM32F10XXX

参考手册(中文版)_V10.pdf》相关章节的寄存器描述部分,有详细的描述。

A.寄存器描述解读

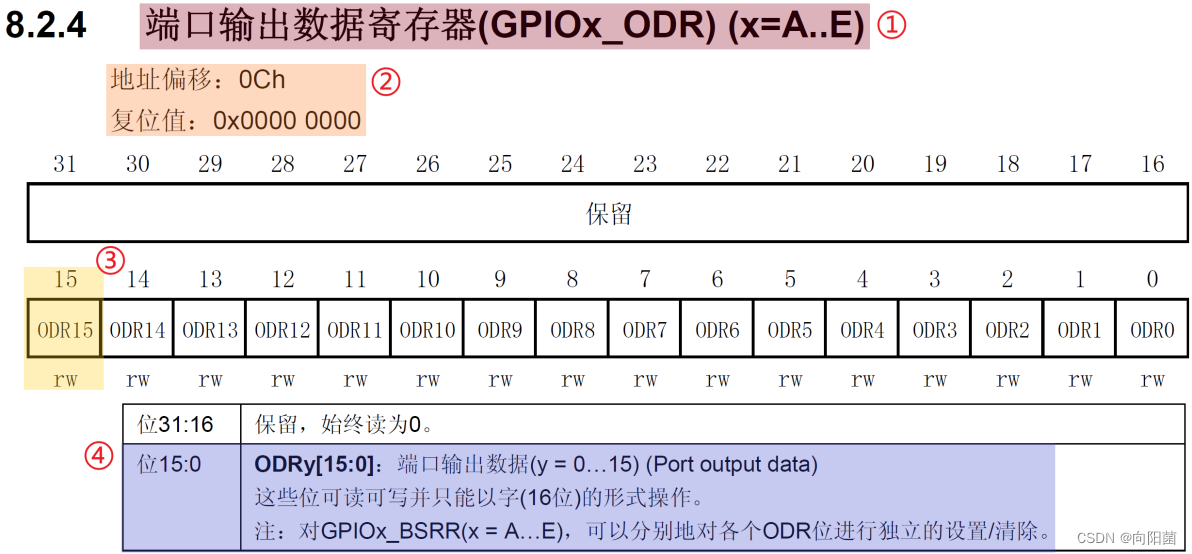

我们以GPIO的ODR寄存器为例,其参考手册的描述如图

① 寄存器名字

每个寄存器都有一个对应的名字,以简单表达其作用,并方便记忆,这里GPIOx_ODR

表示寄存器英文名,x可以从A~E,说明有5个这样的寄存器(每个端口有一个,事实上最 新的STM32F103型号,可能还有F,G等端口,IO数量更多)。

② 寄存器偏移量及复位值

地址偏移量表示相对该外设基地址的偏移,比如GPIOB,我们由图可知其外设基 地址是:0x4001 0C00。那么GPIOB_ODR寄存器的地址就是:0x4001 0C0C。知道了外设基 地址和地址偏移量,我们就可以知道任何一个寄存器的实际地址。

复位值表示该寄存器在系统复位后的默认值,可以用于分析外设的默认状态。这里全 部是0。

③ 寄存器位表

描述寄存器每一个位的作用(共32bit),这里表示ODR寄存器的第15位(bit),位名 字为ODR15,rw表示该寄存器可读写(r,可读取;w,可写入)。

④ 位功能描述

描述寄存器每个位的功能,这里表示位 0~15,对应ODR0~ODR15,每个位控制一个IO

口的输出状态。

其他寄存器描述,参照以上方法解读接口。

B、寄存器映射举例

从前面的学习我们知道 GPIOB_ODR 寄存器的地址为:0x4001 0C0C,假设我们要控制 GPIOB 的 16 个 IO 口都输出 1,则可以写成:

*(unsigned int *)(0x40010C0C) = 0XFFFF; 这里我们先要将 0x4001 0C0C 强制转换成 unsigned int 类型指针,然后用*对这个指针的值 进行设置,从而完成对 GPIOB_ODR 寄存器的写入。

这样写代码功能是没问题,但是可读性和可维护性都很差,使用起来极其不便,因此我们 将代码改为:

#define GPIOB_ODR *(unsigned int *)(0x40010C0C)

GPIOB_ODR = 0XFFFF;这样,我们就定义了一个 GPIOB_ODR 的宏,来替代数值操作,很明显,GPIOB_ODR 的 可读性和可维护性,比直接使用数值操作来的直观和方便。这个宏定义过程就可以称之为寄存 器的映射。

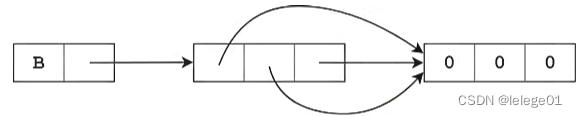

当然,为了简单,我们只举了一个简单实例,实际上大量寄存器的映射,使用结构体是最 方便的方式,stm32f103xe.h 里面使用结构体方式对 STM32F103 的寄存器做了详细映射,等下 我们再介绍。

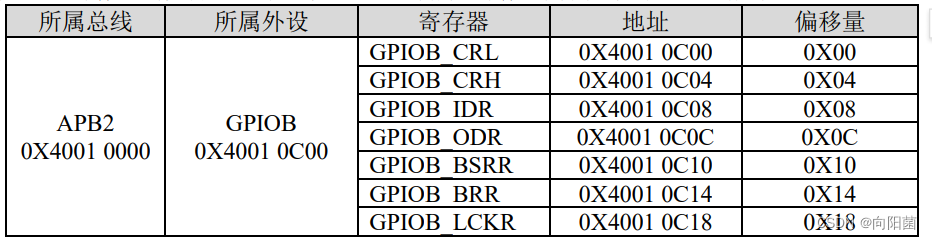

5、寄存器地址计算

STM32F103大部分外设寄存器地址都是在存储块2上面的,见图5.3.3.1。具体某个寄存器地 址,由三个参数决定:1、总线基地址(BUS_BASE_ADDR);2,外设基于总线基地址的偏移 量(PERIPH_OFFSET);3,寄存器相对外设基地址的偏移量(REG_OFFSET)。可以表示为:

寄存器地址 = BUS_BASE_ADDR + PERIPH_OFFSET + REG_OFFSET

总线基地址(BUS_BASE_ADDR),STM32F103内部有三个总线(APB1、APB2和AHB)

举个例子: 上表的偏移量,就是寄存器基于外设基地址的偏移量(REG_OFFSET)。 因此,我们根据前面的公式,很容易可以计算出GPIOB_ODR的地址:

上表的偏移量,就是寄存器基于外设基地址的偏移量(REG_OFFSET)。 因此,我们根据前面的公式,很容易可以计算出GPIOB_ODR的地址:

GPIOB_ODR地址 = APB2总线基地址 + GPIOB外设偏移量 + 寄存器偏移量