请从官网下载 TD4VM 技术参考手册,地址如下:

TDA4VM 技术参考手册地址

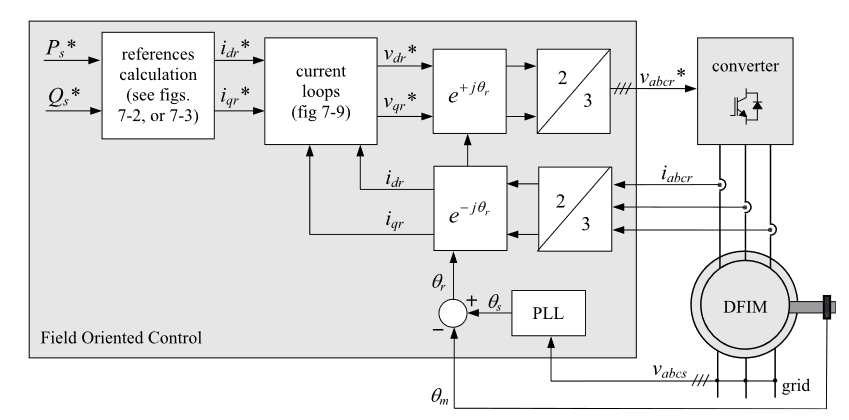

概述

(NAVSS0 的介绍在 TRM 的第10.2章节)

NAVSS0 可以看作 MAIN 域的一个复杂外设域,实现如下功能:

- UDMASS: DMA 管理子系统;

- MODSS:NAVSS0 下集成的一系列外设子系统,比如 Mailbox, Spinlock 等;

- NBSS: North bridge;

- VirtSS: 虚拟化子系统;

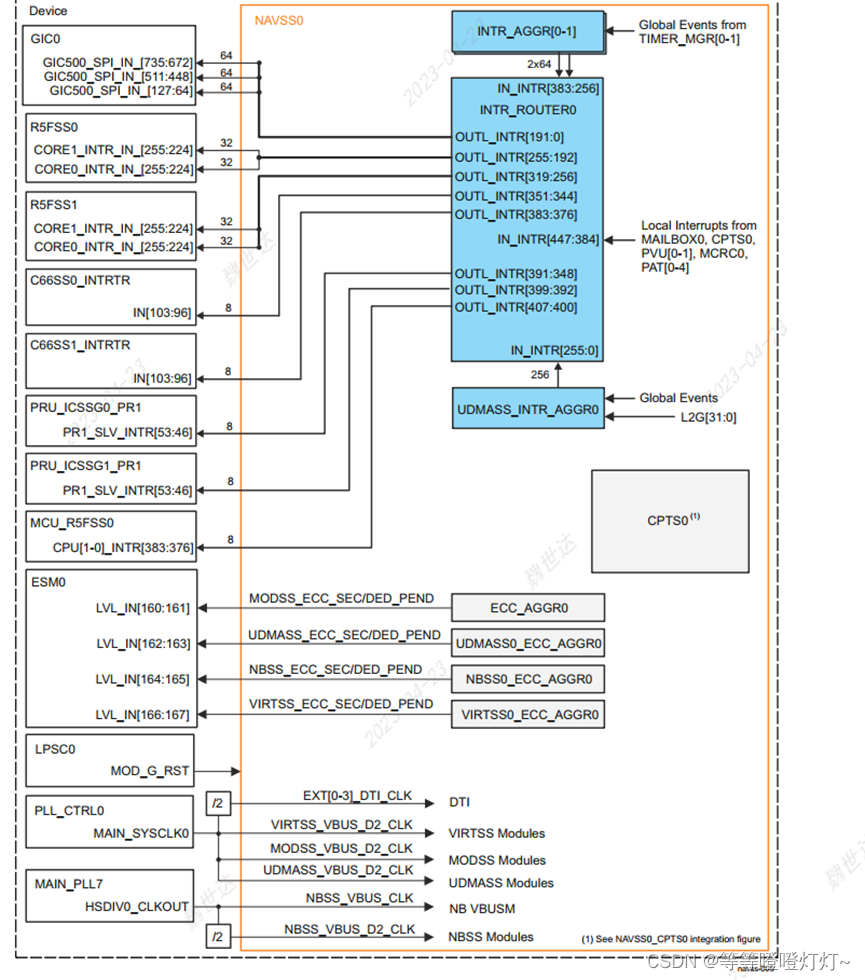

NAVSS0 集成框图

集成框图如下:

说明:

- NAVSS0_MODSS 参考时钟为 MODSS_VBUS_D2_CLK, 时钟源为 MAIN_SYSCLK0;

- NAVSS0_MODSS 的复位信号为 MODSS_RST, 复位信号源为 MOD_G_RST,来自 LPSC0;

- NAVSS0 的中断由

INTR_ROUTER0配置,可输出给芯片上的所有处理器核。

NAVSS0 中 INTR_ROUTER0输出中断与处理器关系

对于INTR_ROUTER0 生成的不同中断号的中断,可由不同处理器处理,中断号与处理器关系如下:

| INTR_ROUTER0 输出中断号 | 目的处理器 | 目的处理器输入中断号 |

|---|---|---|

| INTR_ROUTER0_OUTL_INTR[63:0] | A72SS0 | GIC500_SPI_IN_[127:64] |

| INTR_ROUTER0_OUTL_INTR[223:192] | R5FSS0_CORE0 | CORE0_INTR_IN_[255:224] |

| INTR_ROUTER0_OUTL_INTR[255:224] | R5FSS0_CORE1 | CORE1_INTR_IN_[255:224] |

| INTR_ROUTER0_OUTL_INTR[287:256] | R5FSS1_CORE0 | CORE0_INTR_IN_[255:224] |

| INTR_ROUTER0_OUTL_INTR[319:288] | R5FSS1_CORE1 | CORE1_INTR_IN_[255:224] |

| INTR_ROUTER0_OUTL_INTR[407:400] | MCU_R5FSS0(core0 与core1) | CORE0/1_INTR_IN_[383:376] |

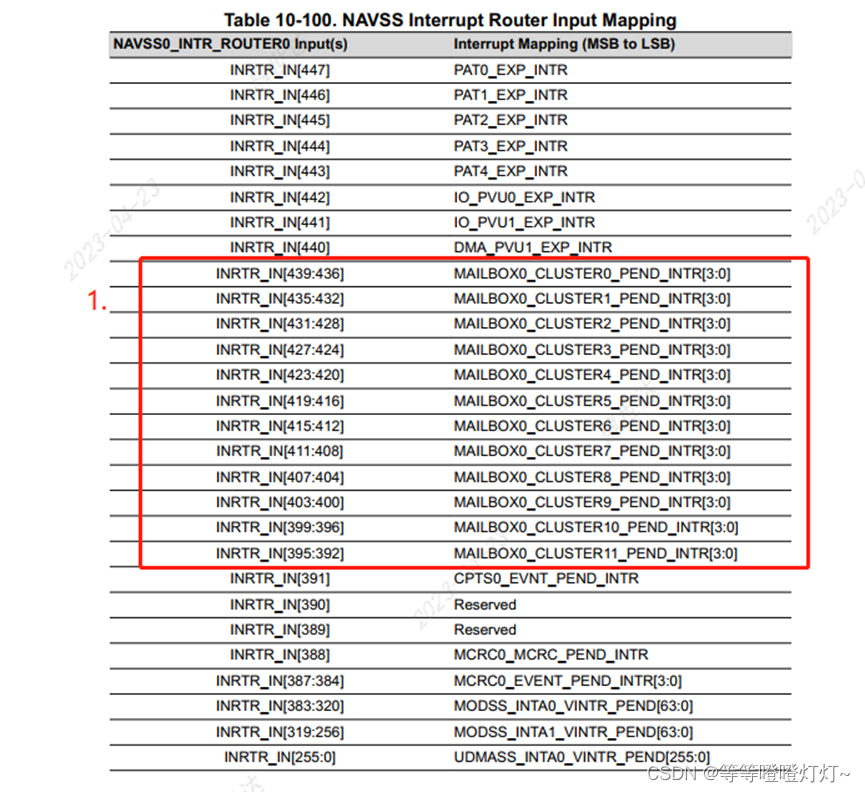

NAVSS0 中 INTR_ROUTER0 输入中断号

INTR_ROUTER0 的输入中断号映射关系如下:

说明:

MAILBOX0可生成的48个中断,由INTR_IN[439:392]捕获。

NAVSS0 中 INTR_ROUTER0 路由配置

对于 INTR_ROUTER0 的某一个中断输入,我们可以将该中断输入信号绑定到某一指定的 INTR_ROUTER0 的中断输出信号上,实现中断路由功能。

中断路由配置寄存器为 INTR_ROUTER_MUXCNTL_[1FF:0] 寄存器配置:

- 对于指定的

中断输出信号y,选择对应的INTR_ROUTER_MUXCNTL_y寄存器进行配置; INTR_ROUTER_MUXCNTL_y寄存器的BIT[8:0].MUX_CONTROL位域选择自定义的中断输入信号;INTR_ROUTER_MUXCNTL_y寄存器的BIT16. INT_ENABLE位域使能中断输出。