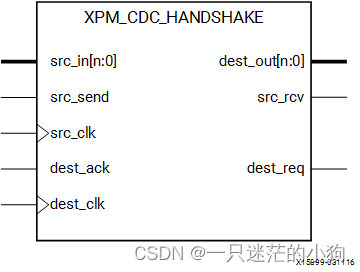

Parameterized Macro: Bus Synchronizer with Full Handshake(参数化宏:具有完全握手的总线同步器)

- MACRO_GROUP: XPM

- MACRO_SUBGROUP: XPM_CDC

- Families: UltraScale, UltraScale+

1、 Introduction(介绍)

此宏使用握手信令将输入总线从源时钟域传输到目标时钟域。应使用此宏的一个示例是,传输的数据与使用GRAY编码的XPM_CDC_GRAY宏不兼容。

为了使该宏正确运行,需要进行完全握手,即确认已接收到数据传输,并重置握手信号—必须在启动另一个数据传输之前完成。

可以定义同步器中用于在时钟域之间单独传输握手信号的寄存器级的数量。还可以包含内部握手逻辑,以确认接收到目标时钟域上的数据。

启用此功能后,当断言数据有效(dest_req)时,必须立即消耗输出(dest_out)。还可以启用仿真特性来生成消息,以报告宏的任何潜在滥用。当提供给宏的信令违反上述使用指南时,这些消息将产生错误。

注:当XPM_CDC_HANDSHAKE模块用于设计并运行report_CDC时,此模块中同步的数据总线将报告为CDC-15类型的警告,即时钟使能控制的CDC。可以安全地忽略此警告。从2018.3开始,通过在Tcl约束文件中添加CDC-15豁免,此警告已被抑制。

2、Port Descriptions(端口声明)

| 端口 | 方向 | 宽度 | 时钟域 | 敏感类型 | 如未使用处理方法 | 功能 |

| dest_ack | 输入 | 1 | dest_clk | 高电平 | 0 | 如果DEST_EXT_HSK=1,则目的地逻辑确认。 DEST_EXT_HSK=0时未使用。 断言该信号表示dest_out上的数据已被目的地逻辑捕获。 一旦dest_req被解除断言,就应该解除该信号的断言,从而完成目的时钟域上的握手,并指示目的逻辑已准备好进行新的数据传输。 |

| dest_clk | 输入 | 1 | NA | 上升沿敏感 | 激活 | 目标时钟 |

| dest_out | 输出 | WIDTH | dest_clk | NA | 激活 | 与目标时钟域同步的输入总线(src_in)。 此输出是寄存器类型。 |

| dest_req | 输出 | 1 | dest_clk | 高电平 | 激活 | 该信号的断言指示已经接收到新的dest_out数据,并且准备由目的地逻辑使用或捕获。 •当DEST_EXT_HSK=1时,一旦源握手确认目标时钟域已接收到传输的数据,该信号将取消断言。 •当DEST_EXT_HSK=0时,当DEST_out总线有效时,该信号在一个时钟周期内断言。 此输出是寄存器类型。 |

| src_clk | 输入 | 1 | NA | 上升沿敏感 | 激活 | 源时钟 |

| src_in | 输入 | WIDTH | src_clk | NA | 激活 | 将被目的时钟同步的输入总线 |

| src_rcv | 输出 | 1 | src_clk | 高电平 | 激活 | 来自目标逻辑的已接收src_in的确认。 一旦目的地握手完全完成,该信号将被取消断言,从而完成完整的数据传输。 此输出为寄存器类型。 |

| src_send | 输入 | 1 | src_clk | 高电平 | 激活 | 该信号的断言允许src_in总线与目标时钟域同步。 •只有当src_rcv被取消断言时,才应断言该信号,表明 之前的数据传输已完成。 •只有在src_rcv被断言时,该信号才应被取消断言,确认src_in已被目标逻辑接收。 |

3、 Design Entry Method

| Instantiation(实例化) | 是 |

| Inference(推断) | 否 |

| IP and IP Integrator Catalog | 否 |

4、 Available Attributes

| 属性 | 类型 | 可用值 | 默认值 | 描述 |

| DEST_EXT_HSK | DECIMAL | 1,0 | 1 | 0-将在宏中实现内部握手,以确认接收到目标时钟域上的数据。 使用此选项时,必须消耗有效的dest_out输出 以避免任何数据丢失。 1-用户必须实现外部握手逻辑,以确认接收到目标时钟域上的数据。 |

| DEST_SYNC_FF | DECIMAL | 2 至10 | 4 | 用于同步目标时钟域中的信号的寄存器级数。 |

| INIT_SYNC_FF | DECIMAL | 0,1 | 0 | 0-禁用同步寄存器上的行为模拟初始化值。 1-在同步寄存器上启用行为模拟初始化值。 |

| SIM_ASSERT_CHK | DECIMAL | 0,1 | 0,1 | 0-禁用模拟消息报告。与潜在滥用相关的信息将不会被报告。 1-启用模拟消息报告。将报告与潜在滥用有关的信息。 |

| SRC_SYNC_FF | DECIMAL | 2 至10 | 4 | 用于同步源时钟域中的信号的寄存器级数。 |

| WIDTH | DECIMAL | 1至1024 | 1 | 将同步到目标时钟域的总线宽度。 |

5、

5.1 VHDL Instantiation Template

除非它们已经存在,否则复制以下两个语句并将它们粘贴到实体声明之前。

Library xpm;

use xpm.vcomponents.all;-- xpm_cdc_handshake: Bus Synchronizer with Full Handshake

-- Xilinx Parameterized Macro, version 2022.2

xpm_cdc_handshake_inst : xpm_cdc_handshake

generic map (

DEST_EXT_HSK => 1, -- DECIMAL; 0=internal handshake, 1=external handshake

DEST_SYNC_FF => 4, -- DECIMAL; range: 2-10

INIT_SYNC_FF => 0, -- DECIMAL; 0=disable simulation init values, 1=enable simulation init values

SIM_ASSERT_CHK => 0, -- DECIMAL; 0=disable simulation messages, 1=enable simulation messages

SRC_SYNC_FF => 4, -- DECIMAL; range: 2-10

WIDTH => 1 -- DECIMAL; range: 1-1024

)

port map (

dest_out => dest_out, -- WIDTH-bit output: Input bus (src_in) synchronized to destination clock domain.

-- This output is registered.

dest_req => dest_req, -- 1-bit output: Assertion of this signal indicates that new dest_out data has been

-- received and is ready to be used or captured by the destination logic. When

-- DEST_EXT_HSK = 1, this signal will deassert once the source handshake

-- acknowledges that the destination clock domain has received the transferred

-- data. When DEST_EXT_HSK = 0, this signal asserts for one clock period when

-- dest_out bus is valid. This output is registered.

src_rcv => src_rcv, -- 1-bit output: Acknowledgement from destination logic that src_in has been

-- received. This signal will be deasserted once destination handshake has fully

-- completed, thus completing a full data transfer. This output is registered.

dest_ack => dest_ack, -- 1-bit input: optional; required when DEST_EXT_HSK = 1

dest_clk => dest_clk, -- 1-bit input: Destination clock.

src_clk => src_clk, -- 1-bit input: Source clock.

src_in => src_in, -- WIDTH-bit input: Input bus that will be synchronized to the destination clock

-- domain.

src_send => src_send -- 1-bit input: Assertion of this signal allows the src_in bus to be synchronized

-- to the destination clock domain. This signal should only be asserted when

-- src_rcv is deasserted, indicating that the previous data transfer is complete.

-- This signal should only be deasserted once src_rcv is asserted, acknowledging

-- that the src_in has been received by the destination logic.

);

-- End of xpm_cdc_handshake_inst instantiation5.2 Verilog Instantiation Template

// xpm_cdc_handshake: Bus Synchronizer with Full Handshake

// Xilinx Parameterized Macro, version 2022.2

xpm_cdc_handshake #(

.DEST_EXT_HSK(1), // DECIMAL; 0=internal handshake, 1=external handshake

.DEST_SYNC_FF(4), // DECIMAL; range: 2-10

.INIT_SYNC_FF(0), // DECIMAL; 0=disable simulation init values, 1=enable simulation init values

.SIM_ASSERT_CHK(0), // DECIMAL; 0=disable simulation messages, 1=enable simulation messages

.SRC_SYNC_FF(4), // DECIMAL; range: 2-10

.WIDTH(1) // DECIMAL; range: 1-1024

)

xpm_cdc_handshake_inst (

.dest_out(dest_out), // WIDTH-bit output: Input bus (src_in) synchronized to destination clock domain.

// This output is registered.

.dest_req(dest_req), // 1-bit output: Assertion of this signal indicates that new dest_out data has been

// received and is ready to be used or captured by the destination logic. When

// DEST_EXT_HSK = 1, this signal will deassert once the source handshake

// acknowledges that the destination clock domain has received the transferred data.

// When DEST_EXT_HSK = 0, this signal asserts for one clock period when dest_out bus

// is valid. This output is registered.

.src_rcv(src_rcv), // 1-bit output: Acknowledgement from destination logic that src_in has been

// received. This signal will be deasserted once destination handshake has fully

// completed, thus completing a full data transfer. This output is registered.

.dest_ack(dest_ack), // 1-bit input: optional; required when DEST_EXT_HSK = 1

.dest_clk(dest_clk), // 1-bit input: Destination clock.

.src_clk(src_clk), // 1-bit input: Source clock.

.src_in(src_in), // WIDTH-bit input: Input bus that will be synchronized to the destination clock

// domain.

.src_send(src_send) // 1-bit input: Assertion of this signal allows the src_in bus to be synchronized to

// the destination clock domain. This signal should only be asserted when src_rcv is

// deasserted, indicating that the previous data transfer is complete. This signal

// should only be deasserted once src_rcv is asserted, acknowledging that the src_in

// has been received by the destination logic.

);

// End of xpm_cdc_handshake_inst instantiation

![P1043 [NOIP2003 普及组] 数字游戏](https://img-blog.csdnimg.cn/img_convert/264c03843149c03db00b9f41afdbea63.png)