Multisim电路仿真与实验:包含连续时间系统的模拟、周期信号频谱分析、组合逻辑电路:竞争冒险、数字锁

文章目录

- Multisim电路仿真与实验:包含连续时间系统的模拟、周期信号频谱分析、组合逻辑电路:竞争冒险、数字锁

- 连续时间系统的模拟

- 实验目的

- 实验仪器

- 实验原理(验证性实验)/设计过程(设计性实验)

- 实验电路图

- 实验结果

- 周期信号频谱分析

- 实验目的

- 实验原理(验证性实验)/设计过程(设计性实验)

- 实验电路图

- 组合逻辑电路

- 竞争冒险

- 实验目的

- 实验原理(验证性实验)/设计过程(设计性实验)

- 实验电路图

- 实验结果

- 数字锁

- 实验目的

- 实验原理(验证性实验)/设计过程(设计性实验)

- 实验电路图

- 实验结果

- 实验小结(总)

连续时间系统的模拟

实验目的

-

学习如何根据给定的连续系统的传输函数,用基本运算单元组成模拟装置。

-

掌握将Multisim软件用于系统模拟的基本方法。

实验仪器

硬件:无

软件:Multisim14.0(注:本次三个实验的实验仪器均同上,故后文不赘述)

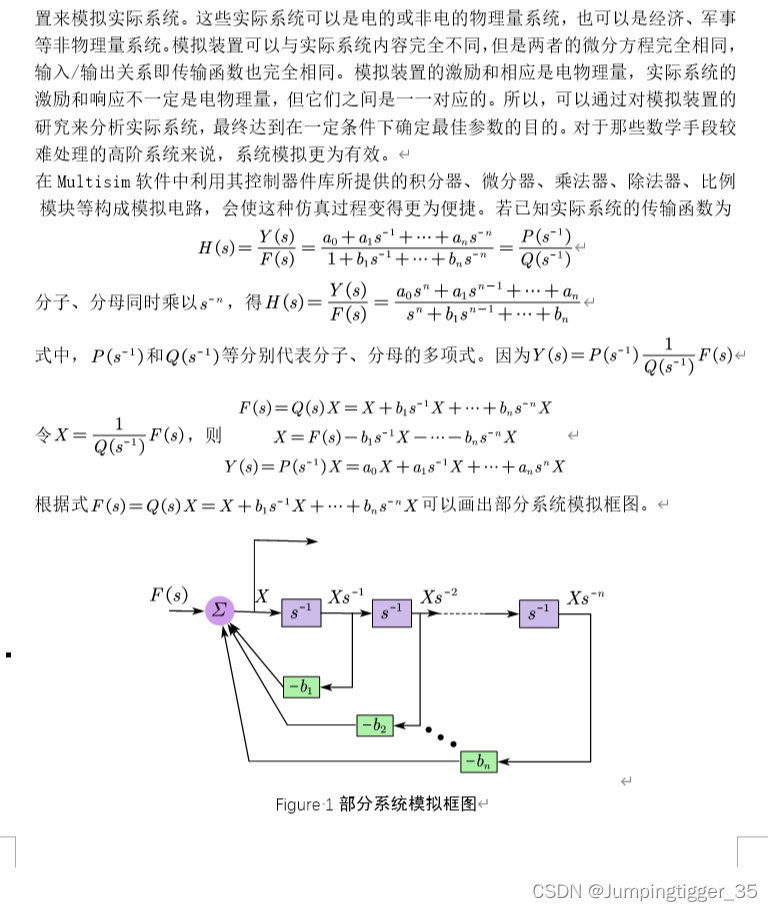

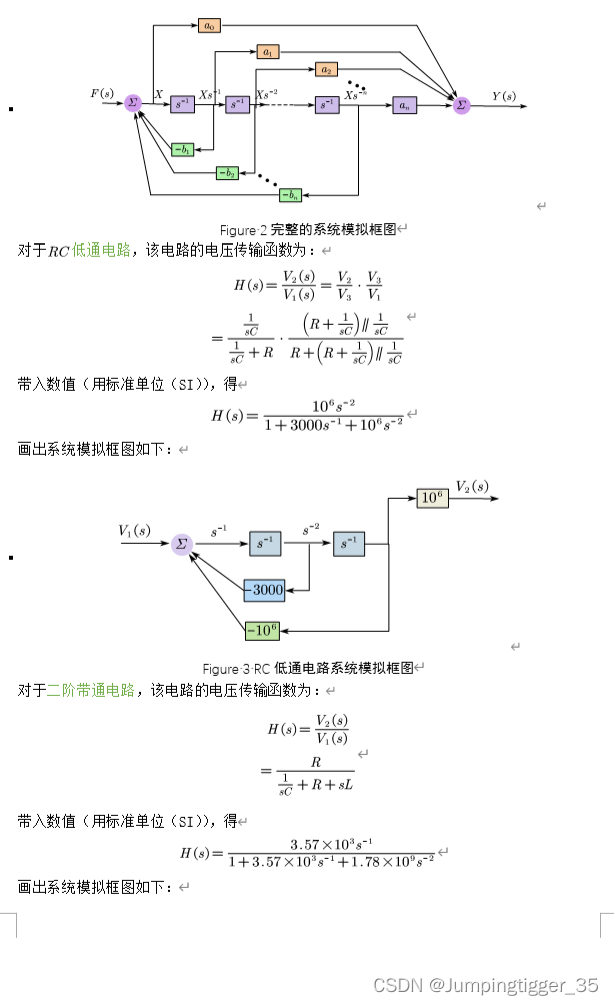

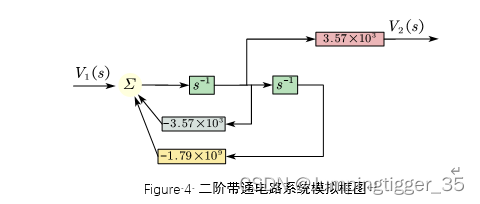

实验原理(验证性实验)/设计过程(设计性实验)

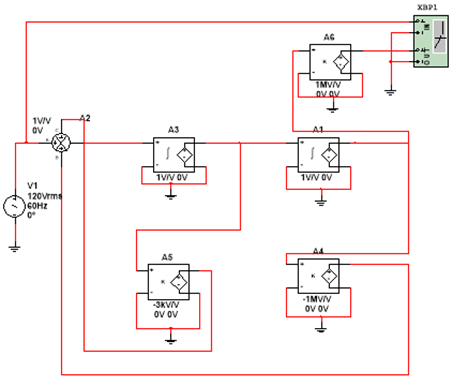

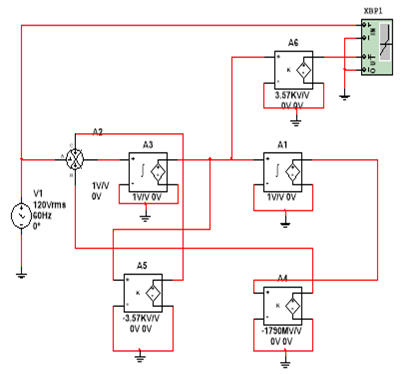

实验电路图

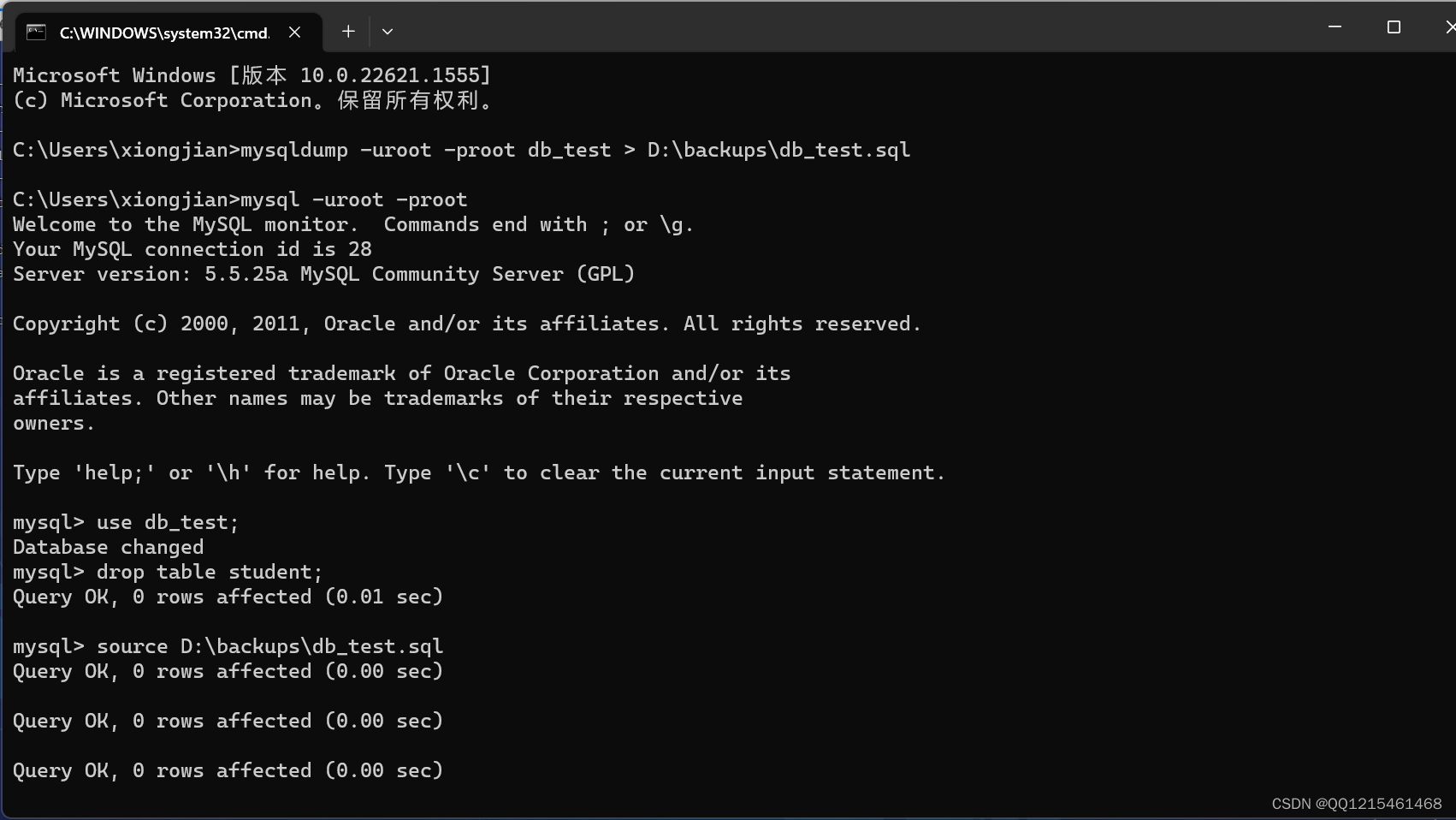

题目要求:

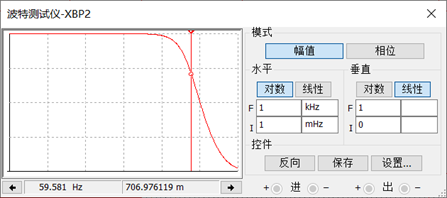

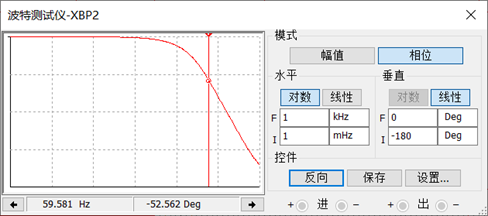

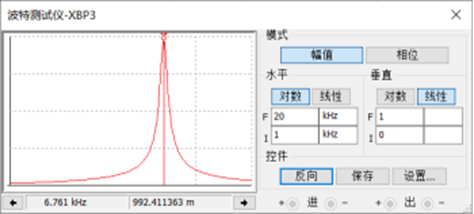

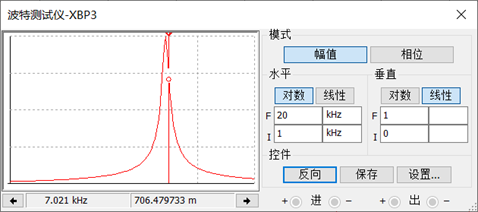

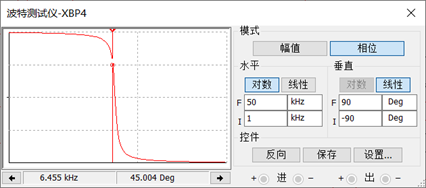

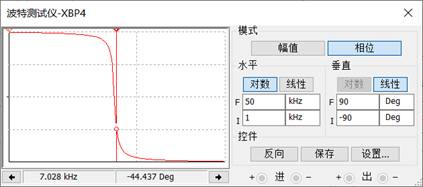

- 直接测量图所示电路的幅频特性、相频特性,并测出相应的数据。测点自定,但半功率点和谐振频率必须在其中。

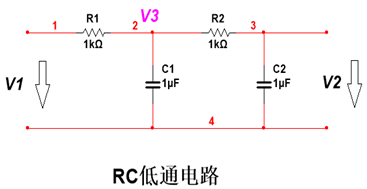

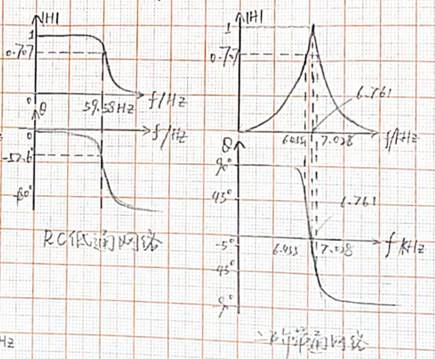

RC低通电路

二阶带通电路

table 1 直接测量结果

| 测量项目 | 最大值 | 最小值 | 半功率点 | 谐振频率/Hz | 相位/° |

|---|---|---|---|---|---|

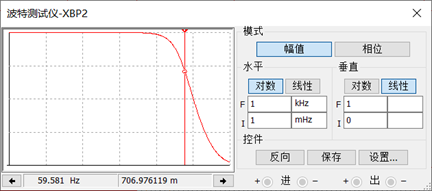

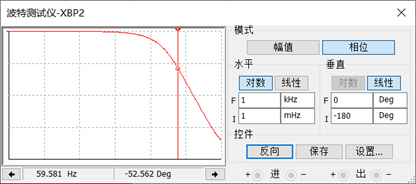

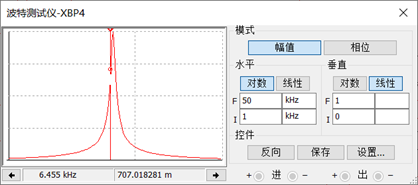

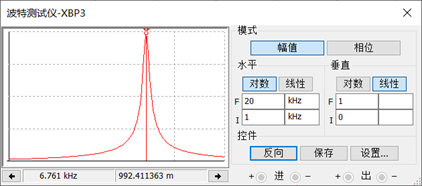

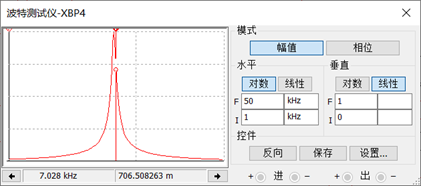

| RC低通 | 1 | 0 | 706.98m | 59.581 | -52.562 |

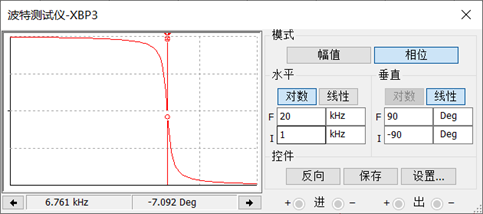

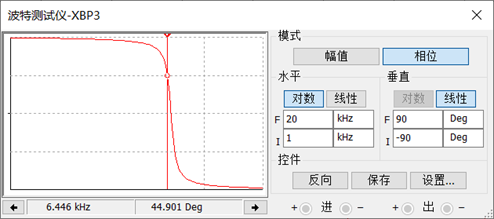

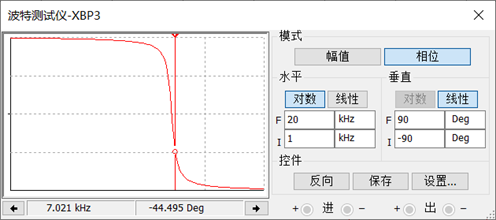

| 二阶带通 | 992.41m (6.761kHz) | 0 (-7.09°) | 707.13m | 6.446k | 44.9 |

| 706.48m | 7.021k | -44.5 |

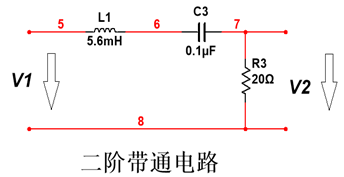

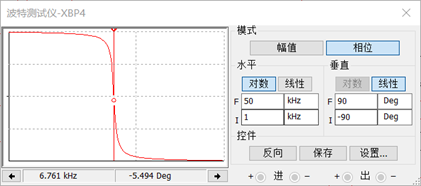

- 根据预习时计算出的传输函数H(s)分别搭建两个电路的系统模拟测试电路,分别测量幅频特性、相频特性,并按直接测量时所选的测点进行测量。

RC低通电路

二阶带通电路

table 2 间接测量结果

| 测量项目 | 最大值 | 最小值 | 半功率点 | 谐振频率/Hz | 相位/° |

|---|---|---|---|---|---|

| RC低通 | 1 | 0 | 706.98m | 59.581 | -52.56 |

| 二阶带通 | 992.41m (6.76kHz) | 0 (-5.49°) | 707.92m | 6.455k | 45.00 |

| 706.99m | 7.028k | -44.44 |

实验结果

Figure 13 手绘波形图

周期信号频谱分析

实验目的

-

了解和掌握周期信号频谱分析的基本概念。

-

掌握用软件进行频谱分析的基本方法。

-

理解周期信号时域参数变化对其谐波分量的影响及变化趋势。

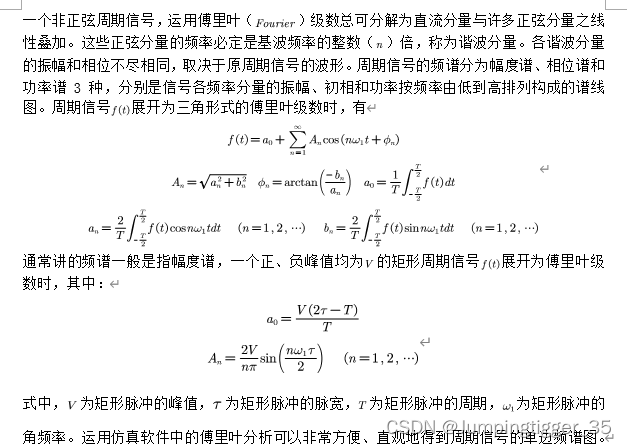

实验原理(验证性实验)/设计过程(设计性实验)

实验电路图

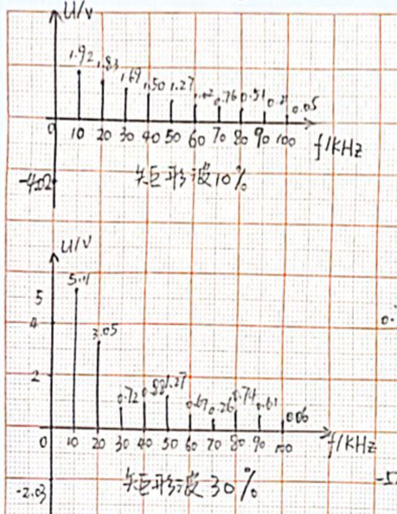

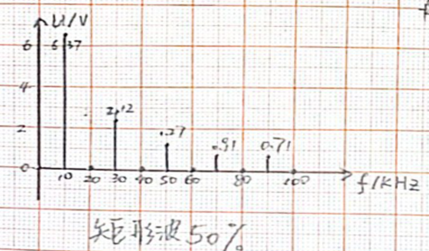

Table 3 直流分量和各谐波分量的幅度

| 波形占空比 | f/kHz | f/kHz | f/kHz | f/kHz | f/kHz | f/kHz | f/kHz | f/kHz | f/kHz | f/kHz | f/kHz |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | 10 | 20 | 30 | 40 | 50 | 60 | 70 | 80 | 90 | 100 | |

| 矩形波10% | -4.02 | 1.96 | 1.86 | 1.71 | 1.51 | 1.27 | 1.01 | 0.74 | 0.47 | 0.23 | 0.01 |

| 矩形波30% | -2.01 | 5.15 | 3.03 | 0.66 | 0.93 | 1.27 | 0.63 | 0.28 | 0.76 | 0.57 | 0 |

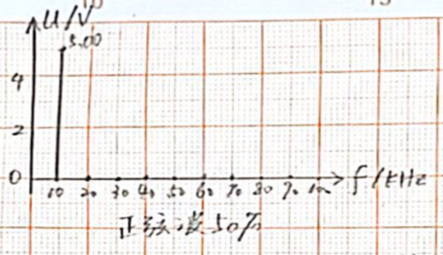

| 矩形波50% | 0 | 6.37 | 0 | 2.12 | 0 | 1.27 | 0 | 0.91 | 0 | 0.71 | 0 |

| 正弦波50% | 0 | 4.90 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 三角波50% | 0 | 4.10 | 0 | 0.45 | 0 | 0.16 | 0 | 0.08 | 0 | 0.05 | 0 |

| 三角波70% | 0 | 3.91 | 1.15 | 0.17 | 0.18 | 0.19 | 0.08 | 0.03 | 0.07 | 0.04 | 0 |

| 三角波90% | 0 | 3.48 | 1.65 | 1.01 | 0.67 | 0.45 | 0.30 | 0.19 | 0.10 | 0.04 | 0 |

| n = | 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 |

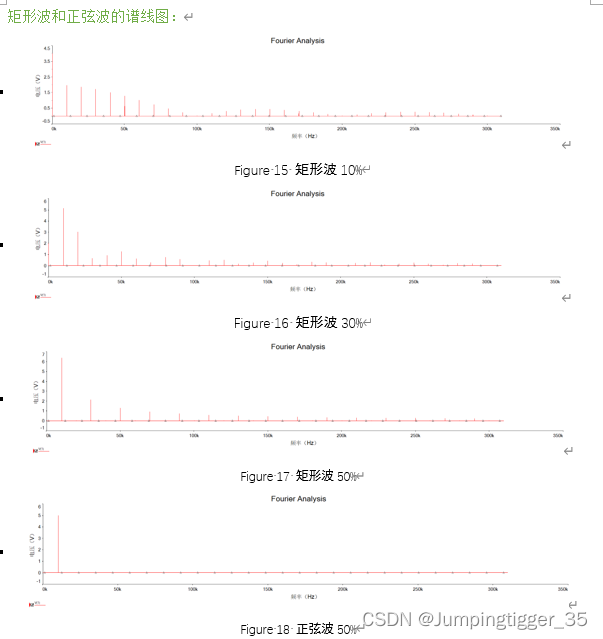

矩形波和正弦波的谱线图:

思考题

-

大多数非正弦周期信号的幅度谱包含若干条谱线,但其主要能量集中在谱线幅度包络线的第一个零点以内,这段包络线称为主峰,其频率范围称为有效频带宽度。

-

矩形周期信号的直流、基波和各谐波分量的幅值与矩形脉冲幅度成正比。

-

在有效频带宽度内,矩形周期信号谐波幅度按抽样函数规律收敛,三角形周期信号谐波幅度按抽样函数的平方规律收敛。

-

矩形周期信号的幅度和周期保持不变,随着占空比的增加(即脉宽加大),主峰高度越高,主峰宽度越窄,各谱线间隔越窄,主峰包含的谱线数量越少,有效频带宽度越窄,主峰内高次谐波分量越少。

-

理想的正弦波的幅度谱包含1条谱线,证明其只有基频分量,而无谐波分量,如果能测出谐波分量,说明该正弦波已有失真。

组合逻辑电路

竞争冒险

实验目的

-

掌握判断逻辑电路冒险的方法。

-

了解消除险象的方法。

-

用实验观察逻辑冒险的现象。

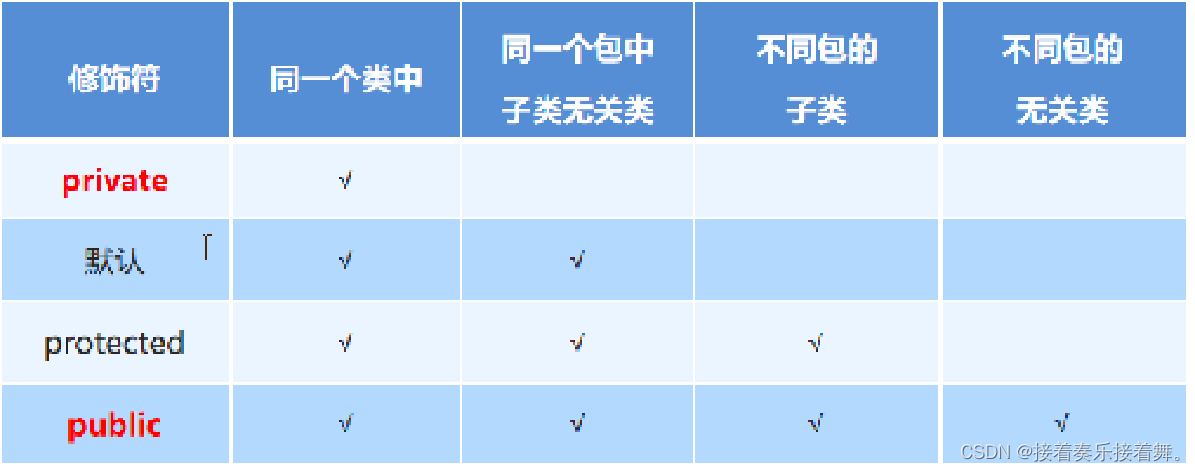

实验原理(验证性实验)/设计过程(设计性实验)

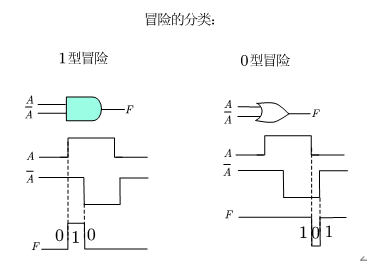

1.静态逻辑险象

输入信号所经路径不同而引起的冒险现象,按短暂尖峰极性的不同,可将冒险分为“0-1-0”型险象(也称“1”型)和“1-0-1”型险象(也称“0”型)

2.逻辑险象的判断。

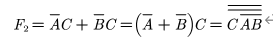

(1)当逻辑函数中出现下列结果时将出现逻辑现象: ,存在“1-0-1”型险象; ,存在“0-1-0”型险象。

(2)卡诺图若出现“相切”的卡诺圈,且相切部分未被另外卡诺圈包围,即可断定存在逻辑冒险。

3. 险象的消除方法。险象对数字系统带来的危害,视它的负载电路性质而定。 如果负载是组合电路或惯性大的仪表,则影响不大;如果负载是时序电路,而且毛刺的宽度等于或大于后级的响应时间,则会使时序电路中的触发器错误动作。显然该情况下险象是有害的。险象的消除有以下几种方法。

(1)修改逻辑设计。对逻辑险象来说,可在原函数中加上多余项或乘上多余因 子(对或与表达式),也就是在卡诺图中,用一个多余圈将两个相切的卡诺圈连接起来。或将卡诺图重圈,避免相切。其目的是使原函数 不再可能化为 或 的形式,从而消除逻辑现象。可以证明,添加多余项后,原来的险象消除了,但这样却增加了设备量。

(2)加滤波电路。在输出波形要求不高的情况下,可在输出端加一个 积分器(低通滤波器)或直接加滤波电容,适当选取 值将毛刺压抑在电路正常工作的允许范围内,从而消除毛刺对后级工作的影响。

(3)加取样脉冲。险象仅发生在输入信号变化的瞬间。因此,在组合电路输出门的一个输入端加入一个取样脉冲,就可以有效地消除任何险象。取样脉冲的出现时间一定要与输入信号的变化时间错开。这样,通过取样后就能正确反映组合电路的输出值。但必须指出,加取样脉冲后,输出将不是电位信号,而是脉冲信号。

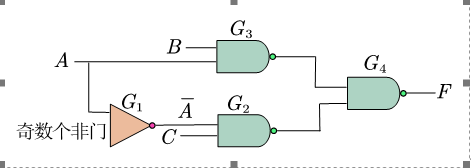

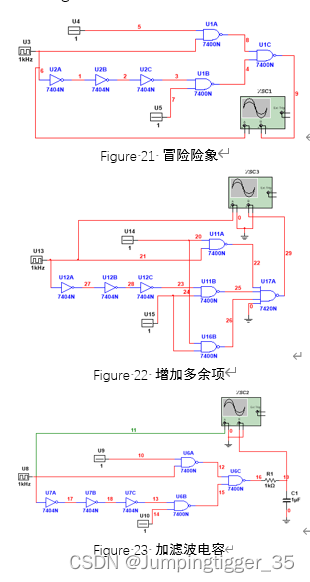

P55 6有一逻辑电路,如图

Figure 20 竞争冒险的逻辑电路

(1) 试用示波器来判断是否存在逻辑险象、险象类型及险象出现的条件。

(2) 在输出端加接滤波电容,观察毛刺的变化情况。

(3) 换用修改逻辑设计的方法来消除所出现的险象,并通过实验验证。

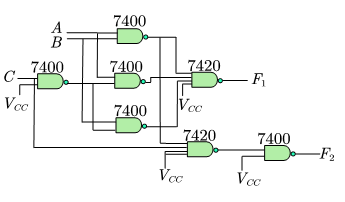

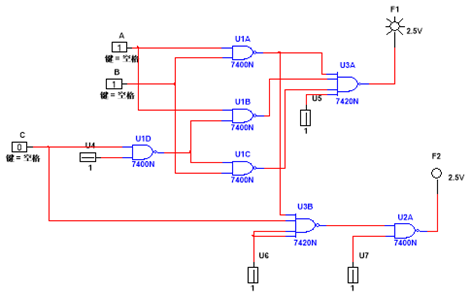

实验电路图

实验结果

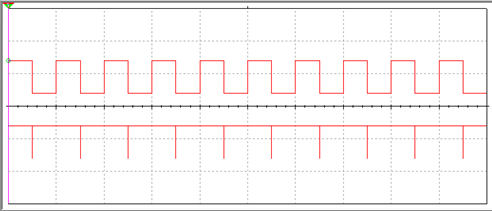

- 试用示波器来判断是否存在逻辑险象、现象类型及险象出现的条件

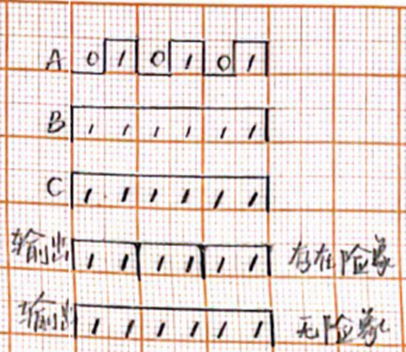

Figure 19 用来观测图

- 存在逻辑险象

- 是“0”型冒险

- 条件:当B=C=1,A从1跳变到0时,出现“1-0-1”型险象

-

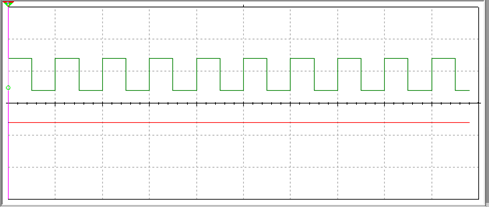

在输出端加接滤波电容,观察毛刺的变化情况

Figure 20 发现冒险消除

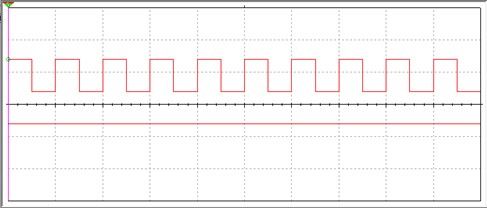

- 换用修改逻辑设计的方法来消除所出现的险象,并通过实验验证

Figure 21 增加多余项BC

Figure 22 手绘波形图

数字锁

实验目的

-

掌握组合逻辑电路的实际应用。

-

掌握组合逻辑电路的设计方法。

-

用实验验证所设计电路的逻辑功能。

-

掌握基本门多余端的处理方法。

实验原理(验证性实验)/设计过程(设计性实验)

组合逻辑电路是指纯由小、中、大规模集成门构成的电路,电路中没有记忆元器件。

组合逻辑电路的设计:

(1) 正确将需求抽象为逻辑关系。

(2) 列出真值表。

(3) 得到逻辑表达式。根据电气要求选用合理元器件。

(4) 根据制图标准,正确绘制逻辑电路图。

P55 5用与非门设计一数字锁逻辑电路,该锁有三个按钮A、B、C,当A、B、C同时按下,或A、B同时按下,或只有A或B按下时开锁,若不符合上述条件应发出报警。

数字锁设计过程

设A、B、C分别为“1”时表示按键按下,为“0”时表示按键没按下。F1表示开锁信息,为“1”表示开锁,为“0”表示没开锁。F2表示报警信息,为“1”表示报警,为“0”表示没报警。

(1)将逻辑函数转换为真值表:

分析:题目隐含真值表第一行的信息,即不按键时既不报警也不开锁。

Table 4 真值表

| A | B | C | F1 | F2 |

|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 0 | 1 |

| 0 | 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 | 1 |

| 1 | 0 | 0 | 1 | 0 |

| 1 | 0 | 1 | 0 | 1 |

| 1 | 1 | 0 | 1 | 0 |

| 1 | 1 | 1 | 1 | 0 |

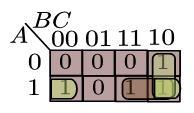

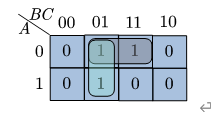

(2)依据真值表绘制卡诺图:

|  |

|---|---|

|  |

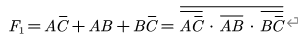

(3)根据表达式绘制逻辑电路图:

Figure 23 绘制数字锁逻辑电路

实验电路图

Figure 24 数字锁仿真电路图

实验结果

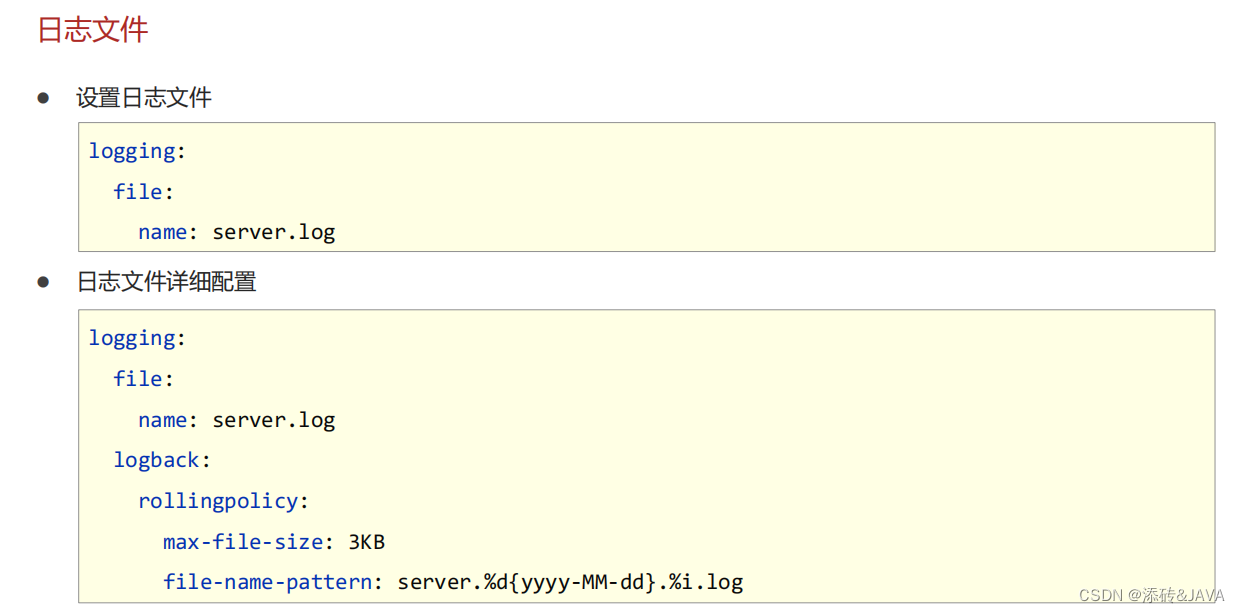

实验小结(总)

了解并学会使用Multisim元件库中的“加法器”(Voltage Summer)“积分器”(Voltage Integrator)“比例放大器”(Voltage Gain Block)搭建模拟系统。

结合仿真图与信号与系统分析所学可知:

(1) 周期矩形脉冲信号的频谱有如下特点。

离散性:指频谱由不连续的谱线组成。这种频谱称为不连续频谱或离散频谱。

谐波性:指频谱的每条谱线只能出现在基波频率的整数倍频率上,频谱中不可能存在频率为基波频率非整数倍的分量。

收敛性:指谱线的高度即各次谐波的振幅随n趋向于无穷大的总趋势衰减到零,频谱具有收敛性。

虽然是从周期矩形脉冲信号的频谱提取出的特点,但这三个特点代表了所有周期信号频谱的普遍特性。

对于周期信号的频带宽度:

理论上讲,周期信号的谐波分量是无限多的,但在实际工作中没有必要也不可能考虑无限多的谐波分量。因为谐波分量振幅具有收敛性,信号的能量主要集中在低频分量中,故只需考虑频率较低的一部分谐波分量。对于某个信号,从零频率开始到需要考虑的最高频率范围称为信号占有的频带宽度,简称带宽。

当脉冲宽度无限趋小时,频带宽度将无限趋大,此时信号能量就不再集中在低频分量中,而均匀分布在零到无限大的整个频段。事实上,一切脉冲信号的脉冲宽度与频带宽度是呈反比的。这反映了信号时间特性及频率特性间的关系。

掌握了组合电路竞争与冒险中冒险的分类与冒险的消除办法等。