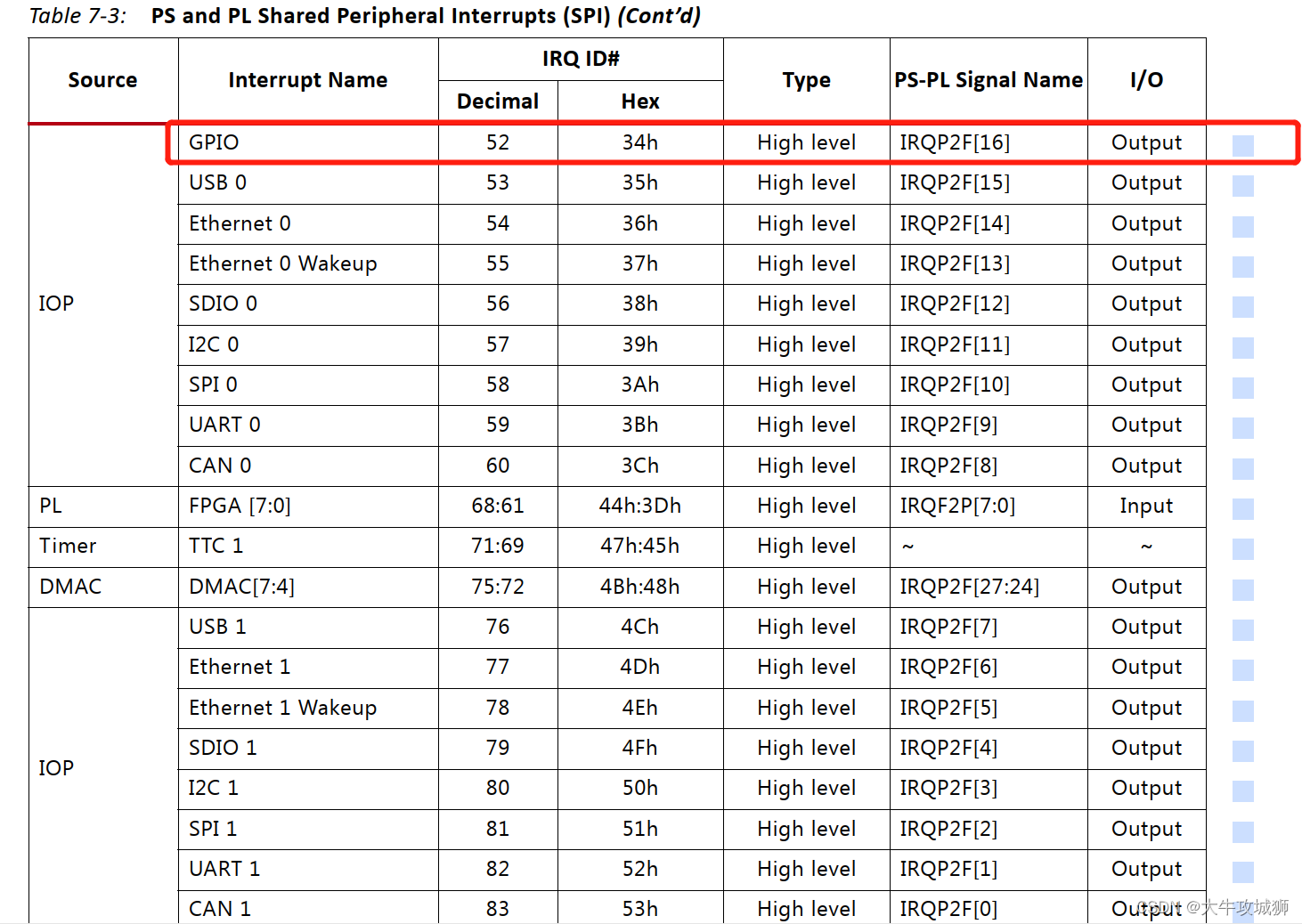

325t配置:

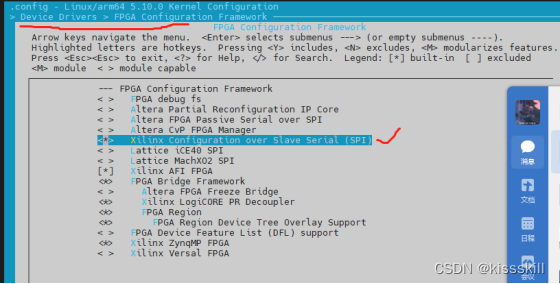

使用内核自带的linux-xlnx-xilinx-v2021.2/drivers/fpga/xilinx-spi驱动,做serial slave模式,设备树更改如下(根据

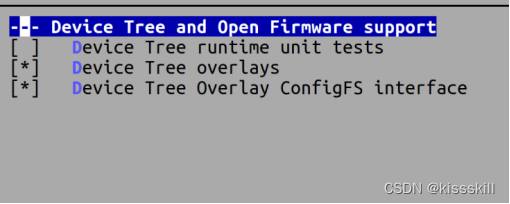

linux-xlnx-xilinx-v2021.2/Documentation/devicetree/bindings/fpga/xilinx-slave-serial.txt,修改)slave-serial需要将fpga的m0-m2引脚配置为slave-serial模式,在内核中开启配置

其他内核需要的配置请参考:Solution Zynq PL Programming With FPGA Manager - Xilinx Wiki - Confluence (atlassian.net)

在根节点下添加:

fpga-region1 {

device_type = “fpga-region”;

compatible = “fpga-region”;

fpga-mgr = <&fpga_mgr_spi>;

#address-cells = <0x1>;

#size-cells = <0x1>;

};

Spi节点添加:

&spi0 {

status = “okay”;

is-decoded-cs = <0>;

spi-max-frequency = <60000000>;

num-cs = <2>;

fpga_mgr_spi: fpga-mgr@0 {

compatible = “xlnx,fpga-slave-serial”;

spi-max-frequency = <60000000>;

spi-tx-bus-width = <0x04>;

spi-rx-bus-width = <0x04>;

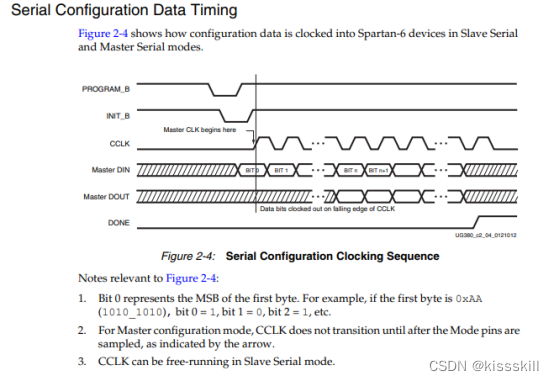

//spi-cpha; //注意极性,需要根据ug380等手册去定义,spi传输的时序,定义即为1,注释为0,根据手册,这里需要注释

reg = <0>; //注意片选没接,依旧需要标明

prog_b-gpios = <&gpio 44 GPIO_ACTIVE_LOW>;

init-b-gpios = <&gpio 51 GPIO_ACTIVE_LOW>;

done-gpios = <&gpio 50 GPIO_ACTIVE_HIGH>;

};

};

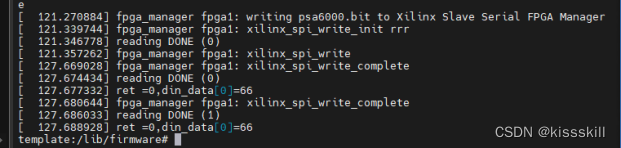

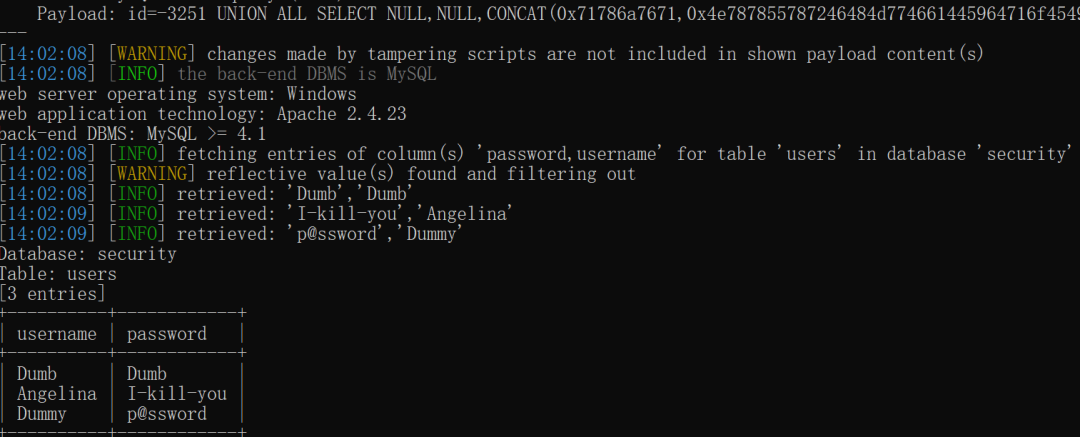

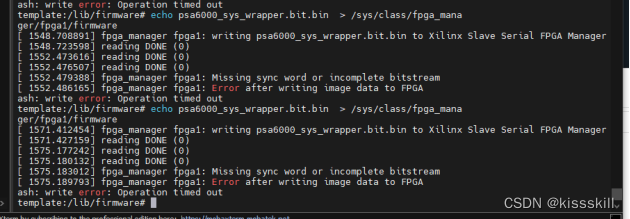

此时烧录会报错:(烧录的bin文件必须是325tfpga的bin文件)或者spi-cpha;开启了也会报以下错误

因为参考ug380手册可以知道slave-serial 模式fpga的时序极性都为0。

另外路径/sys/class/fpga_manager/fpga1/下有fpga的几种操作文件路径,相关操作报错可以查看status。错误信息查看(FPGA Manager — The Linux Kernel documentation)

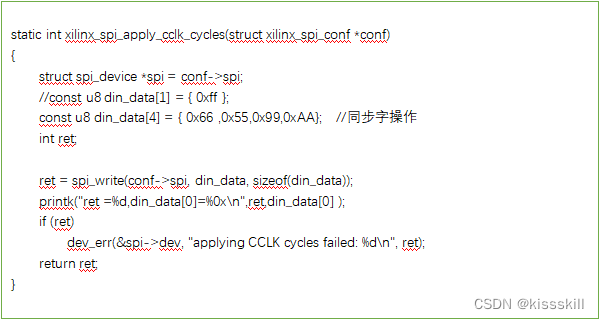

报同步字错误,需要在xilinx-spi.c中更改同步字(每个芯片的同步字不同)。与325t匹配:

烧录可以配置成功,配置不成功done引脚一直低,成功为高