系列文章目录

FPGA时序约束(一)基本概念入门及简单语法

FPGA时序约束(二)利用Quartus18对Altera进行时序约束

文章目录

- 系列文章目录

- 前言

- 基本时序路径

- 时钟偏差

- 寄存器到寄存器(reg2reg)

- 建立时间余量

- 保持时间余量

- Set input delay

- 系统同步接口路径分析(引脚到寄存器)

- 源同步接口的路径分析(引脚到寄存器)

- Set output delay

- 系统同步接口路径分析(寄存器到引脚)

- 源同步接口路径分析(寄存器到引脚)

- 引脚到引脚(set min/max delay)

前言

在读《FPGA时序约束与分析》吴厚航时记录的读书笔记,也是在上一篇系列文章继续学习时序分析。

基本时序路径

时钟偏差

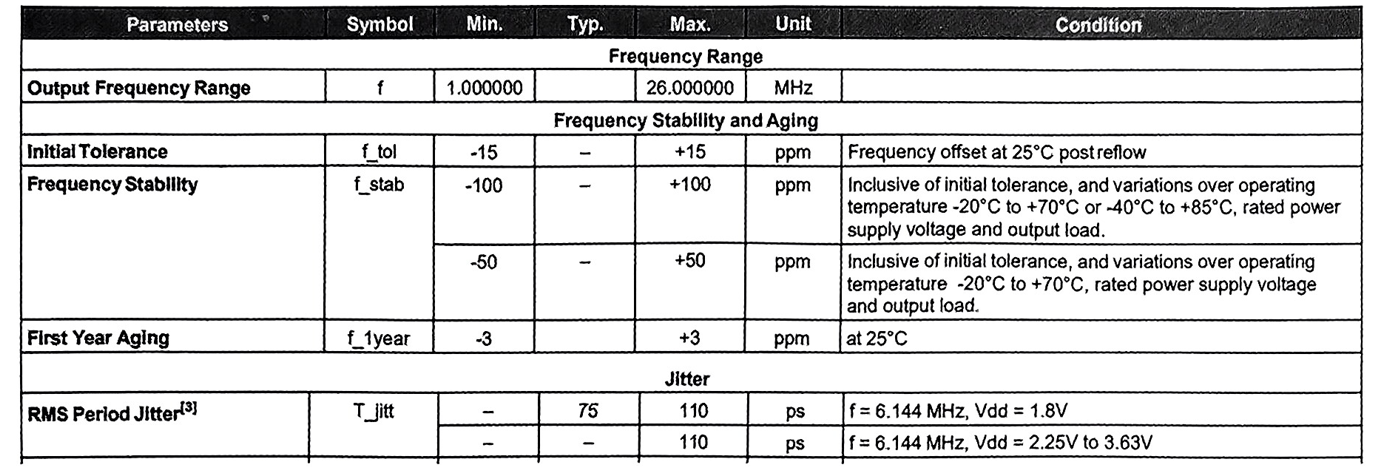

以SiT8021系列的晶振为例:

Frequency Tolerance(时钟精度):在这个手册中时initial Tolerance,±15ppm:每秒产生15us的偏差。如果时钟周期是25M,那么一个周期的偏差就是1/25M*(15/1000000)=0.6ps。ppm:part per million即百万分之一。

Frequency Stability(时钟稳定,指温漂):有的也叫Frequency versus Temperature Characteristics,可选50ppm和100ppm的两种,同样的算法,25M下,一个周期的偏差值就是2ps和4ps

Jitter(时钟抖动):晶振源固有的噪声和干扰通常会带来时钟信号的周期性偏差,就是图中的RMS Period Jitter。

FPGA中,会将时钟抖动作为Clock Uncertainty加以约束。

寄存器到寄存器(reg2reg)

以同时钟源进行分析:我们主要时分析计算数据到达的时间和时钟到达的时间进行制约,满足建立时间和保持时间。

(数据到达时间和数据需求时间)

在上篇系列文章中《FPGA时序约束(二)利用Quartus18对Altera进行时序约束》中也有分析,但是记录的不是很清楚,这里再重新分析一下。

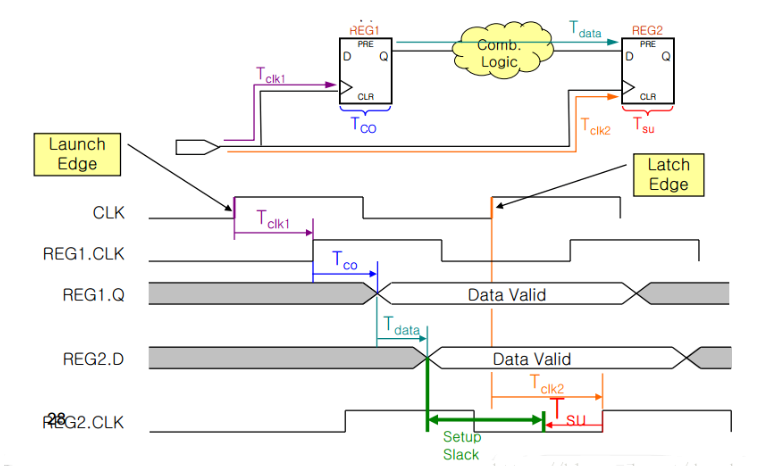

建立时间余量

建立时间余量计算公式中:时钟启动沿(launch edge)定义为0ns,时钟锁存沿(latch edge)为一个时钟周期。

launch是reg1数据发送,latch是reg2数据锁存,在寄存器到寄存器,数据锁存总是慢一个周期,见下图

Data Arrival Time=Launch Edge+Tclk1 ( max)+Td,这里的Td包括了Tco和Tdate

Data Required Time=Latch Edge+Tclk2 (min)-Tsu

建立时间余量:Setup Time Slack =Data Required Time-Data Arrival Time=Tclk2-Tclk1+一个周期-Tsu-Td。

作最坏打算,使约束满足最差情况:Tclk2取最小值,Tclk1取最大值,使得建立时间余量最小。

这里Tckl1和Tclk2有一段重复路径,在具体的路径下,Tcommon不存在最大值或最小值,但是实际计算中我们采用min的Tckl2和max的Tclk1中会包含Tcommon最大值和最小值,所以应该的计算公式是:(Tclk2(min)-Tcommon(min))-(Tclk1(max)-Tcommon(max)),即剔除掉Tcommon。

综上,所以需要补偿一个+Tcommon(max)-Tcommon(min)在最后建立余量公式中。

这个值即clock pessimism removal(上篇文章提到的时钟悲观,一般算在clock skew里面,时钟偏斜,Skew=Tclk2(min)-Tclk1(max)+Clock Pessimism)

最终加入Clock Uncertainty和Clock pessimism removal(CPR)(Tcommon(max)-Tcommon(min))后的结果是:

Setup Time Slack =Data Required Time-Data Arrival Time=Tclk2-Tclk1+Tclk2-Tclk1-Tsu-Td+CPR-clock uncertainty。

(书中这里介绍clock uncertainty,时钟源本身产生的不用周期的偏差,需要考虑,依我看,clock uncertainty只要在最终表达式中是减去,表示最坏影响)

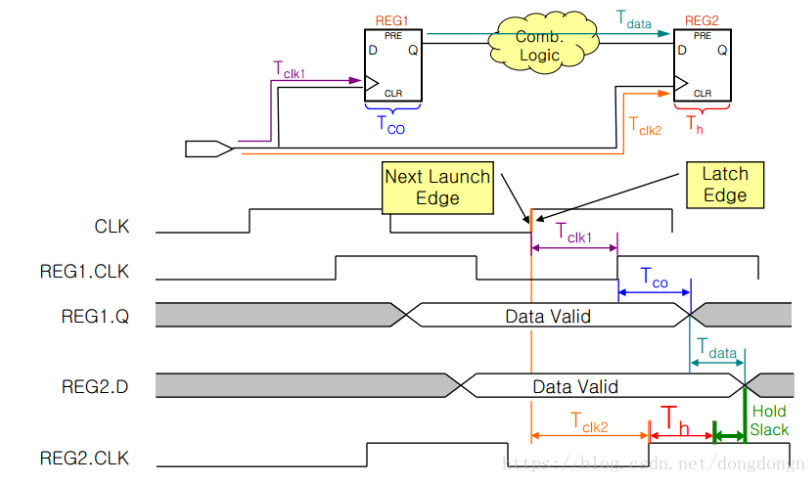

保持时间余量

保持时间余量计算公式中:时钟启动沿和时钟锁存沿都为0ns。可以看到是第二次数据launch时,要保证第一次launch的数据被latch的保持时间。

同理;

Data Arrival Time=Launch Edge+Tclk1( min)+Td

Data Required Time=Latch Edge+Tclk2 (max)+Th+Clock Uncertainty-Clock Pessimism

Hold Time Slack= Data Arrival Time-Data Required Time

保持时间余量的减数和被减数与建立时间余量是相反的,所以作最坏打算时,是Tclk1取min,Tclk2取max。

这里最后的表达式还是-Clock Uncertainty(始终将clock uncertainty作最坏的打算加入表达式中)

建立时间和保持时间余量是相对立的,平衡是最好的状态

Set input delay

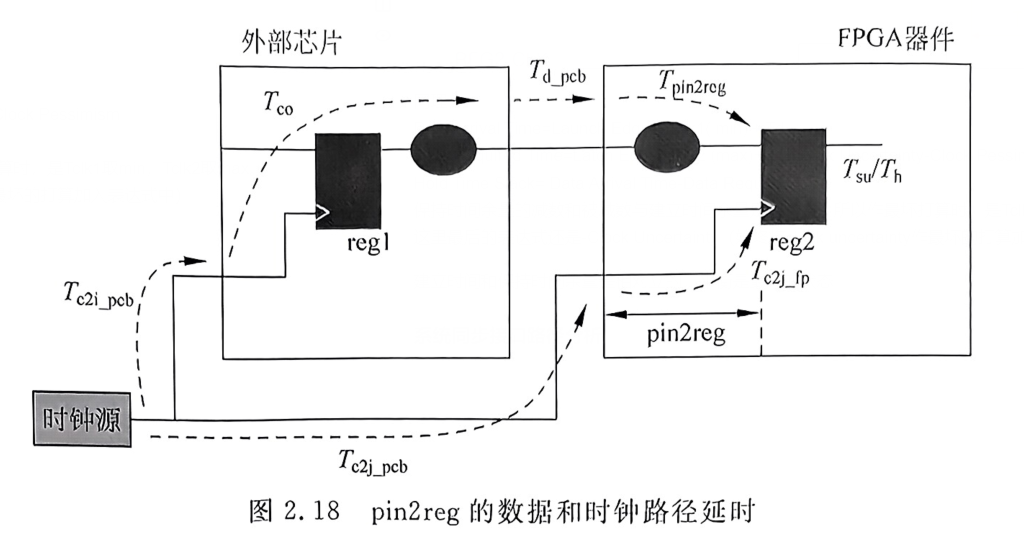

系统同步接口路径分析(引脚到寄存器)

系统同步接口:FPGA与外部芯片的时钟都由外部同一时钟源产生

分析pin2reg(pin to reg):

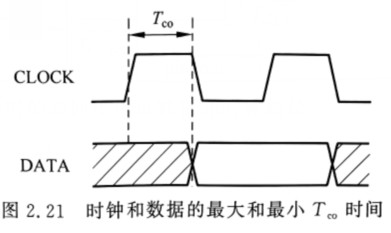

外部芯片的内部寄存器的状态一般不会给出详细的内部信息,但是再手册中通常都会给出芯片引脚的一些时序信息,如Tco(数据在时钟沿后多长时间范围内是有效的)、Tsu(建立时间)和Th(保持时间)等。

仍然用前面的reg2reg的方法来分析:

- Tc2i_pcb表示时钟信号从时钟源到外部芯片(源寄存器reg1)所经过的PCB走线延时。

- Tco表示时钟启动沿到达外部芯片引脚,一直到外部芯片数据引脚输出数据所经过的延时。这个延时包含了时钟从外部芯片输入引脚到源寄存器regl1的延时,及数据从reg1到芯片输出引脚的延时。

- Td_pcb是数据信号在PCB上的走线延时。

- Tpin2reg则是数据信号从FPGA器件的引脚到目的寄存器reg2输入端的延时,也就是pin2reg 实际要约束的路径延时。

- Tc2j_pcb表示时钟信号从时钟源到达FPGA器件引脚所经过的PCB走线延时。

- Tc2j_fp表示时钟信号从FPGA器件输人引脚到目的寄存器reg2所经过的时钟网络延时。

- Tsu表示目的寄存器的建立时间。

- Th表示目的寄存器的保持时间。

Data Arrival Time=Launch Edge+Tc2i_pcb( max)+Tco( max)+Td_pcb( max)+Tpin2reg(max)

Data Required Time=Latch Edge+Tc2j_pcb( min)+Tc2j_fp(min)-Tsu-Clock Uncertainty Time

Setup Time Slack=Data Required Time-Data Arrival Time

这里的时钟路径在不像前面的reg2reg有时钟共同路径,所以没有Clock Pessimisim Time。

在上面的公式中,只有Tpin2reg和Tc2j_fp的延时值是未知的。Tc2j_fp是时钟从FPGA输人引脚到FPGA寄存器的延时,通常在硬件电路设计时需要把这样的时钟信号分配到FPGA专用时钟引脚上,通常会走全局时钟网络(在上一篇系列文章有如何走线在全局时钟上),尽可能地减小时钟引脚到寄存器的时钟网络延时,所以这个路径的延时通常会是一个较小的时间值。

具有很大变数的是Tpin2reg,使用set_input_delay命令进行约束设置。set_input_delay命令所设定的最大值(-max)和最小值(-min)分别用建立时间和保持时间分析。

这里Data Required Time和Data Arrival Time不是一个固定公式,应该只是为了计算最后Setup Time Slack的值而创建的两个方便理解的公式。将Tc2j_pcb( min)移动到Data Arrival Time中,但是保证Setup Time Slack不变。

Data Arrival Time=Launch Edge+Tc2i_pcb( max)+Tco( max)+Td_pcb( max)+Tpin2reg(max)-Tc2j_pcb( min)

Data Required Time=Latch Edge+Tc2j_fp(min)-Tsu-Clock Uncertainty Time

书中介绍这样FPGA的外部所有延时信息都集中在Data Arrival Time里面,就是set_input_delay-max要约束的值

set_input_delay(max)=Tc2i_pcb( max)+Tco( max)+Td_pcb( max)-Tc2j_pcb( min)

(对这个解释目前还是没有很明白,为什么要这样变换,主要是如何理解输入延时,时序约束是为了告诉FPGA时钟和数据的相位关系,从而让FPGA能够正确接收,在上面将FPGA的所有外部延时计算到一个公式中,告诉FPGA数据到达相对时钟的延时情况,这样FPGA就会对Tpin2reg的走线进行优化)

同理,计算保持时间余量;

Data Arrival Time=Launch Edge+Tc2i_pcb( min)+Tco(min)+Td_pcb(min)+Tpin2reg(min)-Tc2j_pcb( max)

Data Required Time=Latch Edge+Tc2j_fp(max)+Th+Clock Uncertainty Time

set_input_delay(min)=Tc2i_pcb(min)+Tco(min)+Td_pcb(min)-Tc2j_pcb(max)

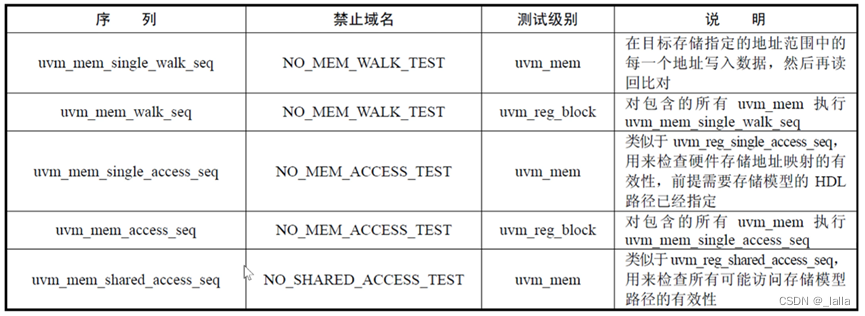

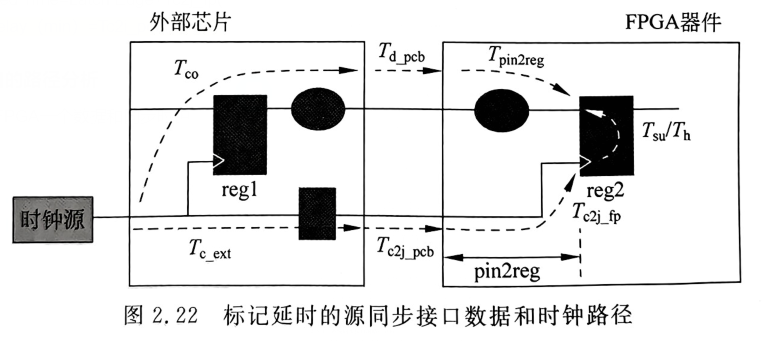

源同步接口的路径分析(引脚到寄存器)

外部芯片给FPGA一个数据和同步时钟

通常,在外部芯片中我们可以找到Tco的值,外部芯片的时钟启动沿到外部芯片数据输出引脚的延时时间。外部芯片的时钟走线延时Tc_ext已经包含在Tco里了,所以可以认为它的取值是0。

推导出建立时间余量公式:(这里和上面一样,对公式Tc2j_pcb进行了变换)

Data Arrival Time=Launch Edge+Tco( max)+Td_pcb ( max)十Tpin2reg ( max)-Tc2j_pcb(min)

Data Required Time=Latch Edge+Tc2j_fp( min)-Tsu-Clock Uncertainty Time

set_input_delay(max)=Tco( max)+Td_pcb( max)-Tc2j_pcb( min)

保持时间余量公式:

==Data Arrival Time=Launch Edge+Tco(min)+Td_pcb(min)+Tpin2reg(min)-Tc2j_pcb( max)

Data Required Time=Latch Edge+Tc2j_fp(max)+Th+Clock Uncertainty Time

set_input_delay(min)=Tco(min)+Td_pcb(min)-Tc2j_pcb(max)

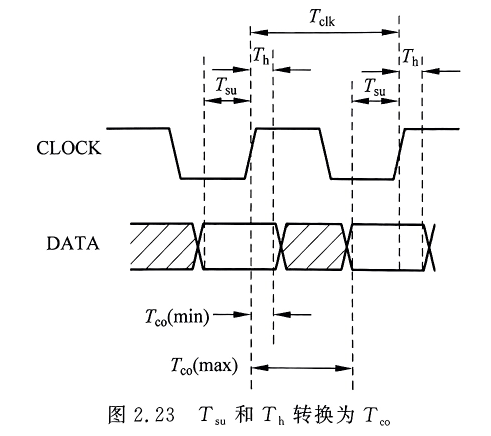

如果手册中没有Tco的最大最小值,可以根据建立时间和保持时间自己计算:

Tco(max)=Tclk-Tsu

Tco(min)=Th

Set output delay

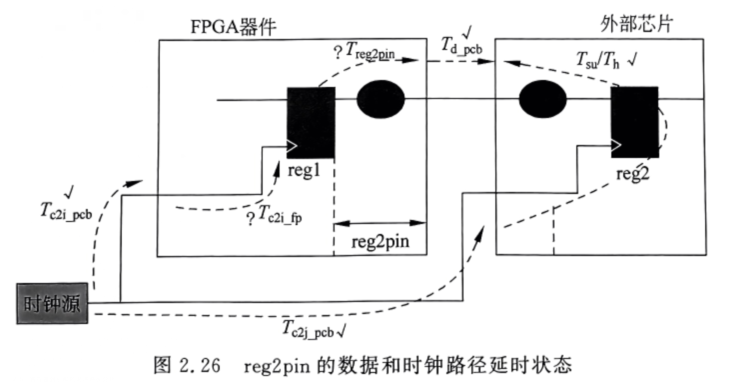

系统同步接口路径分析(寄存器到引脚)

这里的FPGA的引脚是用作输出,目的寄存器是在外部芯片中

- Tc2i_pcb表示时钟信号从时钟源到FPGA输人引脚所经过的PCB走线延时。

- Tc2i_fp表示时钟信号从FPGA输人引脚到其内部的源寄存器regl所经过的时钟网络延时。

- Treg2pin则是数据信号从FPGA器件的源寄存器到其输出引脚的延时,也就是reg2pin实际要约束的路径延时。

- Td_pcb是数据信号在PCB上的走线延时。

- Tc2j_pcb表示时钟信号从时钟源到达外部芯片引脚所经过的PCB走线延时。

- Tsu表示外部芯片(通常包括目的寄存器和外部芯片中所有相关的路径延时信息)的建立时间。

- Th表示外部芯片(通常包括目的寄存器和外部芯片中所有相关的路径延时信息)的保持时间。

建立时间余量:

Data Arrival Time=Launch Edge+Tc2i_pcb( max)+Tc2i_fp( max)+Treg2pin( max)+Td_pcb( max)

Data Required Time=Latch Edge+Tc2j_pcb( min)-Tsu

Setup Time Slack=Data Required Time- Data Arrival Time

保持时间余量;

Data Arrival Time=Launch Edge+Tc2i_pcb( min)+Tc2i_fp(min)+Treg2pin( min)+Td_pcb (min)

Data Required Time=Latch Edge+Tc2j_pcb( max)+Tn

Hold Time Slack=Data Arrival Time-Data Required Time

和之前分析的一样,Tc2i_fp还是忽略掉,用set_output_delay约束Treg2pin。

还是要变换公式,要把FPGA的外部延时综合在一起,其他的延时编译器都是知道的,变到Data Required Time中

set_output_delay(max)=Tc2i_pcb( max)-Tc2j_pcb(min)+Td_pcb(max)+Tsu

set_output_delay(min)=Tc2i_pcb(min)-Tc2j_pcb(max)+Td_pcb(min)-Th

(这里有点混乱,公式为什么要这么变也没有解释)

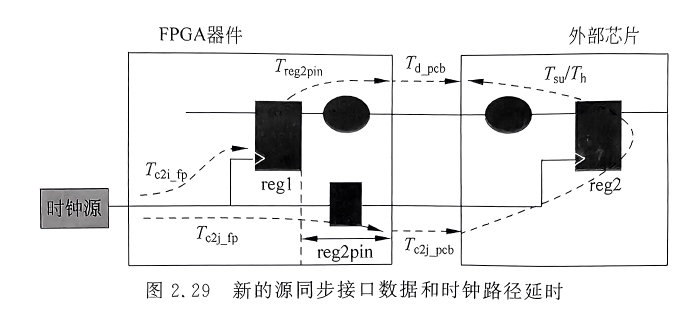

源同步接口路径分析(寄存器到引脚)

推导出建立时间余量公式:

Data Arrival Time=Launch Edge+Tc2i_fp( max)+Td_pcb ( max)+Treg2pin ( max)

Data Required Time=Latch Edge+Tc2j_pcb+Tc2j_fp( min)-Tsu-Clock Uncertainty Time

==

保持时间余量公式:

Data Arrival Time=Launch Edge+Tc2i_fp(min)+Td_pcb(min)+Treg2pin(min)

Data Required Time=Latch Edge+Tc2j_fp(max)+Tc2j_pcb+Th+Clock Uncertainty Time

对公式变换得到:

set_output_delay( max)=Td_pcb ( max)+Tsu-Tc2j_pcb(min)

set_output_delay( min)=Td_pcb (min)-Th-Tc2j_pcb(max)

总结下来,set_input_delay和 set_output_delay 的约束值计算公式,都是将时序路径中所有FPGA器件外部的延时信息汇总在一起,告诉FPGA编译工具,使其引导布局布线,以保证其内部的延时能够满足系统(FPGA器件和外部芯片)的时序要求。

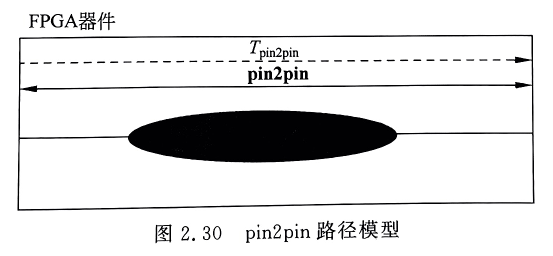

引脚到引脚(set min/max delay)

pin2pin即 FPGA外部信号从 FPGA的输入引脚到输出引脚所经过的整个路径延时。

整个路径延时基本上只是一些组合逻辑延时和走线延时。没有所谓的建立时间和保持时间,只需要set_max_delay或set_min_delay这两条约束命令分别指定某个输入引脚到某个输出引脚的最大或最小延时值。至于这个最大或最小延时值如何确定,取决于实际的应用,没有什么通用公式可以套用。