平台:vivado21018.3

芯片:xcku115-flva1517-2-i (active)

本文官方文档:Xilinx_Answer_64761_Ultrascale_Devices

本文驱动下载地址:64761 - Bitstream Loading across the PCI Express Link in UltraScale and UltraScale+ Devices for Tandem PCIe and Partial Reconfiguration (xilinx.com)

本文参考:Xilinx基于PCIE的部分重配置实现(一) | 电子创新网赛灵思中文社区 (eetrend.com)

要使用PCIE实现FPGA的部分可重构,就要理解为什么要使用PCIE来重构FPGA内部的电路。PCIE是一种即插即用的协议,这个就意味着在通电状态下,PCIE主机将枚举系统。这个过程包括主机从每个设备读取请求的地址大小,然后为该设备分配一个基本地址。因此在在主机查询PCIE接口时,必须要准备好它们,否则它们将不会被分配一个基本地址。

另外,PCIE规范规定,系统上电后,复位信号必须在100毫秒内取消断言,并且PCIE端口必须在复位信号取消断言后不超过20毫秒准备好进行链路训练。通常被称为100毫秒的启动时间要求。

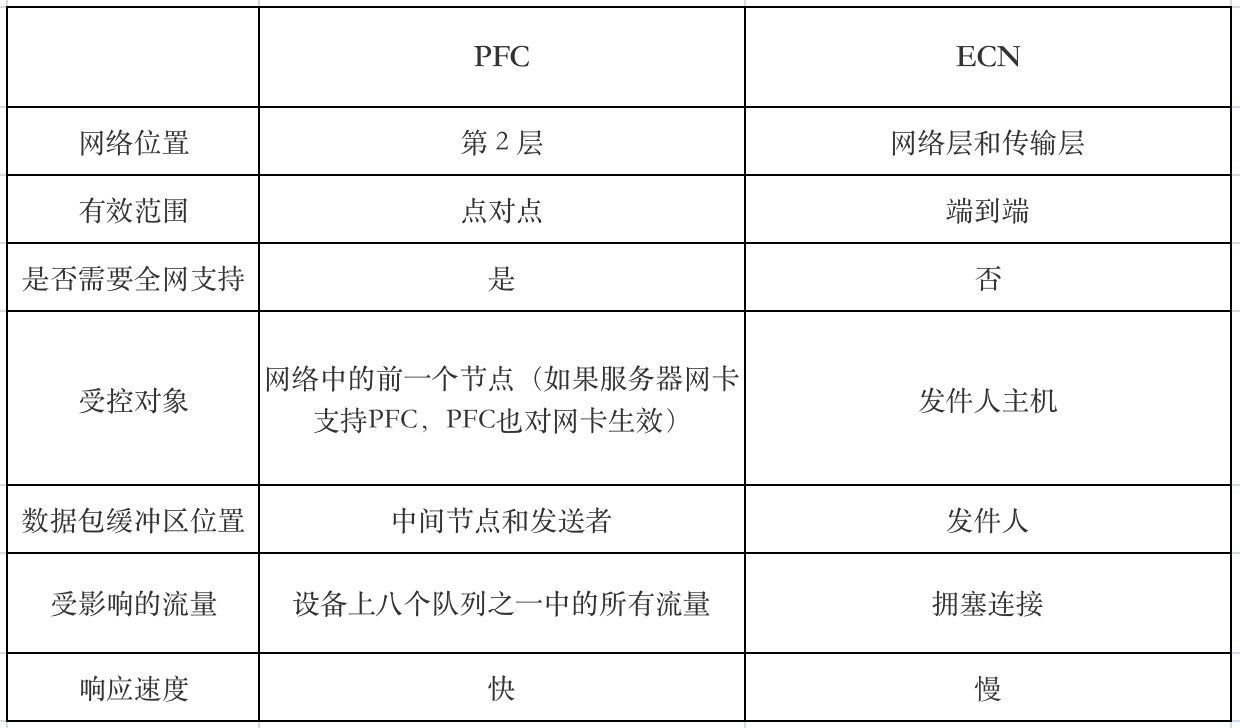

Tandem Configuration(串联配置)采用两阶段方法,使IP能够满足PCI Express规范中指定的配置时间要求。该技术支持多种用例:

| Tandem PROM | 从闪存中加载单个两级位流。 |

| Tandem PCIe | 从闪存中加载第一阶段比特流,并通过 PCIe 链路将第二阶段比特流传递到 MCAP。 |

| Tandem with Field Updates | 在Tandem PROM或Tandem PCIe的初始配置之后,保持PCIe链接处于活动状态,更新整个用户设计。更新区域(平面图)和设计结构是预定义的,并提供了Tcl脚本。 |

| Tandem + Partial Reconfiguration | 这是Tandem配置后跟随任何大小或数量的部分重构(PR)的更一般情况。 |

| Partial Reconfiguration over PCIe(PR over PCIe) | 这是PR通常遵循的标准配置,使用PCIe / MCAP作为部分比特流的传递路径。 |

下面我们将采用PR over PCIe模式,通过PCIe的PR启用MCAP链路进行部分重新配置。

对于FPGA的配置方式可以使用JTAG、ICAP和MCAP来配置FPGA。它们具有一下区别:

| JTAG | 使用JTAG线对FPGA进行烧录配置。需要繁琐的烧录线。 |

| ICAP | 使用FPGA的内部配置接口,通过FPGA内部逻辑电路实现对FPGA的配置。 |

| MCAP | 主机通过PCIE接口向FPGA发送配置文件,从而实现对FPGA的烧写。 |

使用MCAP技术对FPGA进行重配置,可以在保证系统不用重新枚举PCI设备的前提下对FPGA某个动态区域进行逻辑修改。

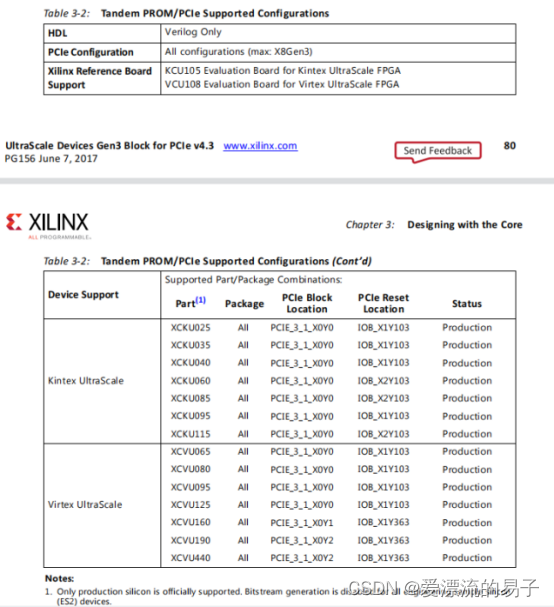

支持的设备,这种配置方式目前只支持UltraScale系列器件。

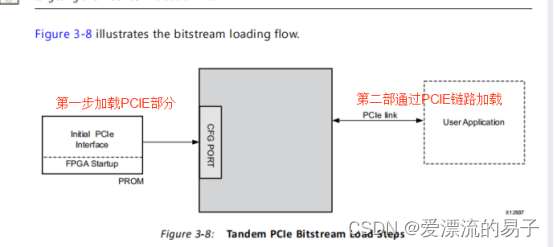

关于Tandem PROM和Tandem PCIe这两个设计的区别。

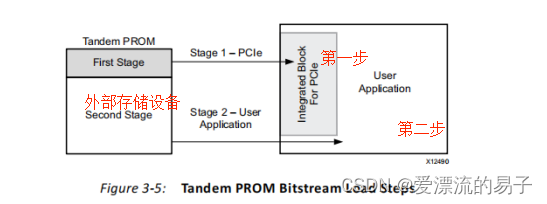

Tandem PROM解决方案将比特流分为两个部分,并将这两个部分都从本地配置存储器(PROM或者其他存储器)加载。bit流的第一部分配置设计的PCIE部分,第二部分配置FPGA的其余部分。

Tandem PCI解决方案与Tandem PROM类似。在第一阶段,只有与PCIe操作相关的配置存储单元从PROM里面加载。加载完第一阶段比特流后,PCIe端口能够被系统枚举。随后第二阶段的比特流通过PCIe链路传输。

下面使用FPGA使用PCIE实现FPGA的部分重配置。

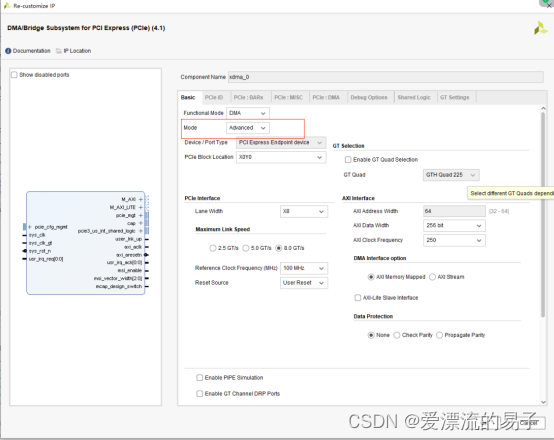

选择mode模式为:Advanced

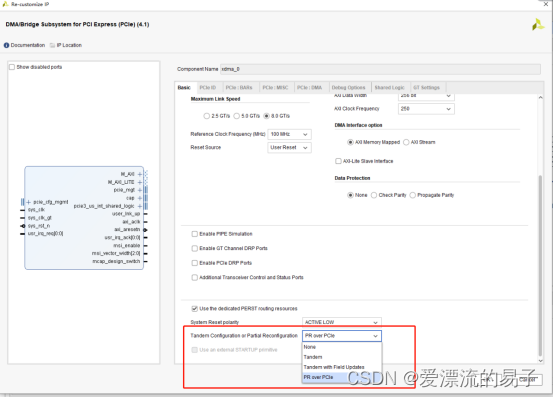

Tandem Configuration or Partial Reconfiguration下选择PR over PCIe

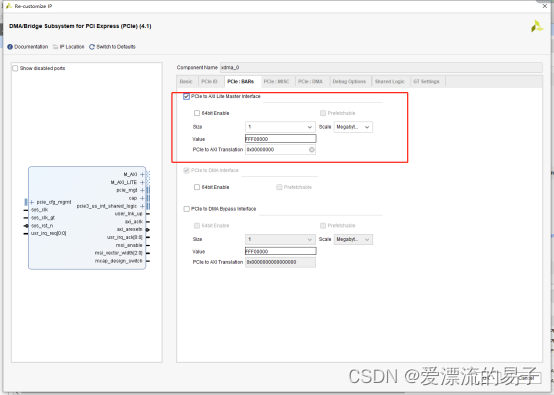

使用AXI_LITE接口来完成对寄存器的读写。

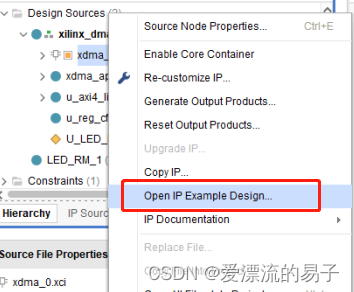

其他配置默认,新建完成XDMA的IP后,打开example project。

打开实例工程后

添加自定义的AXI_LITE接口转换模块、寄存器模块、以及LED_RM_0、LED_RM_1模块。

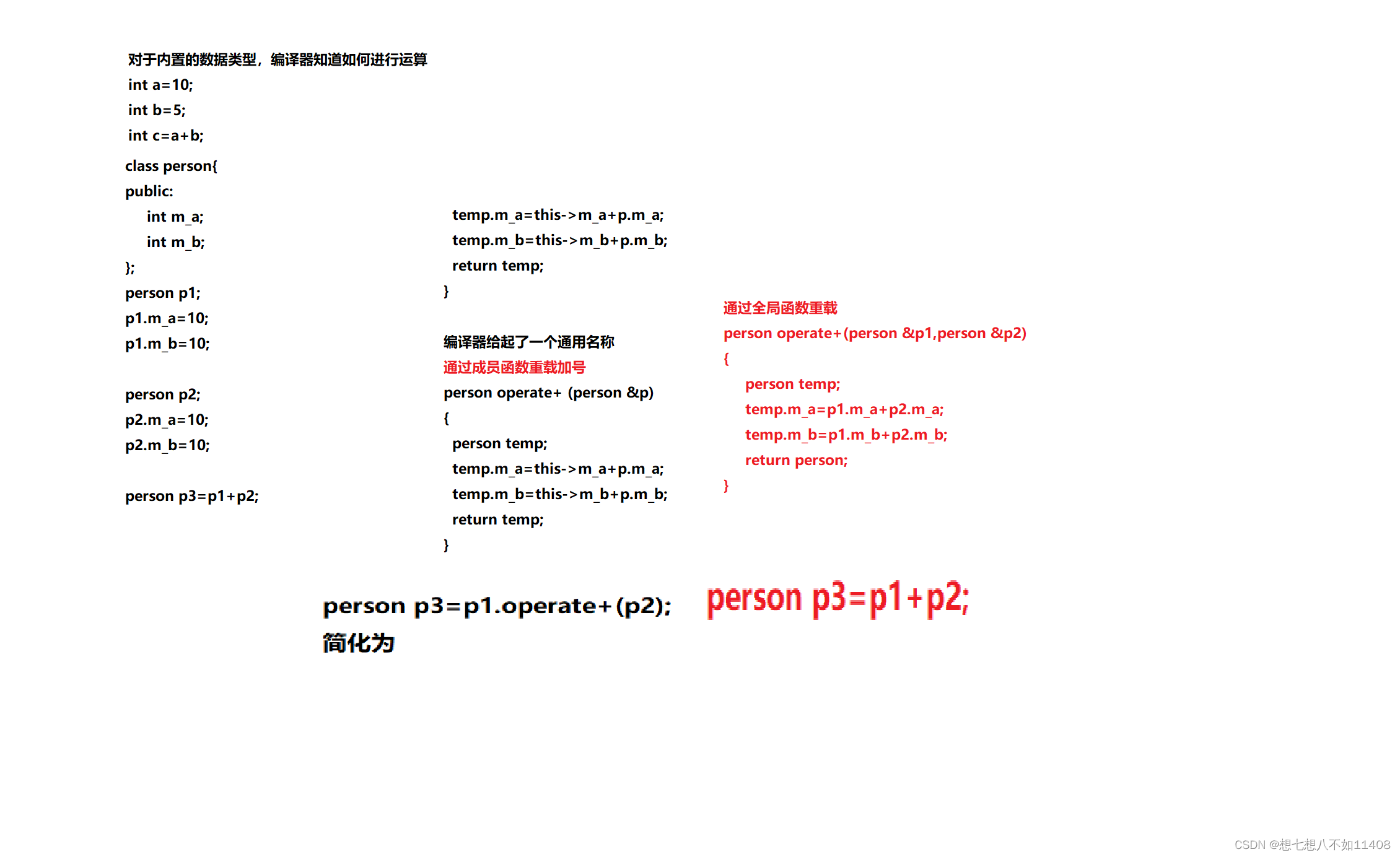

LED_RM_0模块功能输出LED参数为2’b00。

// *********************************************************************************/

// Project Name :

// Author : i_huyi

// Email : i_huyi@qq.com

// Creat Time : 2023/4/20 9:18:02

// File Name : .v

// Module Name :

// Called By :

// Abstract :

//

// CopyRight(c) 2020, xxx xxx xxx Co., Ltd..

// All Rights Reserved

//

// *********************************************************************************/

// Modification History:

// 1. initial

// *********************************************************************************/

// *************************

// MODULE DEFINITION

// *************************

`timescale 1 ns / 1 ps

module LED_RM_0#(

parameter U_DLY = 1

)

(

input wire sys_clk ,

input wire rst_n ,

output reg [1:0] led

);

//--------------------------------------

// localparam

//--------------------------------------

//--------------------------------------

// register

//--------------------------------------

//--------------------------------------

// wire

//--------------------------------------

//--------------------------------------

// assign

//--------------------------------------

//------------------------------------------------------------

//------------------------------------------------------------

//------------------------------------------------------------

//------------------------------------------------------------

always @ (posedge sys_clk or negedge rst_n)

begin

if(rst_n == 1'b0)

led <= 2'b0;

else

led <= 2'b0;

end

//------------------------------------------------------------

//------------------------------------------------------------

endmodule

LED_RM_1模块功能输出LED参数为2’b11。

always @ (posedge sys_clk or negedge rst_n)

begin

if(rst_n == 1'b0)

led <= 2'b0;

else

led <= 2'b11;

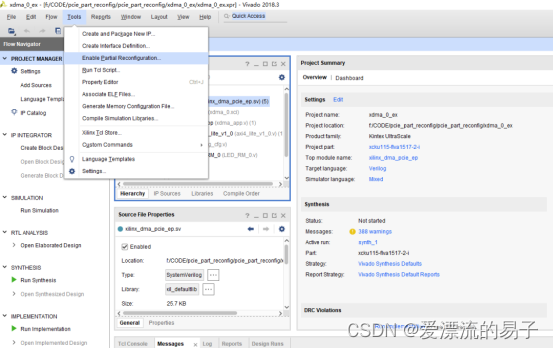

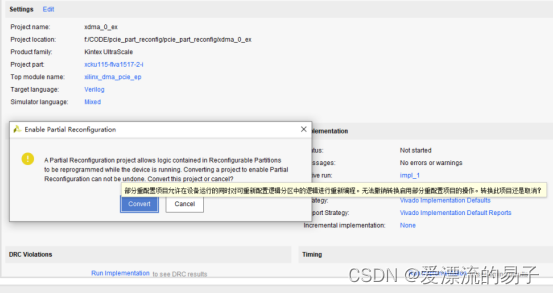

end新建完成后。点击tools-Enable Partial Reconfiguration。

确定启用部分重配置。

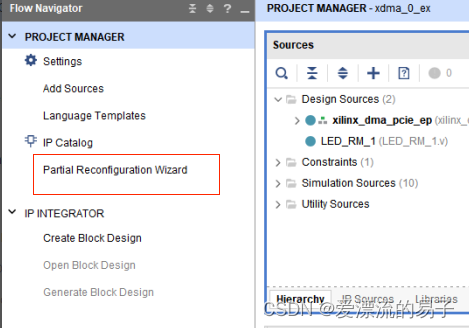

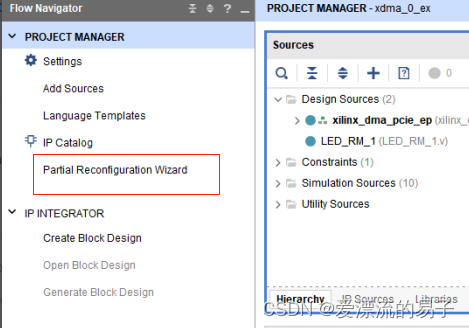

确定后PROJECT MANAGER会多出partial Reconfiguration wizard选项。

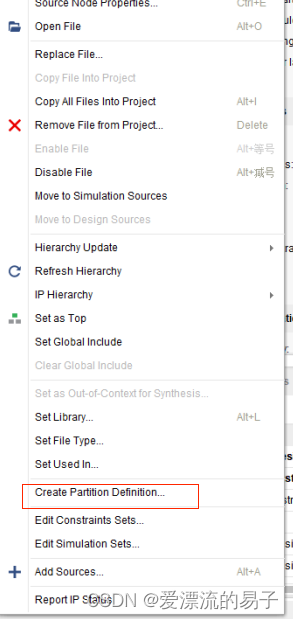

选中你要进行重构的逻辑,即LED_RM_模块。选择Great Partition Definition。

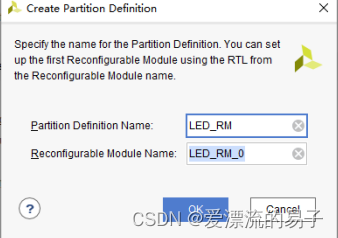

指定一个分区的名字。

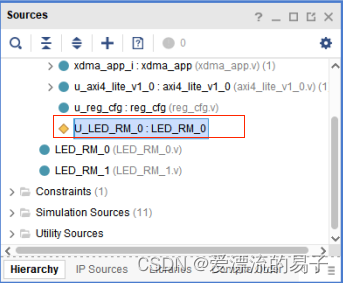

完成后LED_RM_0模块变成了一个棱形的标志。

下面打开partial Reconfiguration wizard

继续

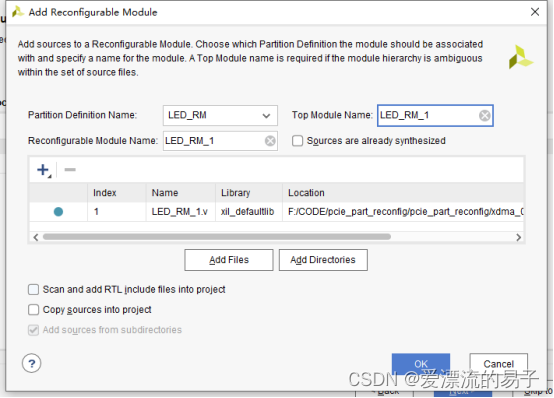

添加模块LED_RM_1。

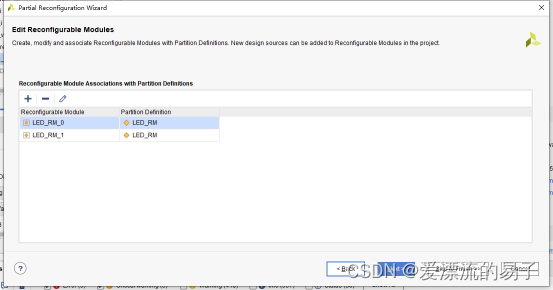

添加完成后,LED_RM分区内有两个模块。

添加完成后,LED_RM分区内有两个模块。

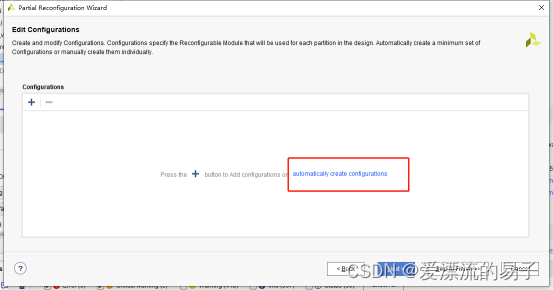

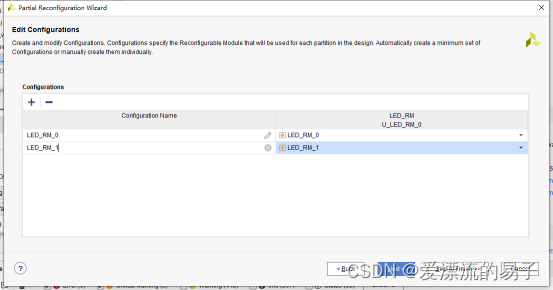

下一步后,继续点击automatically create configurations。

修改Configuration Name。

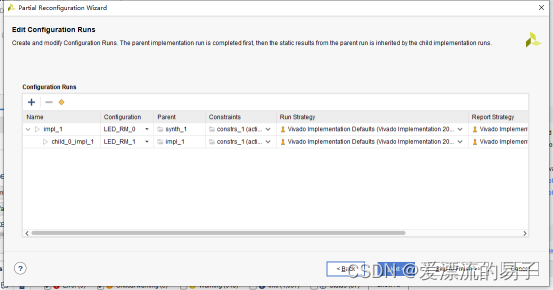

在Edit Configuration Runs下点击automatically create configurations。

完成后进行综合。

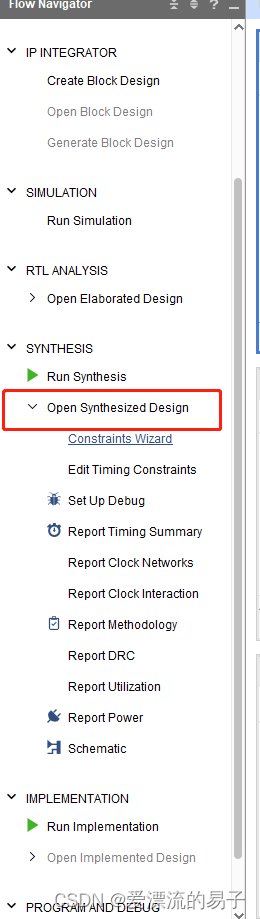

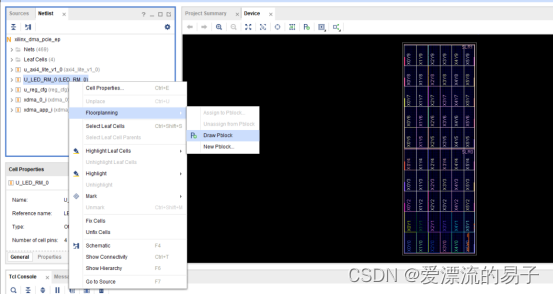

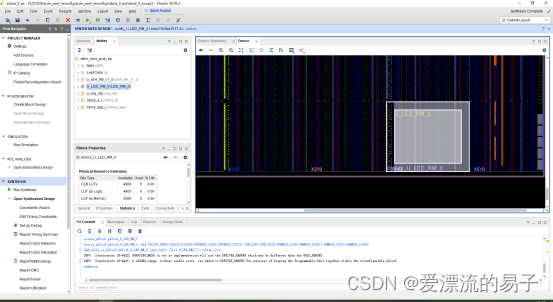

在Vivado中,Floorplanning是一种将设计分配到芯片的不同区域的方法。Pblock是一种在Floorplanning中使用的工具,它允许用户将设计分配到特定的物理区域中。通过使用Pblock,用户可以控制设计中的不同模块的位置和布局,以最大化性能和资源利用率。在Floorplanning中,绘制Pblock是指创建一个物理块,然后将设计中的模块分配到该块中。这样可以更好地控制设计的物理布局,以满足性能和资源利用率的要求。这里我们选中LED_RM_0模块选择Floorplaning - Draw Pblock。

在FPGA上选择一块没有使用的区域,划分该区域为可重构的区域。

修改后会在XDC文件下添加约束信息。

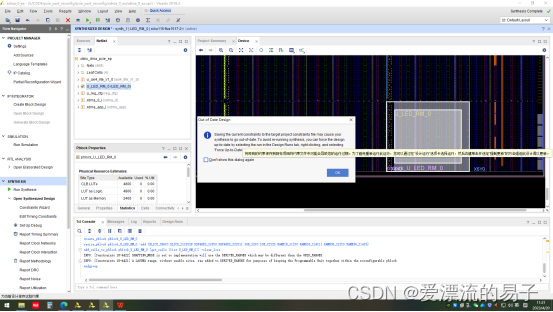

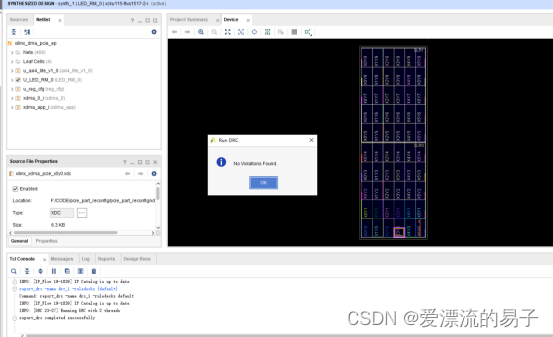

下面我们进行DRC检查看看分配的区域是否合理,不会和其他模块抢占区域。

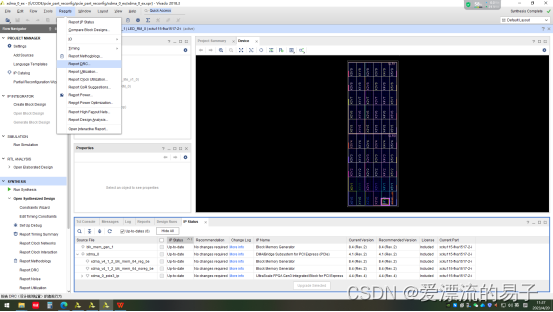

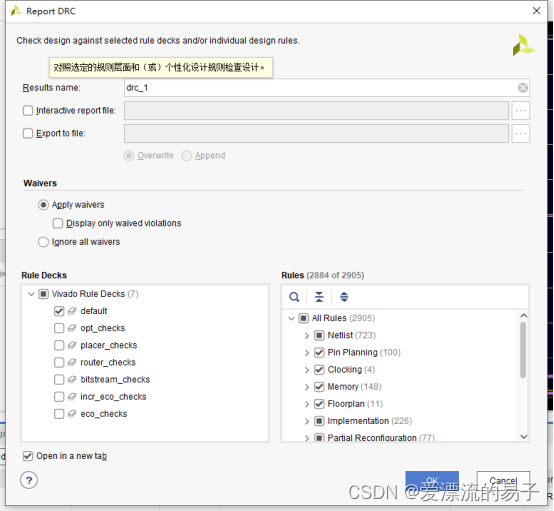

在Vivado中进行DRC检查,可以按照以下步骤操作:

- 打开Vivado软件,打开需要进行DRC检查的工程。

- 在左侧的“Flow Navigator”面板中,选择“Open Implemented Design”选项。

- 在右侧的“Design Runs”面板中,选择“Generate DRC Report”选项,并点击“Run”按钮。

- 等待DRC检查完成后,在“Design Runs”面板中找到生成的DRC报告,并双击打开。

- 在DRC报告中,可以查看所有的DRC错误和警告信息,以及相应的解决方法。

- 如果需要重新运行DRC检查,可以在“Design Runs”面板中选择“Regenerate DRC Report”选项,并点击“Run”按钮。

注意:在进行DRC检查前,需要先进行综合和实现操作,并确保设计没有任何语法错误和警告信息。

无报错。

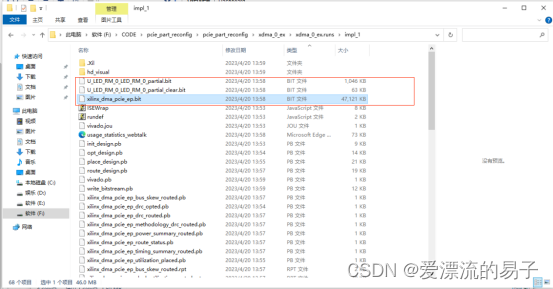

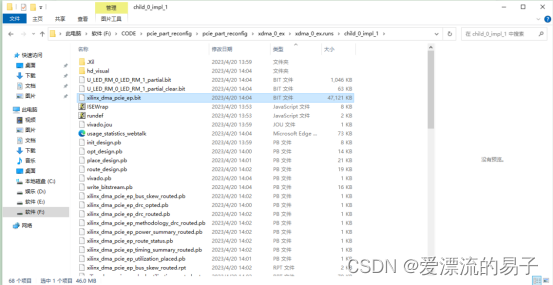

生成bit流。

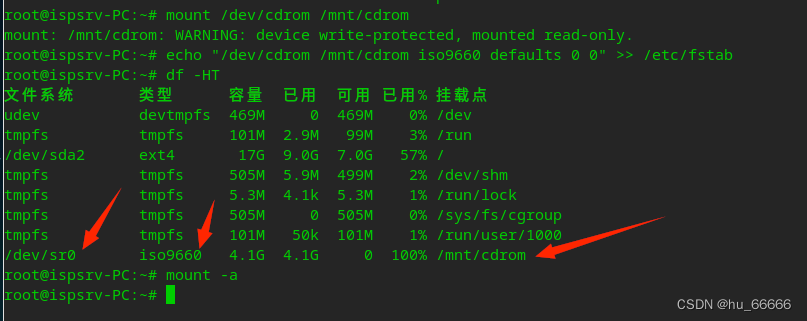

至此,部分重配置的工程就生成完毕,在生成出来的文件里面,在工程目录下会有两个imp的文件夹,里面会分别有静态逻辑和各自的重配置逻辑,我们将静态逻辑先烧写进去FPGA,之后就可以通过PCIE配置动态逻辑,关于MCAP的驱动的上位机,在Xilinx_Answer_64761__UltraScale_Devices这份文档中有详细的说明。

xilinx_dma_pcie_ep.bit:这部分为静态逻辑。

U_LED_RM_0_LED_RM_0_partial.bit:这部分为重配置逻辑。

U_LED_RM_0_LED_RM_0_partial_clear.bit:这部分不清楚。

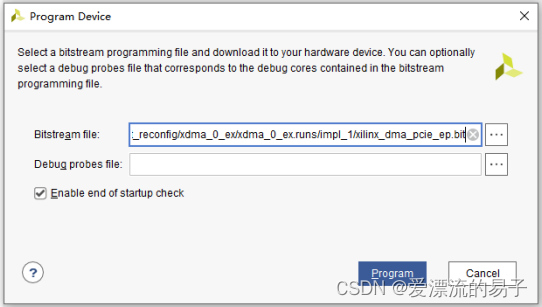

下载bit文件

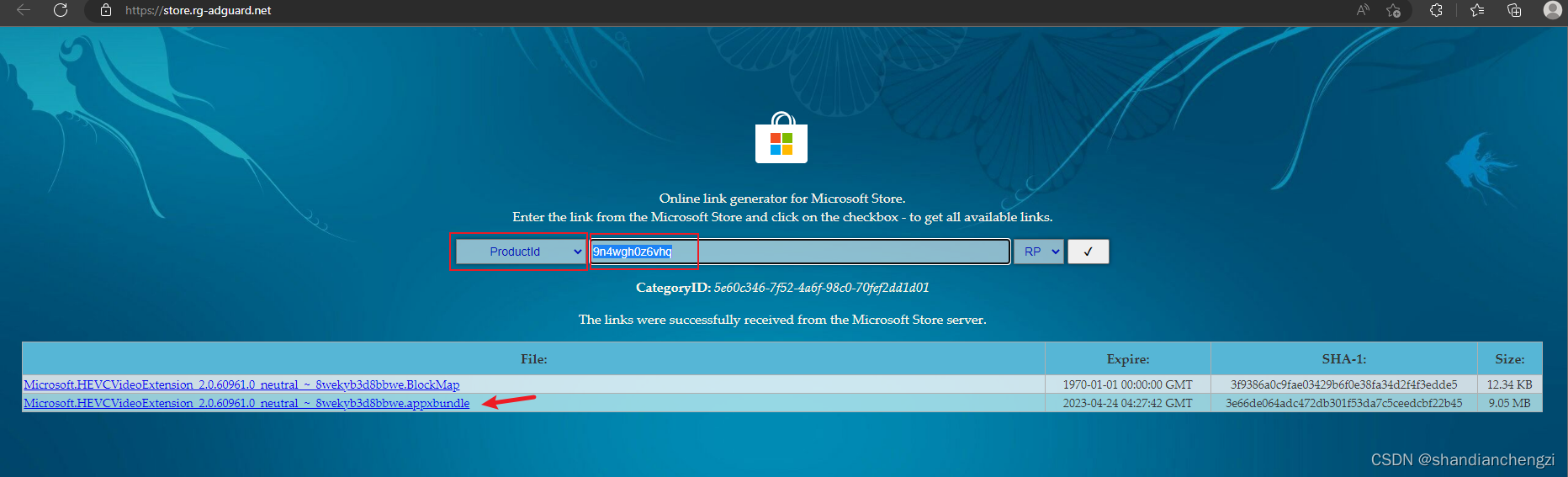

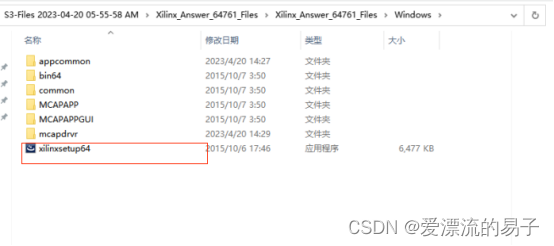

下载Xilinx_Answer_64761_Ultrascale_Devices文件。

安装xilinx提供的驱动。

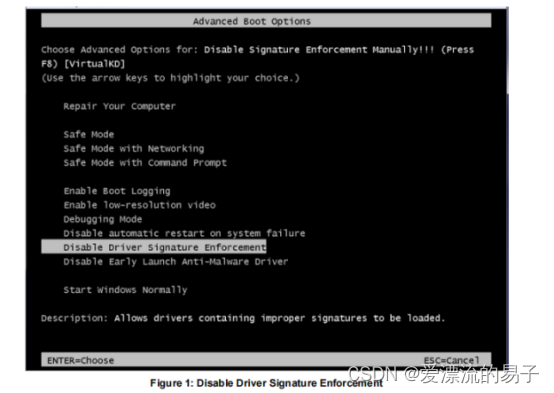

需要注意的是,该驱动目前需要在win764位环境下运行。且需要在启动时强制将驱动签名禁止。设置完成后安装驱动文件。开机按F8,选择强制禁用驱动签名。

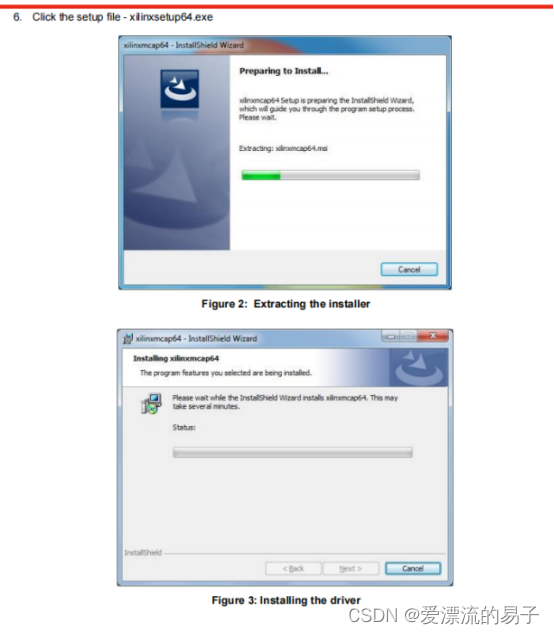

安装驱动。

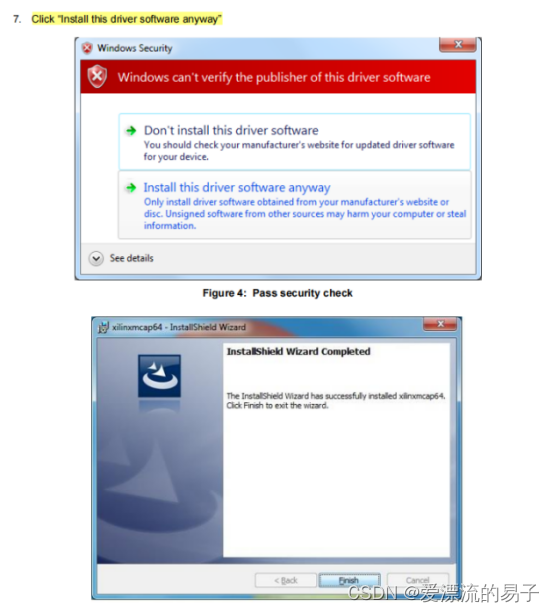

点击始终安装此驱动程序。

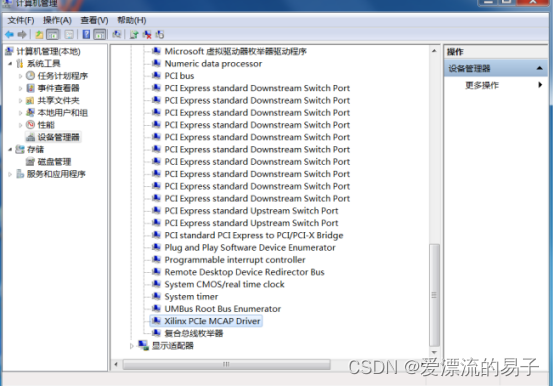

安装完成后发现在设备管理器中的系统设备中找到名字叫做Xilinx Pcle MCAP Driver的驱动。

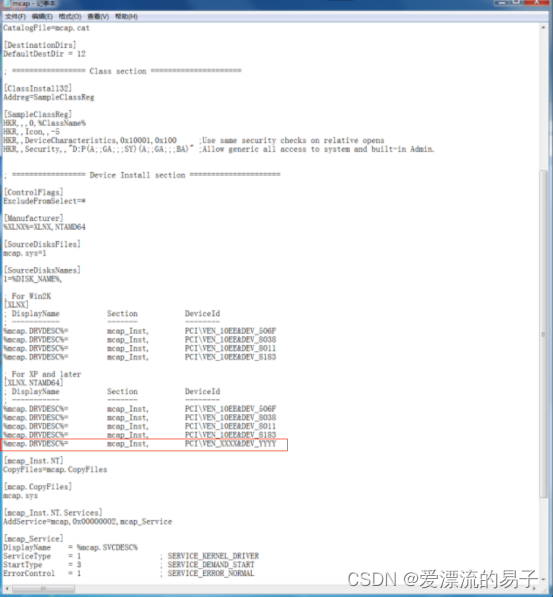

用户可以在驱动安装路径下打开INF文件自由添加你的设备PCIE驱动号。

路径为:C:/Program Files(x86)\Xilinx\MCAP\mcap64

格式为%mcap.DRVDESC%= mcap_Inst, PCI\VEN_xxxx&DEV_YYYY

驱动的使用

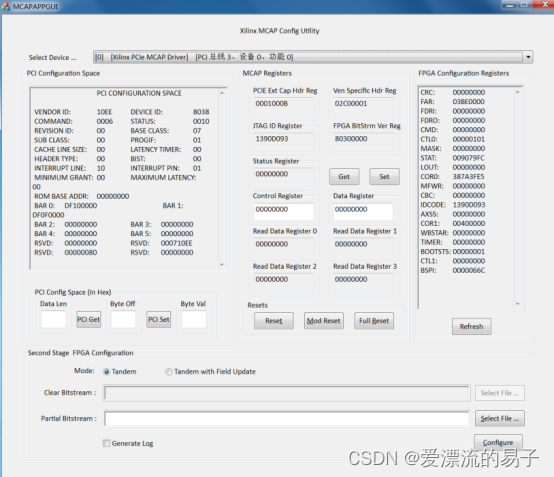

安装后后出现两个快捷方式,一个是MCAPAPP.exe另外一个是MCAPAPPGUI.exe

根据我们代码中。

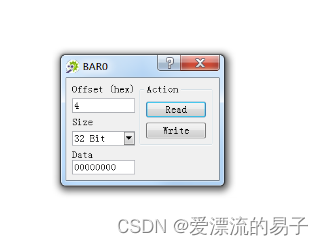

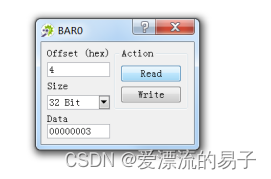

使用LED_RM_0读取PCIE的BAR0地址4读取值为32’h0;

使用LED_RM_1读取PCIE的BAR0地址4读取值为32’h3;

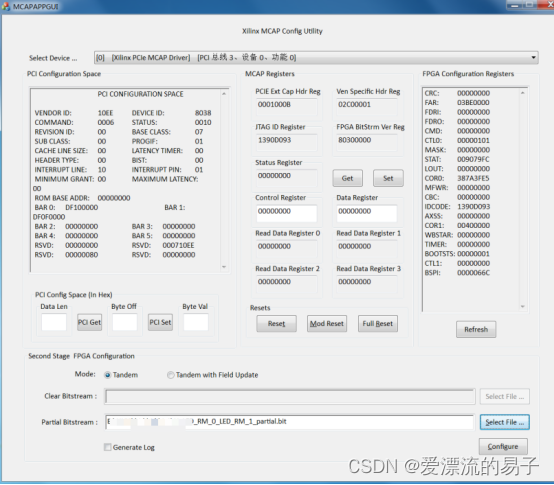

可重构部分未LED_RM_0的时候。

直接启动MCAPAPPGUI.exe,选择重构部分的代码LED_RM_1。

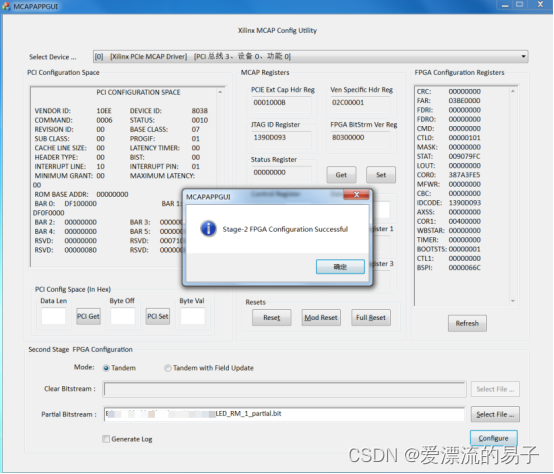

重构成功。

启动windriver读取BAR0地址4的值。

配置成功。