引言

低功耗设计关乎ASIC芯片的性能稳定。对ASIC 特别是一些Soc芯片的设计有着重要的影响,随着集成规模的大幅度增加,芯片自身的功耗问题暴露也越来越明显。低功耗设计的需求和必要性也越来越值得关注。本文就《Low Power Methodology Manual For System-on-Chip Design》 书籍的学习,记录一下低功耗设计的理论知识。

参考

【1】Michael Keating • David Flynn •Robert Aitken Alan G • ibbons • Kaijian Shi. Low Power Methodology Manual For System-on-Chip Design

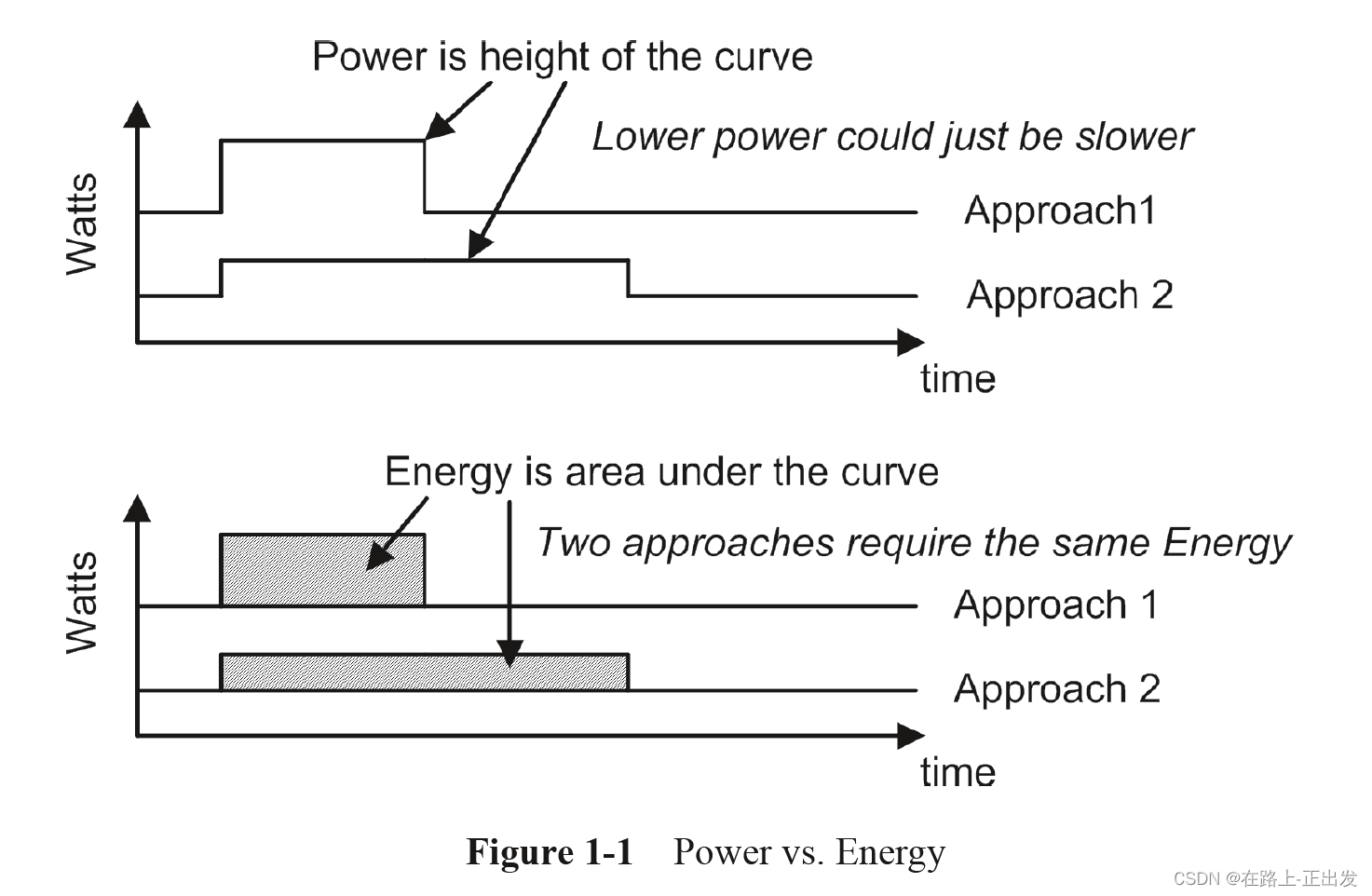

能量 vs 功率

书中给出了这个典型的对比图,能量是功率对时间的积分,那么对于相同容量的电池而言,平均功耗更低的芯片,续航时间更久。这个道理应该很好理解。

动态功耗

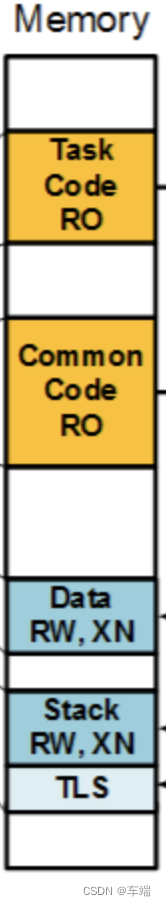

Soc芯片的总功耗包括动态功耗和静态功耗。动态功耗指的是芯片处于活跃状态,即片内信号变化所耗的功率。静态功耗则相反,指设备上电但是,没有信号变化所耗的功率。在CMOS设备中,静态功耗由泄漏电流带来。

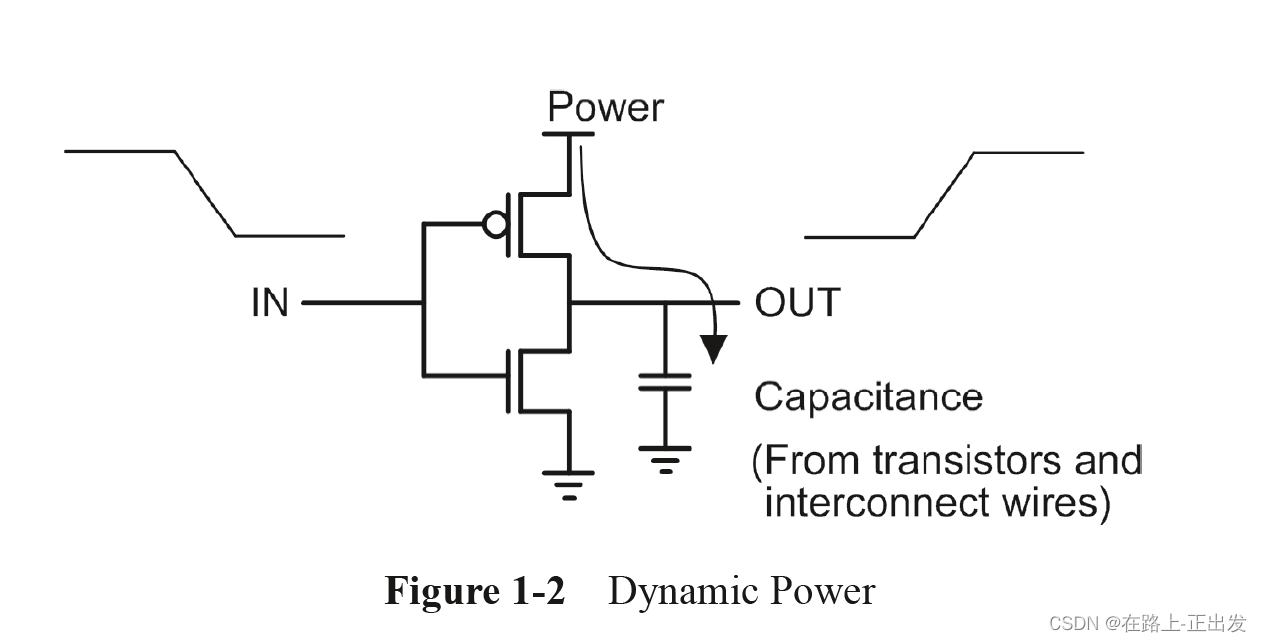

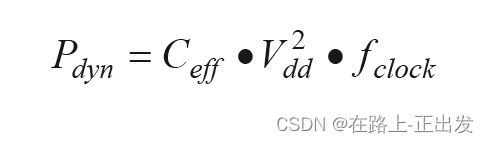

动态功耗的首要并且主要的源头是开关功耗——对栅极上的输出电容进行充电和放电所需的功率。如下图所示:

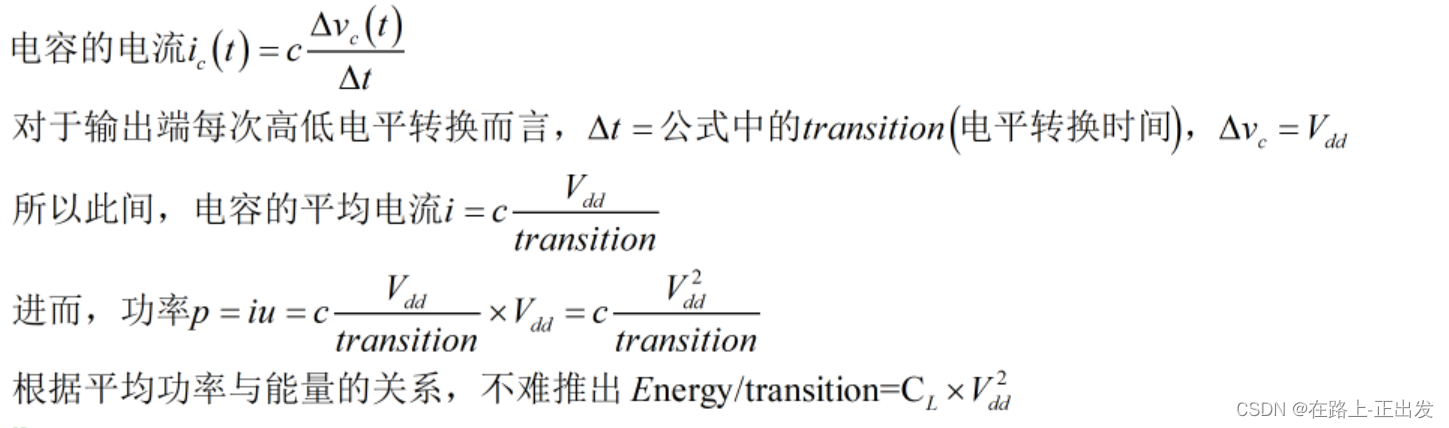

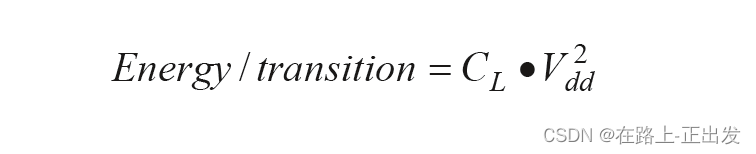

每次输出的高低电平转换对应的能量耗散,式中,CL 是负载电容,Vdd 是供电电压:

有人看到这个式子,可能是不知道咋来的,这里做一些我个人的解释:

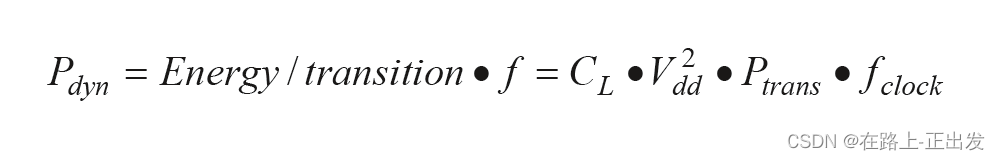

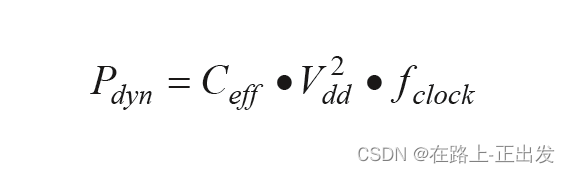

动态功耗的计算公式:

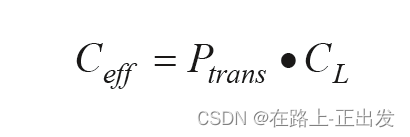

式中,f 为电平转换频率,即1秒内高低电平的翻转次数,Ptrans 表示输出端的电平翻转概率。fclock 是系统时钟频率。定义:

那么就可以用另一个相似的表达式描述动态功耗:

注意,开关功耗并不是晶体管尺寸的函数,而是开关频率和负载电容的函数。因此,动态功耗具有数据依赖性。

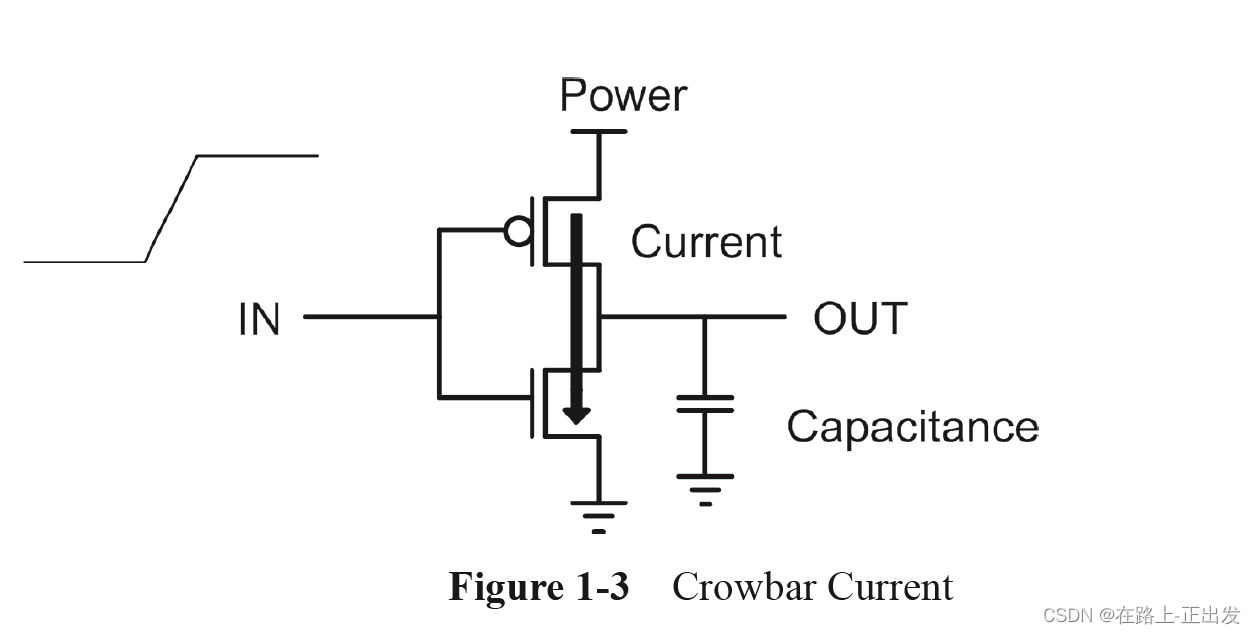

除了开关功耗,内部功耗也是动态功耗的一部分。下图显示了是晶体管内部的开关电流。内部功耗包括NMOS和PMOS晶体管导通时发生的短路电流,以及为电池的内部电容充电所需的电流。

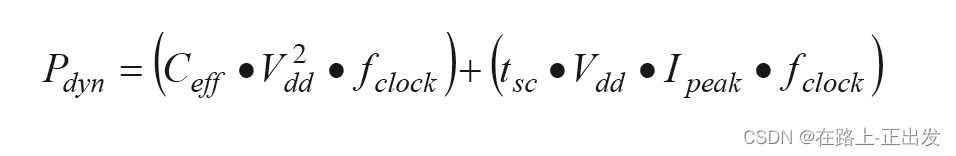

加上内部功耗后,动态功耗的表达式:

tsc 是短路电流持续的时间。Ipeak 是总的内部开关电流(短路电流 + 给内部电容充电所需的电流)。

只要输入信号的斜坡时间保持较短,短路电流在每次转换期间只发生很短的时间,并且整个动态功率由开关功率主导。出于这个原因,我们经常简化开关功率公式的使用:

但在某些情况下,短路电流(通常称为撬棍电流)是令人感兴趣的。特别是,当我们讨论如何处理功率门控模块的浮动输出时,我们将讨论防止过多撬棒电流的方法。

在体系结构、逻辑设计和电路设计方面有许多技术可以降低在给定技术中实现的特定功能的功率。

这些技术专注于方程的电压和频率分量,以及减少依赖于数据的开关活动。

由于功率对电压的二次依赖性,降低电源电压是降低动态功率的一种高度杠杆化的方式。但是,由于栅极的速度随着电源电压的降低而降低,因此这种方法需要小心进行。

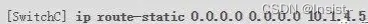

SoC设计者可以通过以下几种方式利用这种方法:

•对于不需要运行特别快的块,如外围设备,我们可以使用比其他块更低的电压供电。这种方法被称为多电压。

•对于处理器,我们可以提供可变电源电压;在需要峰值性能的任务中,我们可以提供高电源电压和相应的高时钟频率。对于需要较低性能的任务,我们可以提供较低的电压和较慢的时钟。这种方法被称为电压缩放。

另一种降低动态功率的方法是时钟门控。将频率驱动到零将功率驱动到零。在许多SoC设计中使用了某种形式的时钟门控。

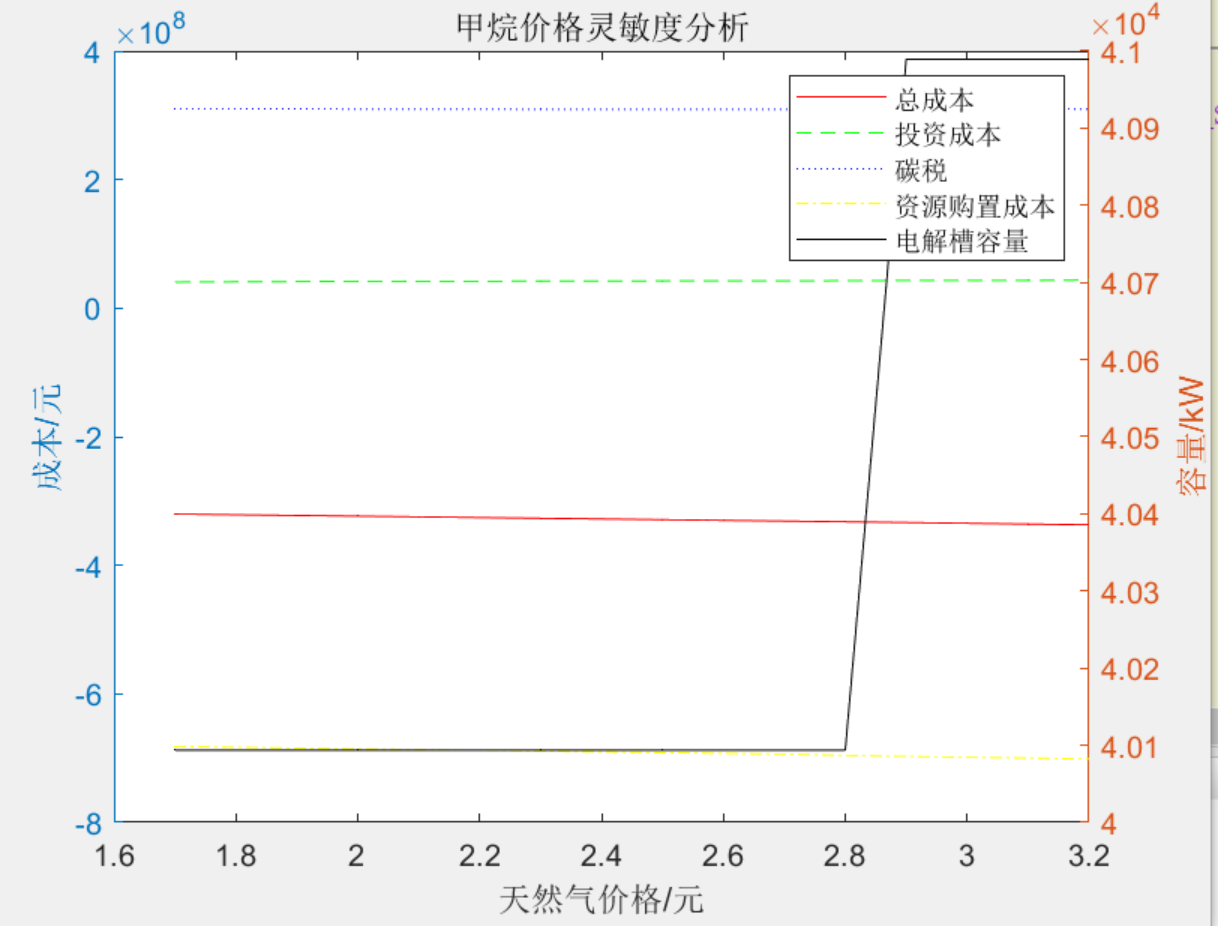

动态功耗与静态功耗的冲突

降低动态功率的最有效方法是降低电源电压。在过去的十五年里,随着半导体技术的发展,VDD已从5V降至3.3V,从2.5V降至1.2V。ITRS路线图预测,2008年和2009年,高性能器件将使用1.0V,低功率器件将使用0.8V。

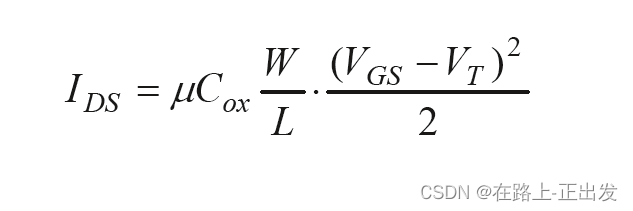

降低VDD的问题在于,它往往会降低IDS,即晶体管的导通或驱动电流,从而导致速度变慢。如果我们忽略速度饱和和90nm以下发生的一些其他细微影响,MOSFET的IDS可以近似为:

其中μ是载流子迁移率,Cox是栅极电容,VT是阈值电压,VGS是栅极-源极电压。由此可见,为了保持良好的性能,我们需要在降低VDD(以及VGS)的同时降低VT。然而,降低阈值电压(VT)会导致亚阈值泄漏电流(ISUB)呈指数级增加。

因此存在冲突。为了降低动态功率,我们降低了VDD;为了保持性能,我们降低了VT;但结果是我们增加了漏电流。到目前为止,这是一个合理的过程,因为泄漏电流产生的静态功率远低于动态功率。但随着90nm技术的发展,我们已经到了静态功率和动态功率一样大的问题的地步,我们需要更仔细地审视这一冲突。

静态功耗

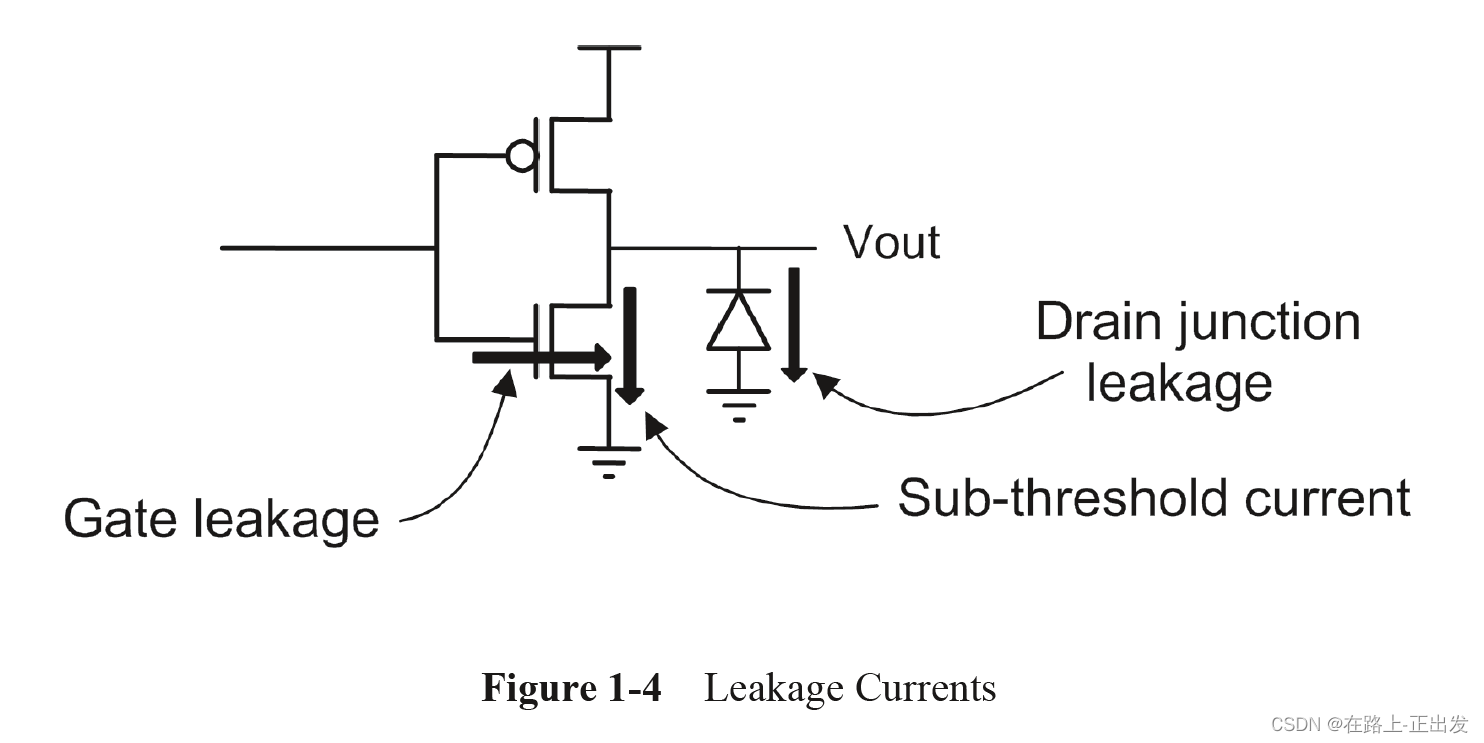

CMOS栅极中有四个主要的漏电流源

•亚阈值泄漏(ISUB):从漏极流向

在弱反转区域中操作的晶体管的源极电流。

•栅极泄漏(IGATE):由于栅极氧化物隧穿和热载流子注入,直接从栅极通过氧化物流到衬底的电流。

•栅极感应漏极泄漏(IGIDL):由高VDG引起的MOSFET漏极中的高场效应引起的从漏极流向衬底的电流。

•反向偏置结泄漏(IREV):由少数载流子漂移和耗尽区中电子/空穴对的产生引起。

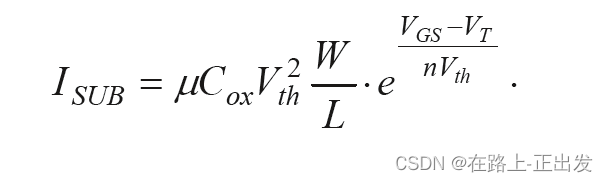

当CMOS门未完全关闭时,会发生亚阈值泄漏。近似而言,其值:

其中W和L是晶体管的尺寸,Vth是热电压kT/q(室温下为25.9mV)。参数n是器件制造工艺的函数,并且在1.0到2.5的范围内。

这个方程告诉我们,亚阈值泄漏以指数形式取决于VGS和VT之间的差异。因此,当我们缩小VDD和VT(以限制动态功率)时,泄漏功率以指数形式恶化。

栅极泄漏是通过栅极氧化物的隧穿电流的结果。栅极氧化物厚度(TOX)在90nm栅极中只有几个原子厚,这是如此之薄以至于隧穿电流可以变得很大。在以前的技术节点中,漏电流主要由亚阈值泄漏控制。但从90nm开始,栅极泄漏可能是亚阈值泄漏的近1/3。在65nm中,在某些情况下,它可以等于亚阈值泄漏。在未来的节点上,将需要高k电介质材料来控制栅极泄漏。这似乎是减少栅极泄漏的唯一有效方法。

亚阈值泄漏电流随温度呈指数级增加。这使得设计低功率系统的问题变得非常复杂。即使在室温下的泄漏是可以接受的,在最坏的情况下,它也可能超过芯片的设计目标。

有几种方法可以最大限度地减少泄漏电流。

一种技术被称为多VT:在性能目标允许的地方使用高VT单元,在必要的地方使用低VT单元以满足时间要求。

第二种技术是在逻辑块不活动时关闭其电源。这种方法被称为功率门控。

这两种方法将在后面的章节中进行更详细的讨论。不过,就目前而言,我们提到了其他三种技术:

VTCMOS晶体管

可变阈值CMOS(VTCMOS)是另一种非常有效的降低待机泄漏功率的方法。通过向衬底施加反向偏置电压,可以降低项(VGS-VT)的值,从而有效地增加VT。这种方法可以将备用泄漏减少多达三个数量级。然而,VTCMOS增加了库的复杂性

需要两个额外的电力网络来分别控制施加到阱的电压。不幸的是,反向体偏置的有效性已被证明随着缩放技术的发展而降低[2]。

叠加效应

当堆叠中的一个以上晶体管被关断时,堆叠效应或自反向偏置可以帮助减少亚阈值泄漏。这主要是因为少量的亚阈值泄漏会导致堆叠晶体管之间的中间节点从电源/接地轨浮起。降低的体源极电势导致略微负的栅极-源极-漏极电压。因此,它减少了项(VGS-VT)的值,有效地增加了VT并减少了亚阈值泄漏。两个晶体管堆叠的泄漏已被证明比单个晶体管的泄漏小一个数量级[3]。这种叠加效应使得逻辑门的泄漏高度依赖于其输入。对于任何多输入电路,都存在最小泄漏状态;理论上,这种状态正好在停止时钟之前应用,以最大限度地减少泄漏。在实践中,在大多数设计中应用这种状态是不可行的。

长通道设备

从亚阈值电流的方程可以清楚地看出,使用非最小长度的通道将减少泄漏。不幸的是,长通道器件具有较低的动态电流,从而降低性能。它们也更大,因此具有更大的栅极电容,这对动态功耗有不利影响,并进一步降低性能。除非长沟道器件的开关活动性低,否则总功耗可能不会降低。因此,在使用长通道设备时,必须考虑切换活动和性能目标。