牛客网Verilog刷题——VL3

- 题目

- 答案

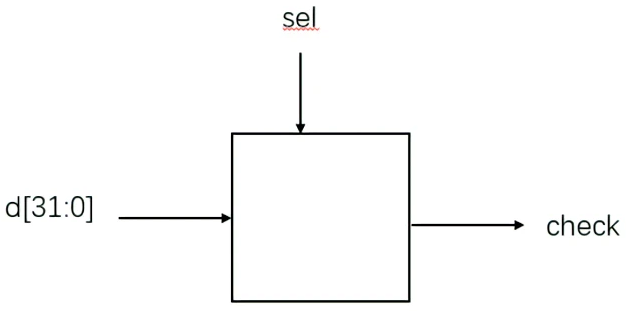

题目

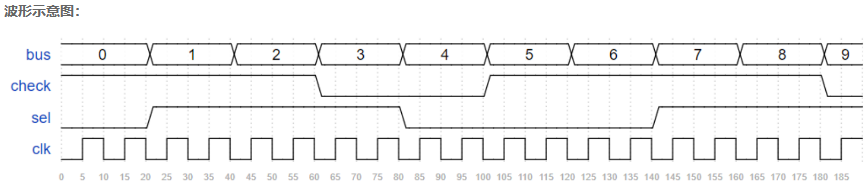

要求设计一个奇偶校验模块,根据sel信号选择进行奇校验还是偶校验(sel=0,进行偶校验;sel=1,进行奇校验),根据输入的32位数据生成1位的奇偶校验位。

奇偶校验位的生成与利用奇偶校验位进行校验的原理如下:

在发送端,根据奇校验还是偶校验来说生成奇偶校验位。

- 奇校验:确保传输的数据(数据位+校验位)中“1”的个数为奇数个。如果数据位中“1”的个数为奇数个,校验位则为0,此时数据位加校验位中“1”的个数还是奇数个;如果数据位中“1”的个数为偶数个,校验位则为1,此时数据位加校验位中“1”的个数变为奇数个。

- 偶校验:确保传输的数据(数据位+校验位)中“1”的个数为偶数个。如果数据位中“1”的个数为奇数个,校验位则为1,此时数据位加校验位中“1”的个数变为偶数个;如果数据位中“1”的个数为偶数个,校验位则为0,此时数据位加校验位中“1”的个数还是奇数个。

而在接收端,计算接收到的数据(数据位+校验位)中“1”的个数是奇数个还是偶数个,来判断接收到的数据是否正确。

- 奇校验:采用奇校验方式,若数据中“1”的个数为奇数个,接收数据正确;若数据中“1”的个数为偶数个,则接收数据有误。

- 偶校验:采用偶校验方式,若数据中“1”的个数为偶数个,接收数据正确;若数据中“1”的个数为奇数个,则接收数据有误。

奇偶校验在很多设计中都有用到,比如串口传输协议中等。奇偶校验只能达到检错的目的,并不能实现纠错。

另外,在数电中,我们学过:奇数个1异或得到1,偶数个1异或得到0,根据该性质,可以用异或运算符实现奇偶校验。

答案

`timescale 1ns/1ns

module odd_sel(

input [31:0] bus,

input sel,

output check

);

//*************code***********//

wire check_temp;

assign check_temp = ^bus;

reg check_t;

always @(*)

if(sel)

check_t <= check_temp;

else

check_t <= ~check_temp;

assign check = check_t;

//*************code***********//

endmodule