FPGA开发是一项非常复杂的工作,需要处理大量的代码、约束和仿真文件。在开发过程中,由于文件数量庞大,很容易导致工程变得混乱不堪。Vivado是Xilinx公司推出的一款FPGA开发工具,能够帮助开发人员处理这种复杂性,提高开发效率。本文将介绍如何清理Vivado工程,并避免缺失必要的文件。

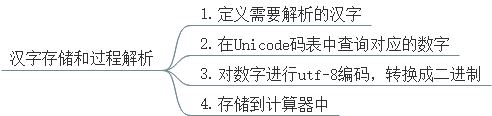

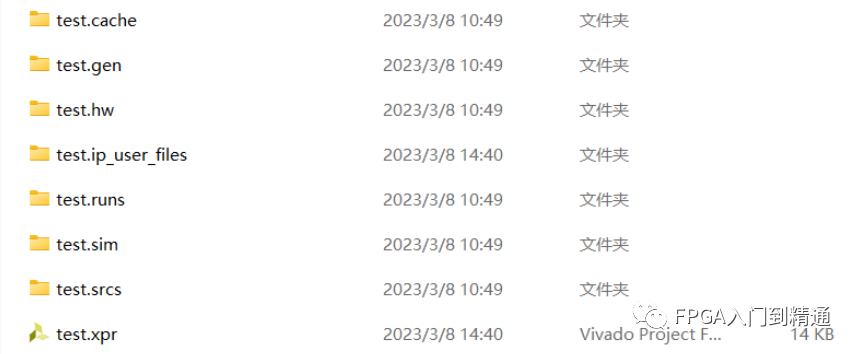

一、vivado工程文件结构

vivado工程文件目录,如下所示:

说明:

-

project_name.cache:Vivado 软件的运行缓存

-

project_name.hw: 所有波形文件

-

project_name.ip_user_files:用户关于 IP 的文件

-

project_name.runs:编译与综合结果 ,impl_1 文件夹存取布线后结果

-

project_name.sdk:SDK 环境代码,一般是 ZYNQ 设计中关于 PS 端的代码

-

project_name.sim:仿真结果

-

project_name.srcs:工程的源码、仿真文件与约束文件

-

project_name.xpr: Vivado 工程启动文件

根据后缀名不同,文件内容也不同:

1、dcp文件,dcp文件是Design CheckPoint的缩写,中文翻译为“设计检查点”,它是一种加密的、压缩的二进制文件类型,包含了完整的设计信息,如实例化层次结构、资源使用情况、时序分析数据、约束等重要信息。在Vivado设计中,DCP文件通常用于在不同的Vivado工程或版本之间共享设计,并简化设计修改和迁移,或增量编译。

2、xdc文件,vivado的约束文件,比如时序约束和IO引脚约束。

3、xci文件,定制ip产生的文件,里面包含了定制的ip核的所有信息。

4、rpt文件,vivado每个过程结束输出的一个report文件,用来记录各个过程中的一些信息

二、清理vivado工程

在实际使用Vivado过程中,该工具会自动生成一系列文件,有些文件是不必时刻保存的中间文件,有些是为了提高编译效率而生成的(比如编译IP核后产生的文件)。然而在上传SVN或备份时,我们希望占用尽量少的存储空间。由于Vivado无法自动清理这些文件,因此需要手动清理。

清理vivado是有tcl命令可以帮助清理的,如:reset_project 和reset_project -exclude ip

reset_project 用于重置当前项目重置为初始状态,清除在综合,模拟,实现和write_bitstream过程中创建的所有输出文件,包括临时文件。但是要注意,这会清理所有的IP和缓存,如果是大工程的话,清理完后,第一次重新编译需要花费更多的时间。

reset_project -exclude ip 可复位整个项目,但不会清理IP 目录下的文件。

三、清理仿真工程结果

如果是使用vivado仿真器仿真,在仿真的过程中,将会产生很多数据缓存,将大量占据磁盘空间,在关闭仿真后,可以通过reset_sim这个TCL命令,用来清空项目的仿真目录下文件。

但要注意,在系统的temp文件夹中,可能也与仿真文件缓存存在,如果发现系统C盘的空间越来越小,可以定期清理下。

四、总结

在FPGA开发中,Vivado是一款非常好用的开发工具。但是,由于工程文件数量庞大,很容易导致工程变得混乱不堪。因此,在进行开发时,我们需要根据实际需要来清理工程,以避免出现一些不必要的问题。本文介绍了如何清理整个Vivado工程和Vivado仿真缓存,希望能对大家的FPGA开发工作有所帮助。