半生风雨半生伤,半醉半醒半心凉

文章目录

- 前言

- 5.1 CPU的功能和基本结构

- 5.2 指令周期的数据流

- 5.3.1 单总线结构

- 5.3.2 专用通路结构

前言

之前我们就说过CPU主要包括两个部分,运算器和控制器,运算器主要是实现算数运算.逻辑运算,

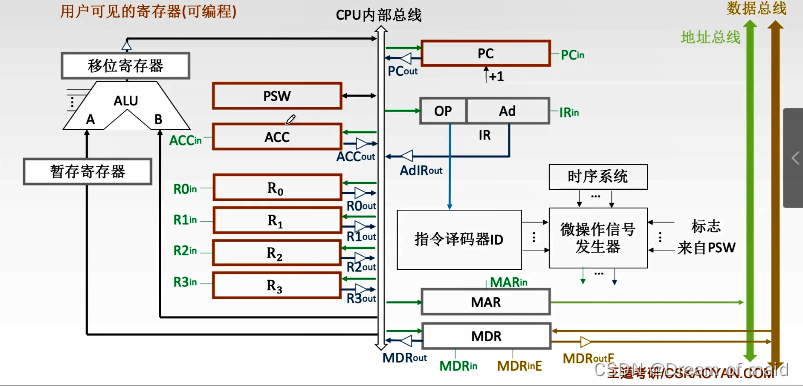

运算器若是再细分,则可分为ACC累加器,用于存放操作数,或者运算结果,MQ:乘商寄存器,在乘,除运算时,用于存放操作数或者运算结果,MQ乘商寄存器,在乘除运算时,用于存放操作数或运算结果,X 通用的操作数寄存器,用于存放操作数,ALU 算数逻辑单元,通过内部复杂的电路实现算数运算,逻辑运算

控制器可分为CU:控制单元,分析指令,给出控制信号

IR:指令寄存器,存放当前执行的指令

PC:程序计数器,存放下一条指令地址,有自动加1功能,完成一个指令需要取指令PC 分析指令IR 执行指令CU

本章主要讲的问题就是如何控制数据在这些元件之间进行流动的,CU又是如何确定每一步需要做些什么的呢

5.1 CPU的功能和基本结构

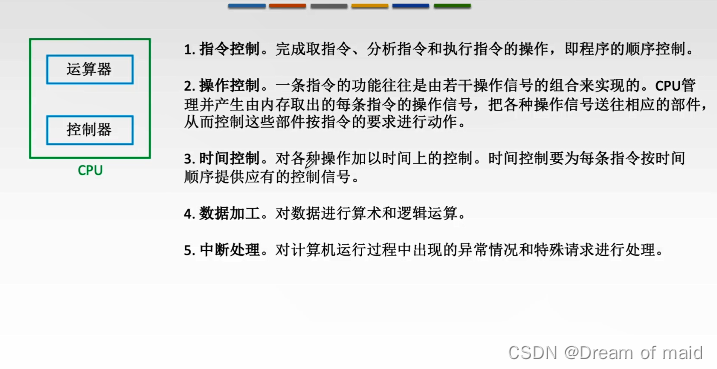

cpu的功能

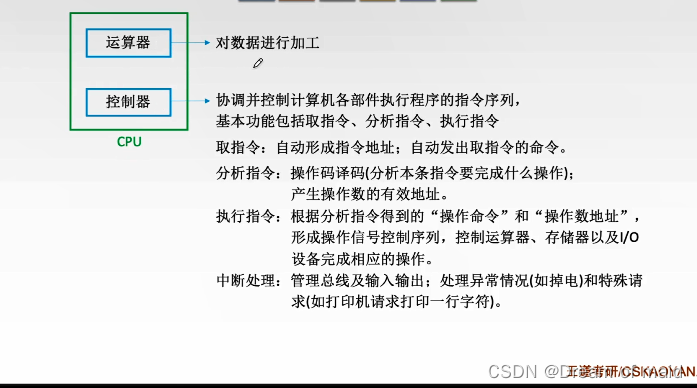

运算器和控制器的功能

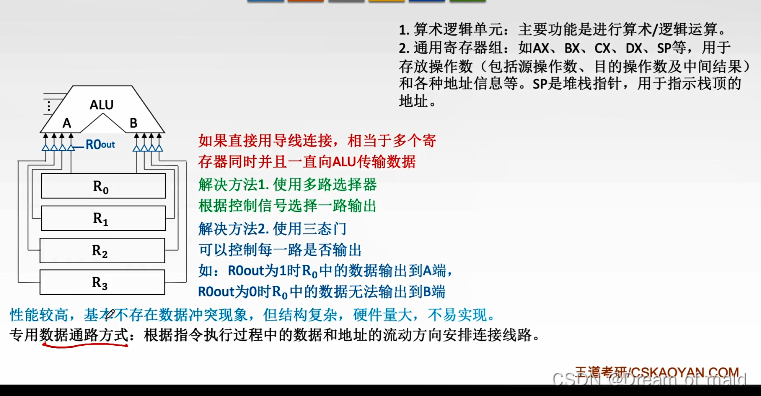

运算器的基本结构

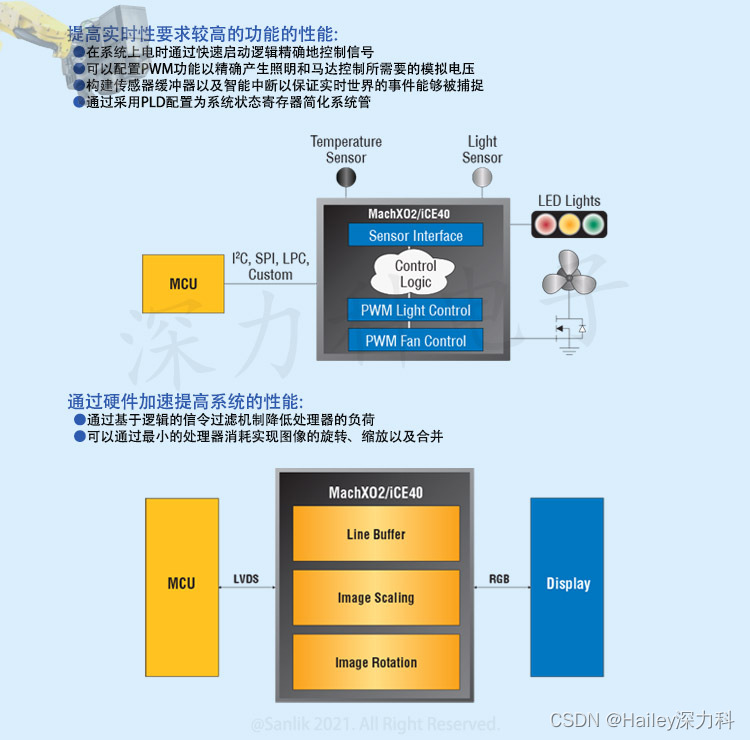

之前我们说过运算器的核心部件是ALU,但是ALU,我们提供操作数,通过ALU 这个逻辑电路的处理可以输出数据,很多时候我们需要把参与的数据提前存放于通用寄存器中

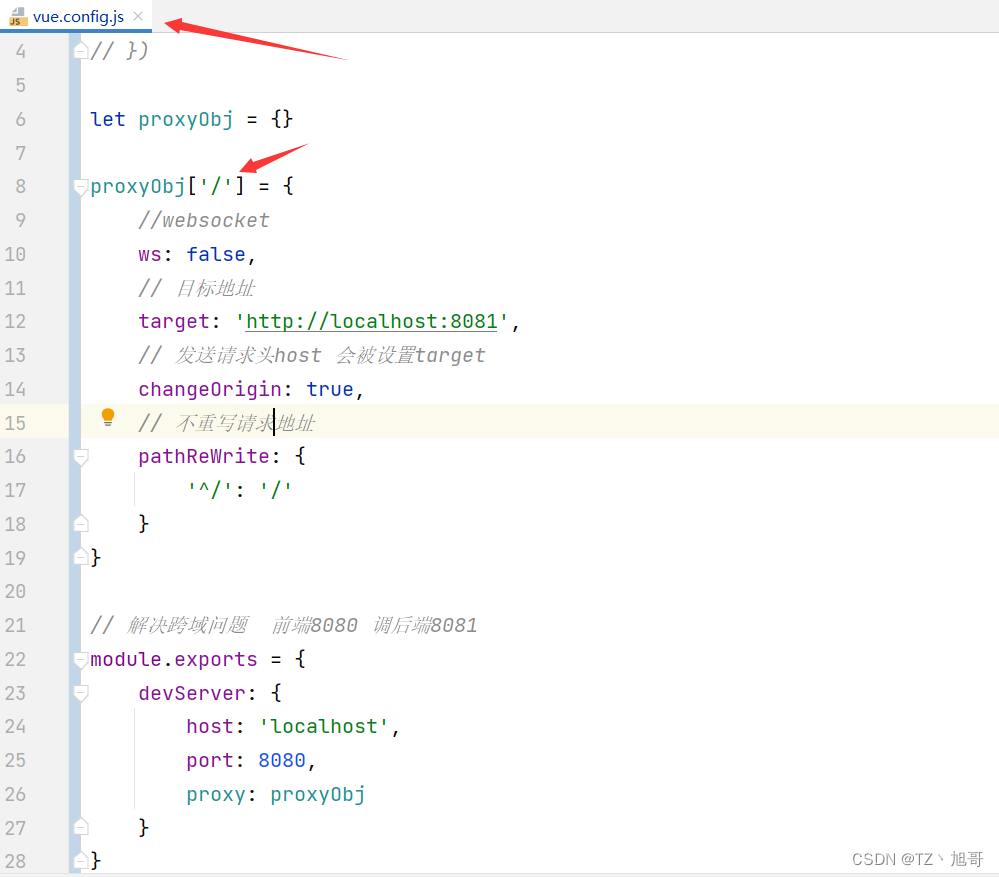

堆栈寄存器SP 保存了堆栈指针,堆栈指针的作用是函数的运行过程中可以会发生函数的调用,程序的执行流发生改变,为了能够使得程序间的相互调用能够完成 堆栈指针指明了当前正在运行的地址在什么位置,因为R0既可以从A输入数据又可以从B 输入数据,所以需要两个线,若是寄存器可以存放16bit的数据,应该是通过十六个线并行的送到ALU的端口的,这种就是称为专用数据通路方式,但是这样也就意味这电路太多,并且可能会有一种情况就是多个寄存器同时并且一直向ALU传输数据,解决方法1,使用多路选择器,根据控制信号选择一路输出,

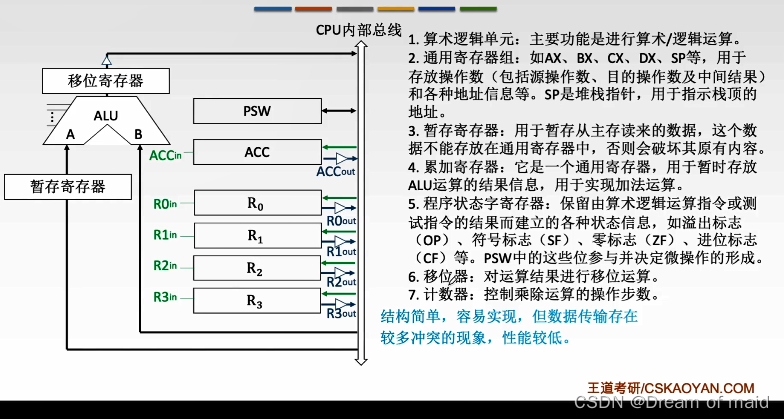

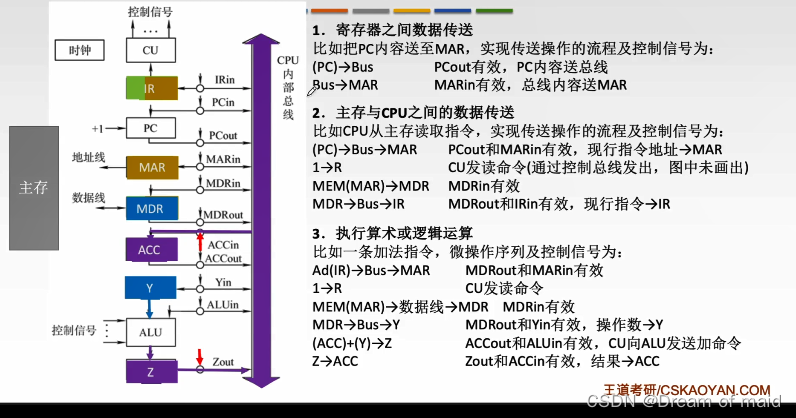

CPU内部总线方式

将所有寄存器的输入端输出端都连接到一条公共的通路上,可以从数据总线上获取输出数据,但是也有一个缺点若是同时通过总线送,则会导致ALU无法判断A,与B的值,一个方法就是设置一个暂存寄存器,先把一个数据送到暂存寄存器中存储起来,不能读入其他通用寄存器是因为其他通用寄存器也可能存放后面需要使用的数据,同时R0给的输入信号不稳定之前,ALU 就会输出信号,此时都在数据总线上 可能会发生冲突,我们的方法是ALU的输出端再加一个暂存寄存器,先把计算的结果放在暂存寄存器中,同时运算器内部还需要一个计数器,如乘的时候需要控制加的次数

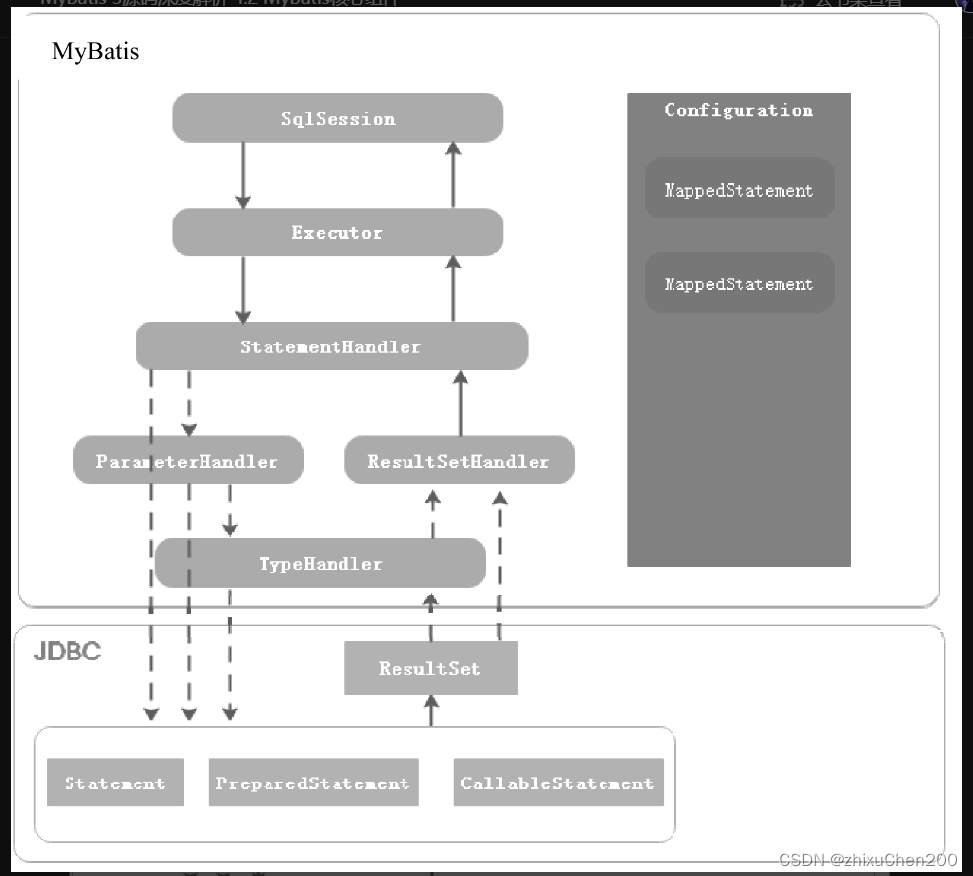

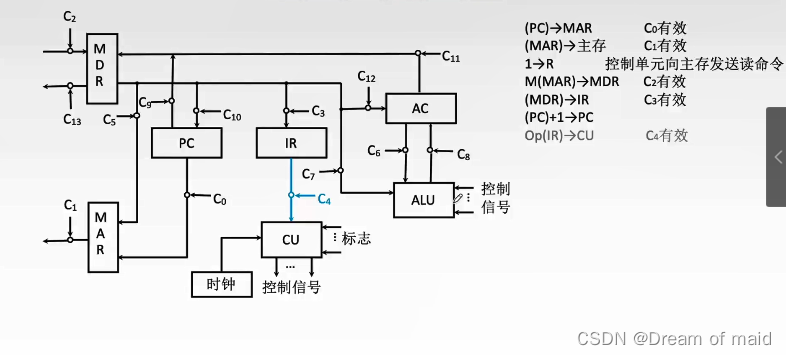

控制器的基本结构

我们取出一个指令之后要把这个指令存放于IR中,把指令的操作码部分作为指令译码器的输入,然后经过指令译码器中的逻辑电路就能判断出当前是什么指令,然后产生微操作序列,然后我们还需要一个时序系统来产生一个时序信号,注意mar的连线只有一个输入的连线没有输出的连线,当有一个地址信息来到MAR中,这个地址指明了在主存中的地址,我们需要外部的地址总线传送给主存,然后通过外部的数据总线将数据存放于MDR中,我们注意到MDR中加E的表示从外部数据总线 上的输入输出是有效的,不加E的是内部输入输出有效的

用户可以通过条件转移指令或者无条件转移指令来修改PC的值,我们之前说过之前条件转移的时候就使用到PSW的值 ,或者使用CMP比较两个数的时候也会直接影响PSW的值

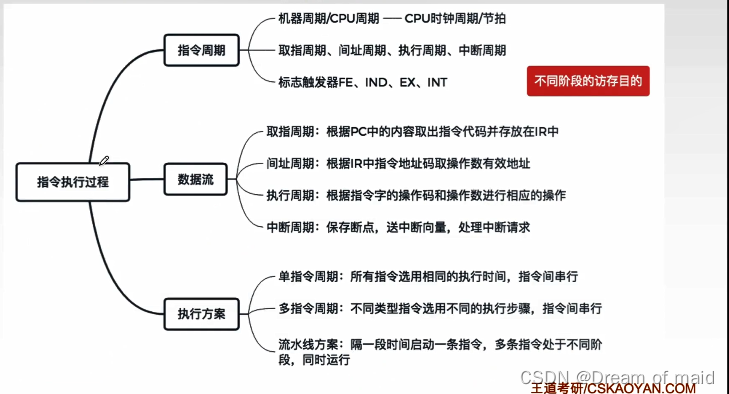

5.2 指令周期的数据流

这一小节中我们对指令的阶段进行一个细化,我们会分析每一个阶段数据流的流向,并且如何安排多条指令的执行

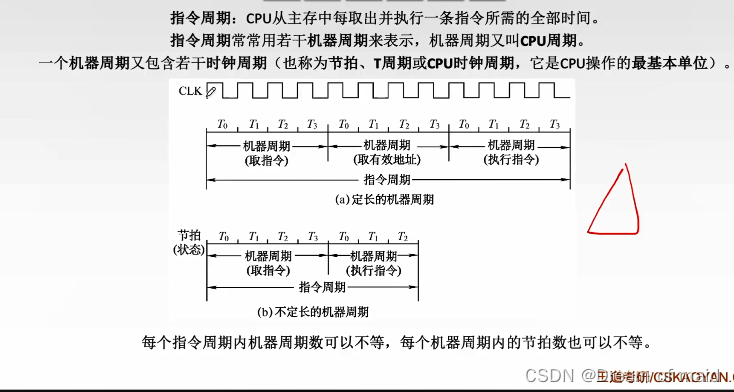

指令周期

取指令是需要访问内存的,也就需要而时间较多,分析指令是cpu来处理的,也就会很快能够完成指令的译码,有的执行指令需要访存 有的不需要,所以导致执行指令的时间差别很大,一个机器周期完成一个较小的子工作,一个指令周期又会包含多个机器周期,并且包含的机器周期数也可能不一样

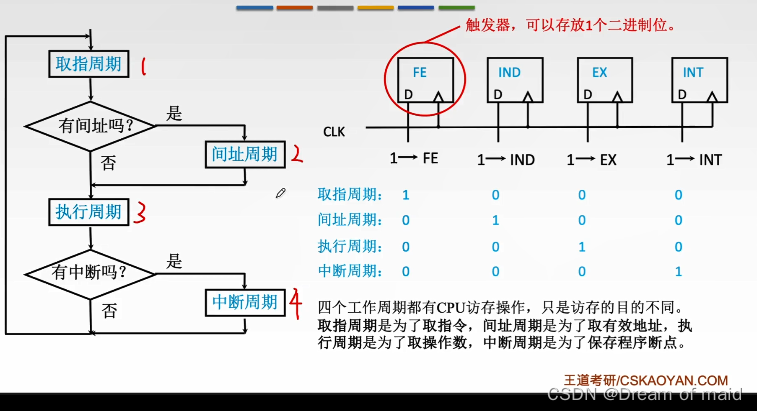

如下图左部分 cpu为了区分这四个阶段,也就是设置四个触发器

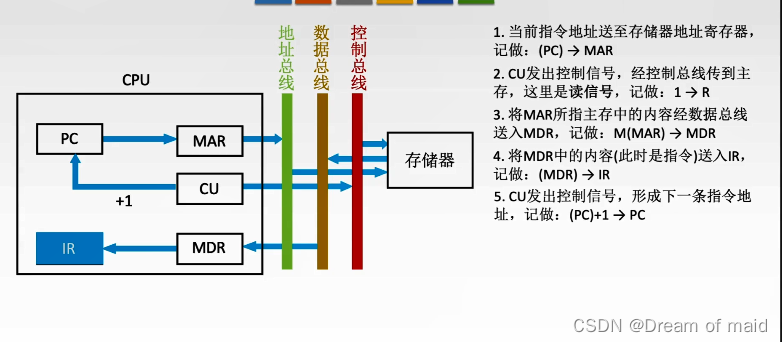

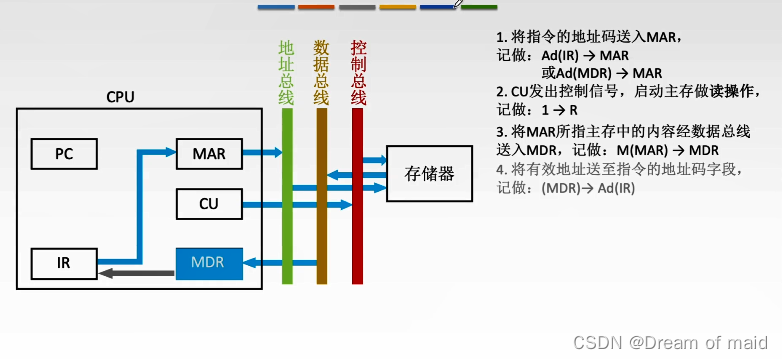

取指周期的一个数据流向

间址周期

这里Ad(MDR)->MAR能成功是因为我们取指的时候是先将MDR中的地址先放在MDR中,然后IR在复制一份的,所以MDR中存储的是当前执行的指令的一个信息

执行周期

执行周期的任务是根据IR中的指令字的操作码和操作数通过ALU操作产生执行的结果,不同的指令的执行周期操作不同,因此没有统一的数据流向

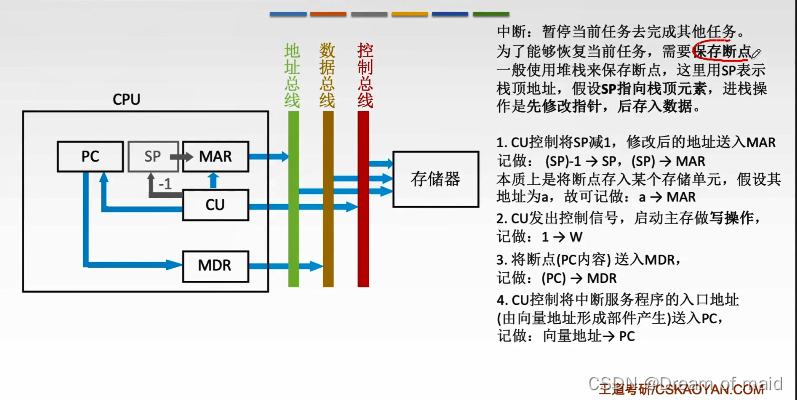

中断周期

之前我们就说过在每一个进程,每一个程序运行的过程中,操作系统都会给程序在主存中开辟一个空间作为运行堆栈,堆栈指针SP会指向当前的栈顶元素,这里与数据结构中有区别,数据结构中地址是从下往上画的,但是操作系统是从上往下画的,也就是我们的栈顶指针是指向低地址部分,所以我们要将一个数压入栈中,就需要先减,此时我们是想把pC的值写入栈顶,CU 通过控制总线启动主存做写操作

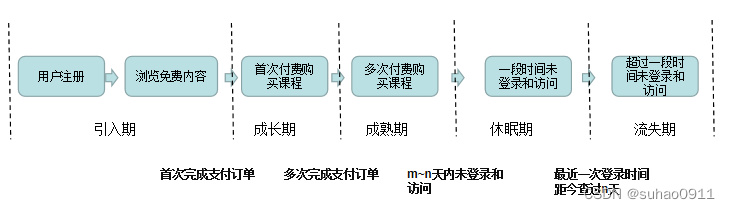

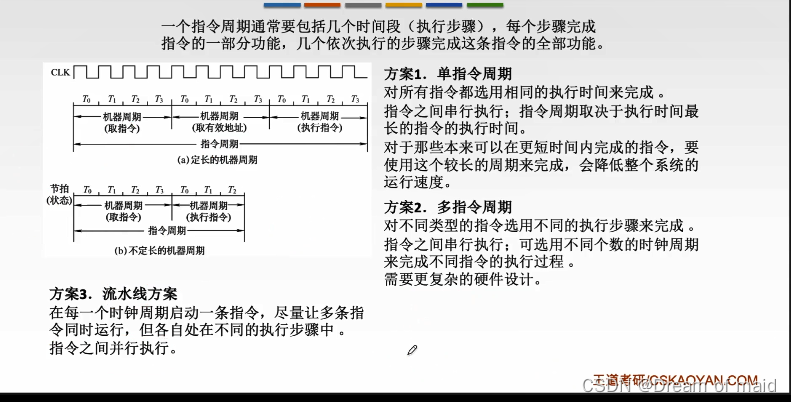

指令执行方案

单指令周期:对所有的指令都选用相同的执行时间来完成,时间较短的会导致浪费较长的时间,从而导致效率低

多指令周期:其实也就是一个指令执行完了就执行另外一个,

流水线方案:不同指令在不同的时间用到的部件可能不同,所以并行也是存在可行性

本节回顾

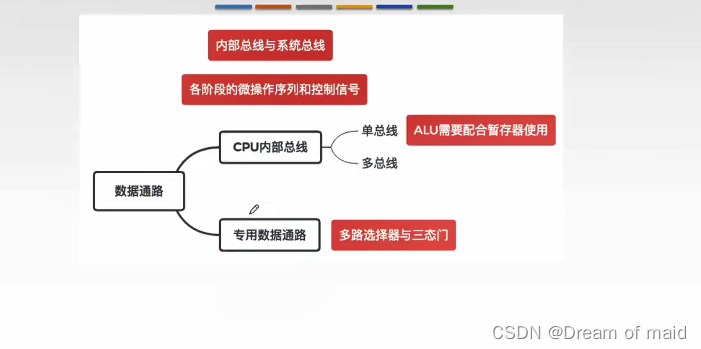

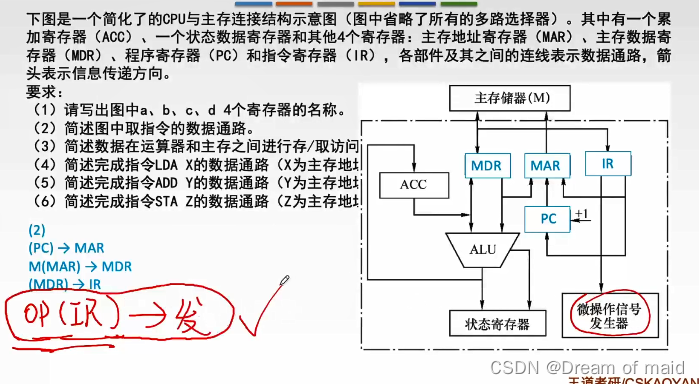

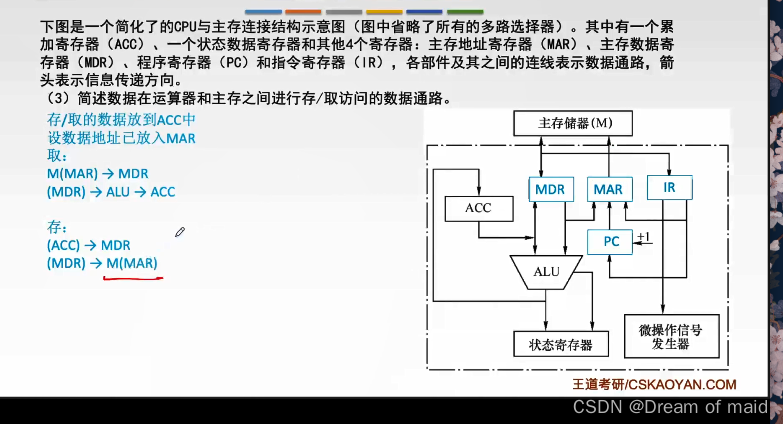

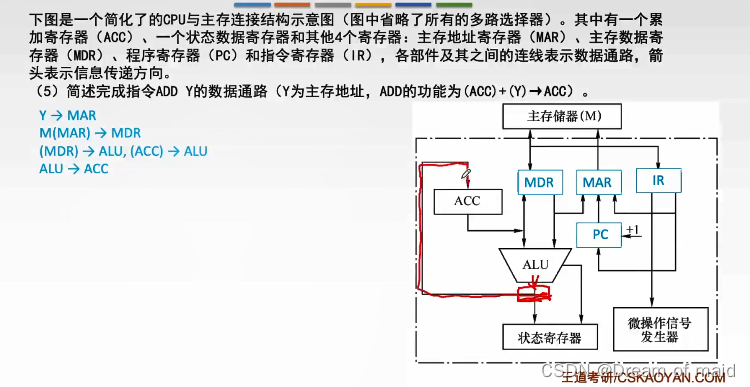

5.3.1 单总线结构

无论我们执行的是什么操作,数据的流向都是不外乎三种,寄存器与寄存器之间,寄存器与主存之间,寄存器与算术逻辑单元之间进行数据交换,无论是数据的输出还是输入操作都是由这个微操作信号发生器来控制的,之前我们说过的一种CPU内部单总线方式,这种也就意味着同一时刻内部总线只允许两个部件之间进行数据交换,为了解决这个问题,有的计算机就设计三个总线,或若是两个会进行数据交换,则在此部件之间设置一个专用的数据通路方式,这里选哟注意执行算数运算的时候,ALU需要两个输入信号必须同时有效,而我们CPU的内部总线同一时刻只能有一个输入信号,我们只有将一个操作数存放于暂存寄存器Y中,若是使用多总线则可不设置暂存寄存器

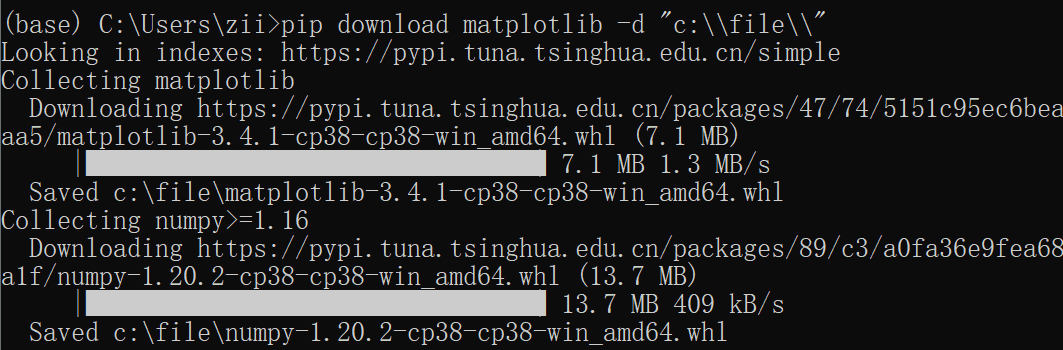

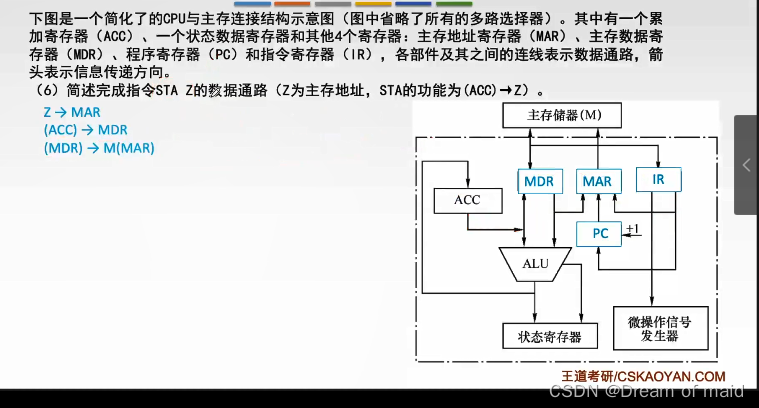

5.3.2 专用通路结构

也就是假如元件之间有数据的交流,则其中的控制信号有效就好,这里用灰色是因为有的并不会给你指令寄存器到cu的通路

多路选择器:如下图中的MAR,当有多个输入的时候,可以接一个多路选择器,选择让哪一个输入通过,还有就是使用三态门,只有微操作信号发生器发出一个信号之后,输入的通路才会被导通,

本节回顾