误逐世间乐,颇穷理乱情

文章目录

- 前言

- 6.1.1 总线概述

- 6.1.2 总线的性能指标

- 6.2 总线仲裁(408不考)

前言

本章在概述部分我们会首先介绍一下总线的基本概念,介绍一下总线的分类以及经典结构,介绍一些性能指标来评价总线的性能如何,第二个部分我们介绍一下仲裁的问题,用来解决多个设备争用总线的问题,当设备之间进行数据交换的时候占用总线的一对设备如何进行数据传输,第四部分我们来介绍一下目前流行的总线标准

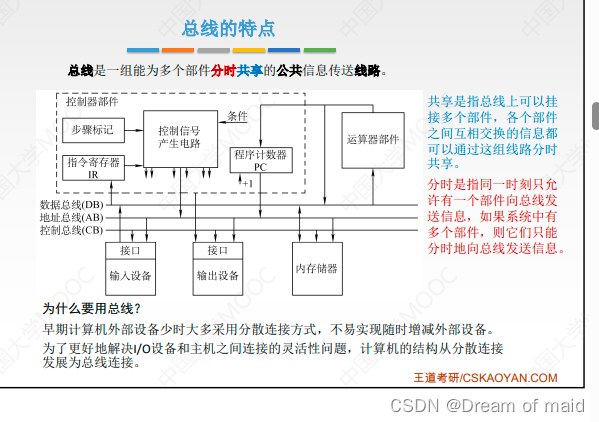

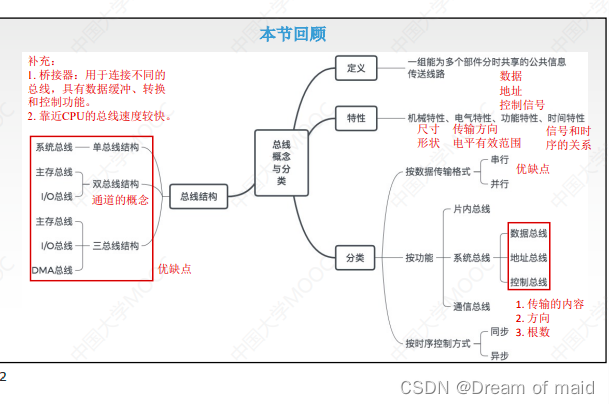

6.1.1 总线概述

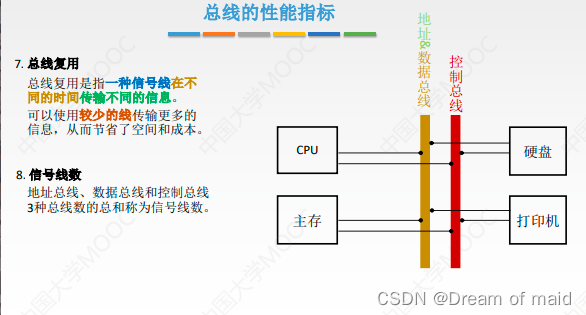

之前我们提到过数据总线,地址总线,控制总线,一个总线内部可能其中包括多个信号线,所有的硬件部件都可以通过这根总线传递数据,可以并行的发送多个数据,同一时刻只能一个部件发送数据,但可有多个部件接受数据

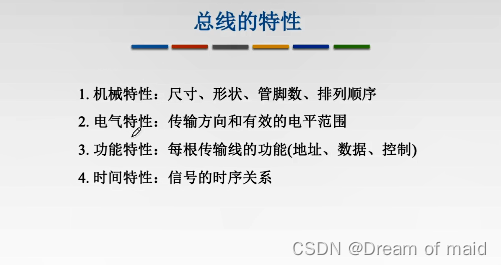

总线的特征

这里传输方向的意思是比如这里CPU通过地址总线指明此次主存要读或者要写的内容,而主存并不给CPU地址,而数据总线确实双向的

有效电平范围:比如我们规定高电平4.8~ 5.0 低电平0~0.5,我们认为只有高低电平落到这样一个范围的时候才是有效的

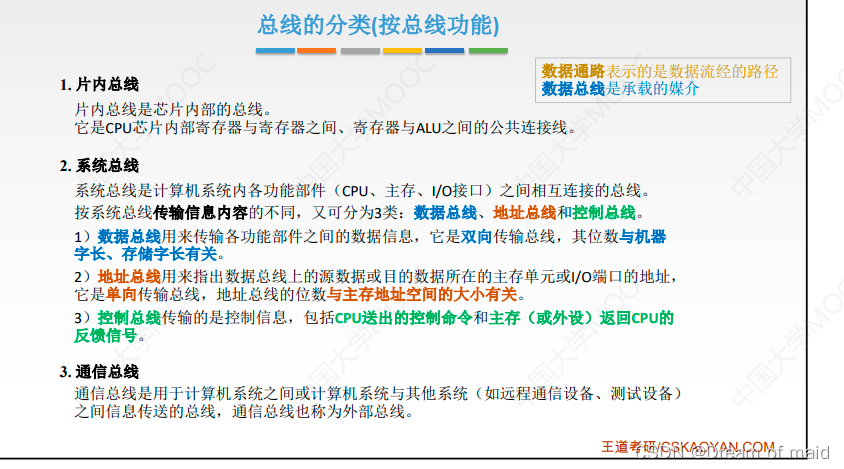

总线的分类

我们可以从多个不同的维度对总线进行分类

按数据传输格式分

串行:每次只能传一位(USB)且抗干扰能力强,也就意味着在长距离传输中数据不容易发生跳变,并且因为只需要一个线,也会节省电路板上的布线空间,虽然我们是串行的发送的 但是我们依然需要转变成并行在发给CPU

并行: 每次可以传多位,当我们把多个信号线并在一起的时候,这些信号线在传递的过程中有可能会造成信息的干扰,导致二进制信息位的跳变,这也就限制了频率不能太高,所有有可能信息传输的速率并没有串行总线来的快

按总线功能(连接的部件)进行分类

数据总线:若是数据总线的位数或者说根数若是与机器字长相等的话,CPU可以通过一次的数据读入,就可以直接处理的那么多的数据,若是数据总线和存储字长相等的话,也就意味着每一次的主存读或者写操作 只需要主存进行一次的读或者写就可以

地址总线:当我们的I/O设备与主存选择统一编址的时候,I/O设备也会影响地址总线的数量

控制总线:有的控制心线是CPU 发向其他设备的,有些则是其他的硬件信号发送给CPU 的,所以对于单根的信号线来说信号的传递方向是单向的,对于整个控制总线来说传输方向是双向的

通信总线:网线就是一种

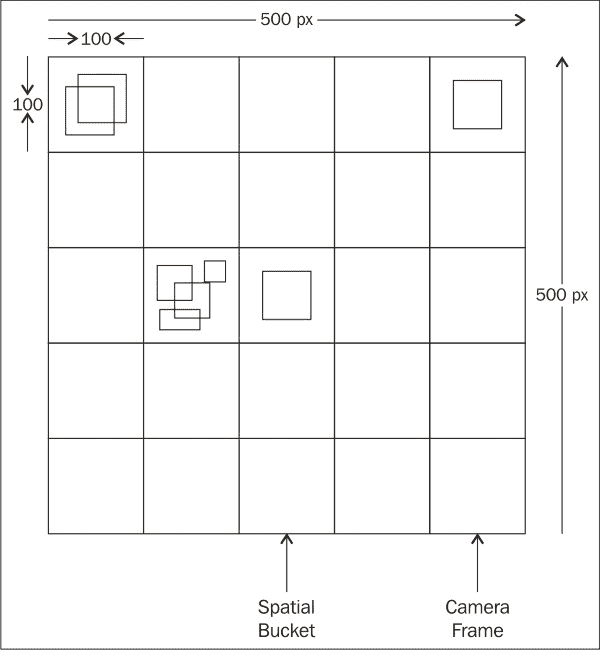

系统总线的结构

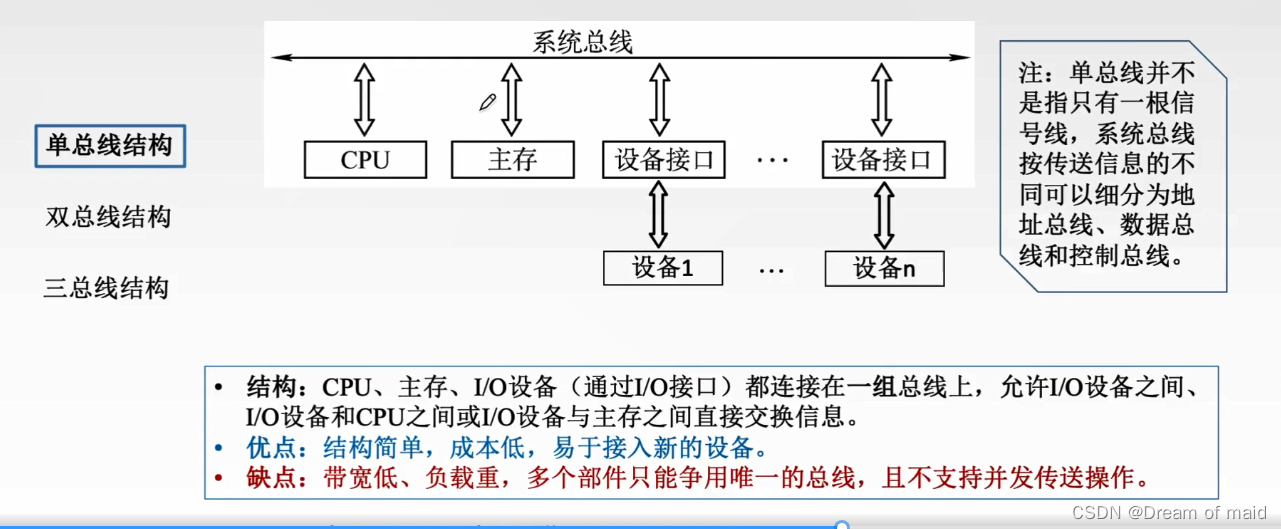

系统总线的结构分为单总线结构,双总线结构,和三总线结构

单总线结构

第六章主要讲的就是这个细分之后的系统总线的结构

这里所说的系统总线就是包括了数据总线,地址总线,控制总线的一组总线

这里的并发指的是同一时刻只能有两个部件之间进行数据的发送,不可能是多组部件通过总线进行数据的传递

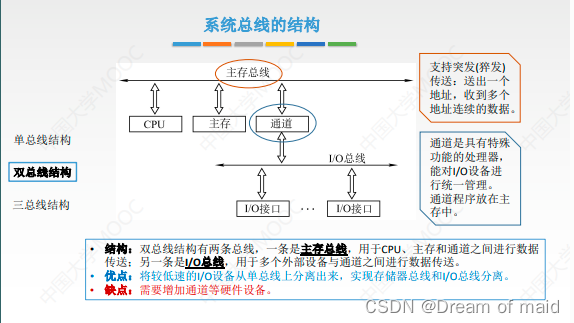

双总线结构

通道:我们可以把通道理解为阉割版的CPU,但是这个功能部件是专门来管理各个I/O 设备的,因为通道的处理速度也很快,所以我们将CPU与通道通过快速的主存总线进行相连接,这样可以保证主存总线的性能发挥出来,I/O总线因为下方的I/O设备输入的较慢,这里也可以设计较慢,引入通道是为了缓和CPU与各种I/O设备的速度问题

突发(猝发):CPU指明一个地址之后,如果能从主存之中连续的读出多个数据能提高系统效率

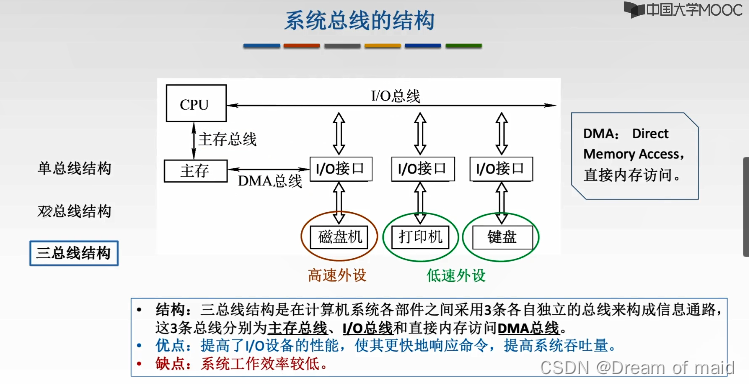

三总线结构

DMA总线:磁盘是高速外设,而打印机 键盘就是低速的外设,我们对磁盘的读写是以块为单位的,我们将磁盘与主存之间的数据交换就是通过DMA总线进行,这样的好处是CPU与磁盘机不需要通过慢速的I/O总线进行数据的交互,这样也是为了缓和磁盘与CPU之间的速度关系,I/O总线的速度就慢一些,CPU就可以通过I/O总线与一些慢速的外设进行数据的交互

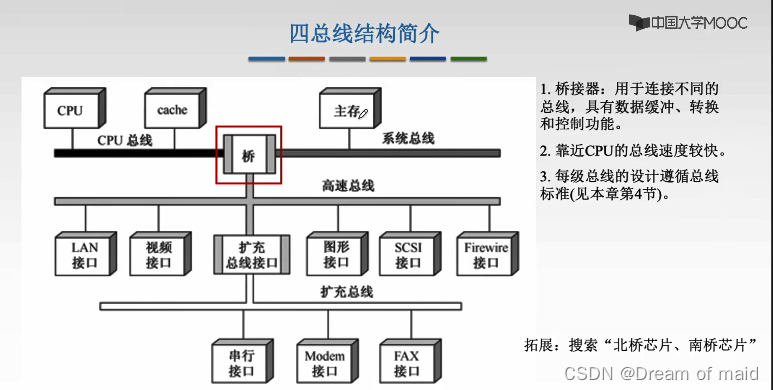

四总线结构

现代计算机更常使用的一种结构

本节回顾

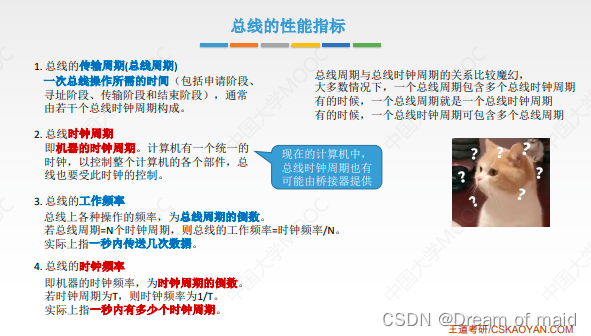

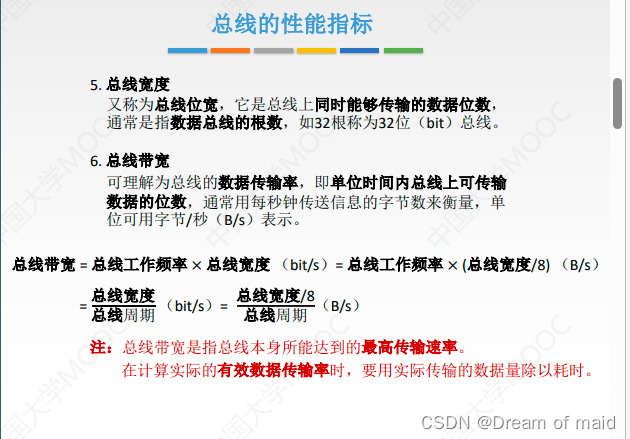

6.1.2 总线的性能指标

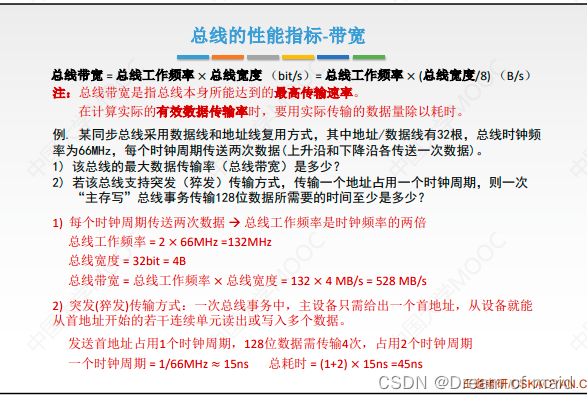

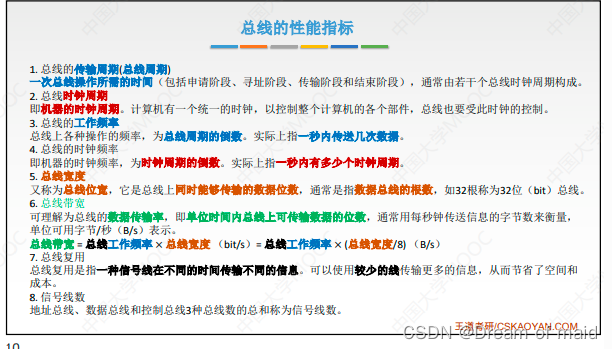

一次总线操作所需的时间(包括申请阶段(这个阶段要做的就是总线仲裁),寻址阶段(主设备通过地址总线把要读或者要写的地址单元送到从设备) 传输阶段,结束阶段(释放总线的使用权))

时钟周期也就是节拍信号,

总线时钟周期和总线周期有可能是一对一,一对多,多对一的关系(如检测到电平信号从高电平变成低电平可以进行一次的总线传输,检测到电信号从低电平到高电平又会传输一次数据,这样一个时钟周期内上升沿和下降沿都进行了一次总线的传输,那也就意味着一个时钟周期内包含了两个总线周期)

最高传输速率:其中可以包含一些校验位,开头标准,结尾标志什么的,并不是都是有效信息

总线复用的时间成本会更高

列题

本节回顾

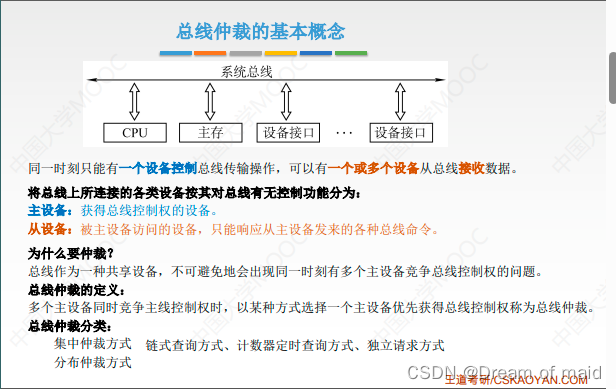

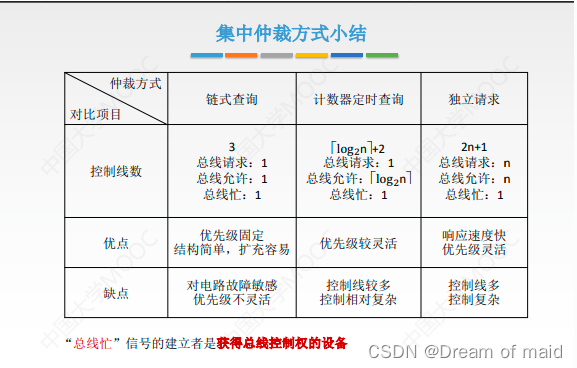

6.2 总线仲裁(408不考)

由于总线是一种贡献的设备,同一时间只能提供给一个设备,那么如何解决多个设备争用总线的问题,设备首先会通过控制总线中的某个线路向总线的控制器发出一个请求,请求总线的使用权,当总线的使用权分配给这个设备的时候,这个设备就是主设备,然后使用数据总线和地址总线进行数据的传输,选择与那个设备进行数据传输这是由当前的已经获得总线控制权的设备决定的,集中仲裁方式又可分三种方式:链表查询方式,计数器查询方式,独立请求方式

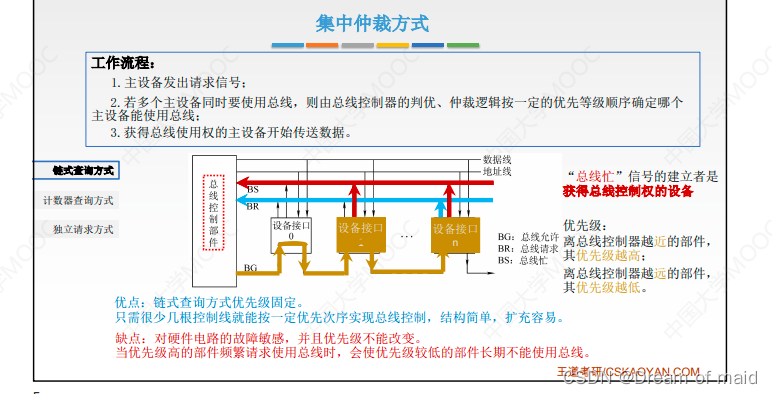

链式仲裁方式

这个总线控制器一般被集成与CPU内部 或者集成与桥接器里面,然后安装一定的优先级顺序,设备通过BR这个信号线上发送要给高电平信号,总线控制部件发出总线允许的信号,当设备收到这个信号的时候就会对总线进行控制,并截断这个BG控制信号向后传,同时往BS总线忙这个信号线上输入一个高电平信号,表示这总线已经被占了,当总线控制部件检测到BS这个信号的时候,就会撤销BG这个信号。会产生饥饿现象,也就是设备优先级高的若是一直请求使用,则低的一直使用不到,并且其中若是有一个设备损坏,信信号可能就无法向后传

用一个故事就是游戏机器的使用就是大儿子玩完才能给二儿子玩,然后是三儿子

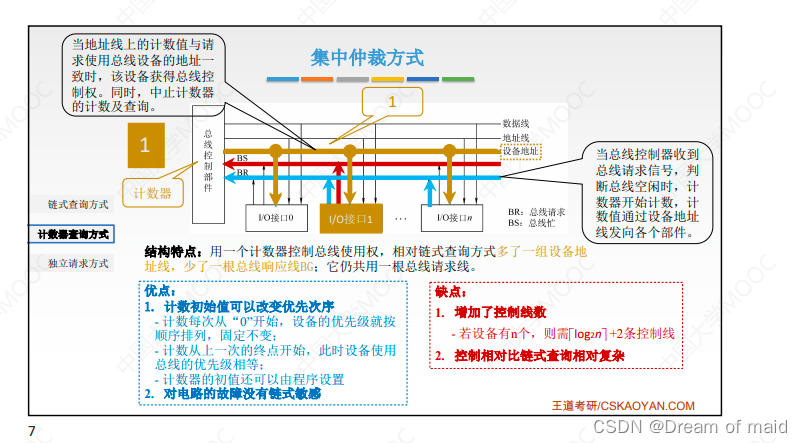

计数器查询方式

首先这里控制部件里面会加一个计数器,当总线控制部件检测到有部件要使用设备的时候也就是有BR信号的时候,这个计数器会进行计数,会从0开始计数,然后这个设备地址(是有多组线)中传过来的数据就是0,表示它正在询问0号这个设备是不是你要使用

加的这两个控制线就是BS与BR这两个控制线

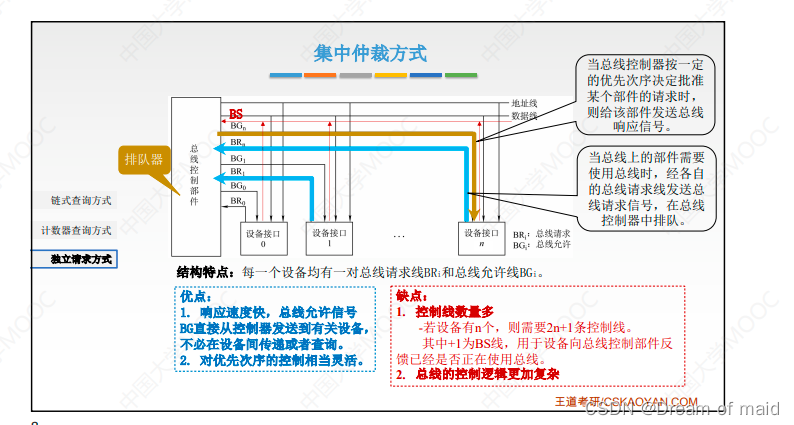

独立请求方式

每个设备与总线控制单元部件间不止有BR还有BG,当接收到多个设备的时候,排队器会决定将控制部件给那个设备,并且所有的信号线都会与总线忙这个信号线进行连接,当设备获得总线控制部件的控制权之后,就会发出一个BS信号,当总线控制部件检测到BS信号就知道已经成功分配,控制部件就会撤销BG这个信号,每一个设备都需要BG,与BR 所以是2n,同时所有的都连接到一个BS线上 ,所以是2n+1条控制线

集中仲裁方式小结

分布仲裁方式

当有多个设备请求申请总线的时候,每一个设备都将自己的仲裁号发送到一个地方,进行优先级比较,