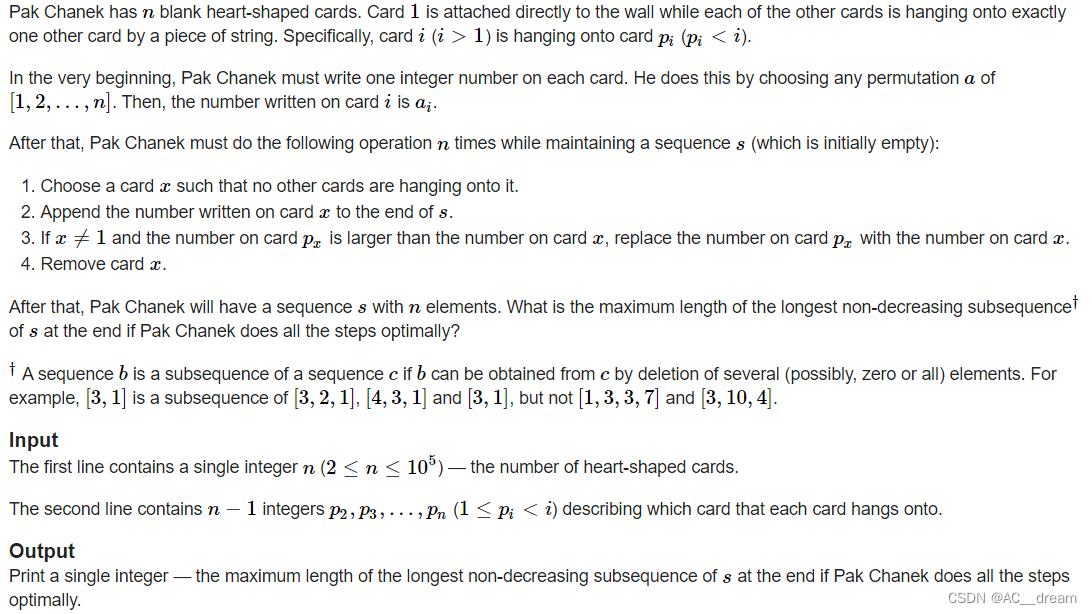

二选一工作器引入的Verilog语法

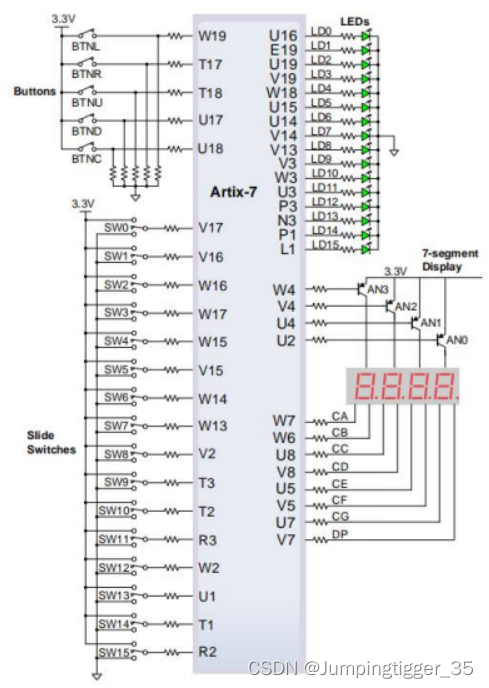

——XILINX 基于BASYS 3板

状态机、线性序列机、学习仿真

DDS:矩阵键盘、DAC,LCD/数码管,这些模块间的接口逻辑

常见的接口设计:SPI、IIC、UART

学习:三八译码器、计数器电灯、学习开发工具的使用

实现步骤:

写一套硬件描述语言,能够在指定的硬件平台上实现相应的功能。

1、设计定义

2、设计输入

3、分析综合(EDA、Quartus、Vivado)

4、功能仿真(Modelsim)

5、布局布线(Quartus、Vivado)

6、分析性能(时序仿真Modelsim,静态时序分析Quartus、Vivado)

7、板级调试

设计定义(让LED灯一秒闪烁一次)、设计输入(编写逻辑/使用Verilog代码描述逻辑/画逻辑图/使用IP)。

综合工具:由专业的EDA软件进行,Quartus、Vivado、ISE,对所写的逻辑描述内容进行分析,并得到逻辑门级别的电路内容。

- 验证功能:

功能仿真(逻辑仿真):使用专门的仿真工具进行仿真,验证设计的逻辑功能能够实现、验证功能。

布局布线:在指定器件上将设计的逻辑电路实现。

- 设计性能、分析性能:

1、时序仿真(非常耗费时间)

2、静态时序分析:让逻辑在目标板上正常工作(功能正常、性能稳定)。

下载到目标板上运行,查看运行结果(烧路)。ILA Signaltap II

- 对数字电路来说,仿真基本接近于真实情况,是可信的。

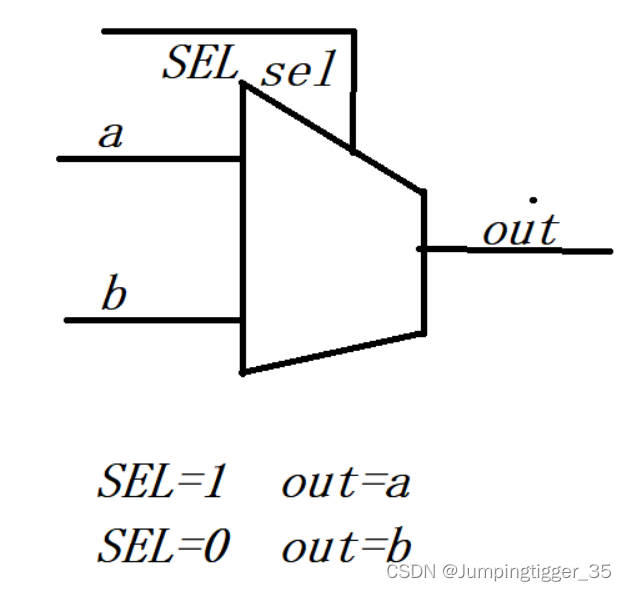

二选一工作器

源代码

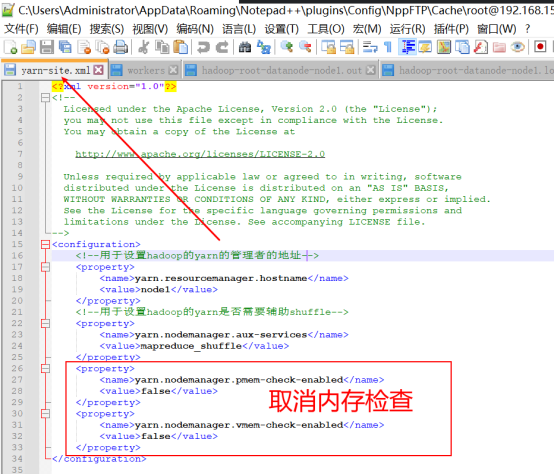

`timescale 1ns / 1ps

module mux2(

a,

b,

sel,

out

);

input a;

input b;

input sel;

output out;//定义端口

assign out=(sel==1)?a:b;

endmodule

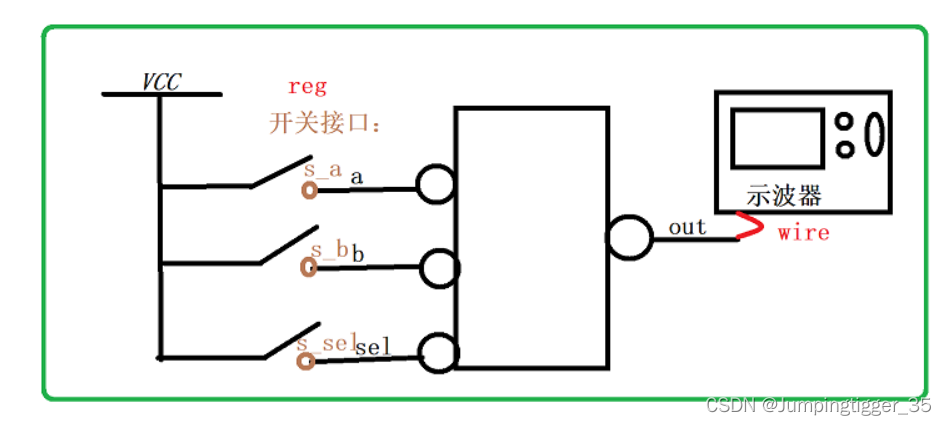

测试激励文件

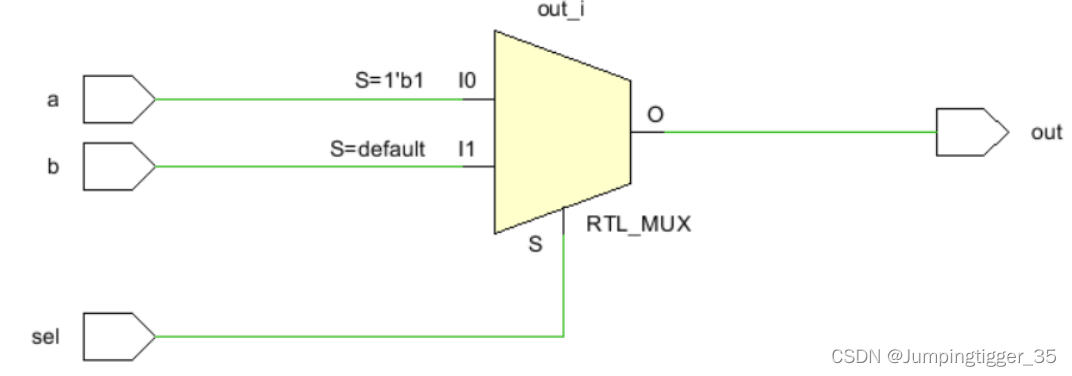

编写的原理图

激励信号的定义:

reg

module mux2_tb();

//定义存在的信号线

reg s_a;

reg s_b;

reg sel;

wire out;

//例化,标题可与例化名称一致(前者一致,后者随意)

mux2 mux2(

.a(s_a),//例化对应既可自己定义,也可用其原名

.b(s_b),

.sel(sel),

.out(out)

);

//初始化

initial begin

s_a=0;s_b=0;sel=0;

#200;

s_a=0;s_b=0;sel=1;

#200;

s_a=0;s_b=1;sel=0;

#200;

s_a=0;s_b=1;sel=1;

#200;

s_a=1;s_b=0;sel=0;

#200;

s_a=1;s_b=0;sel=1;

#200;

s_a=1;s_b=1;sel=0;

#200;

s_a=1;s_b=1;sel=1;

#200;

//仿真时写

$stop;//暂停

end

endmodule

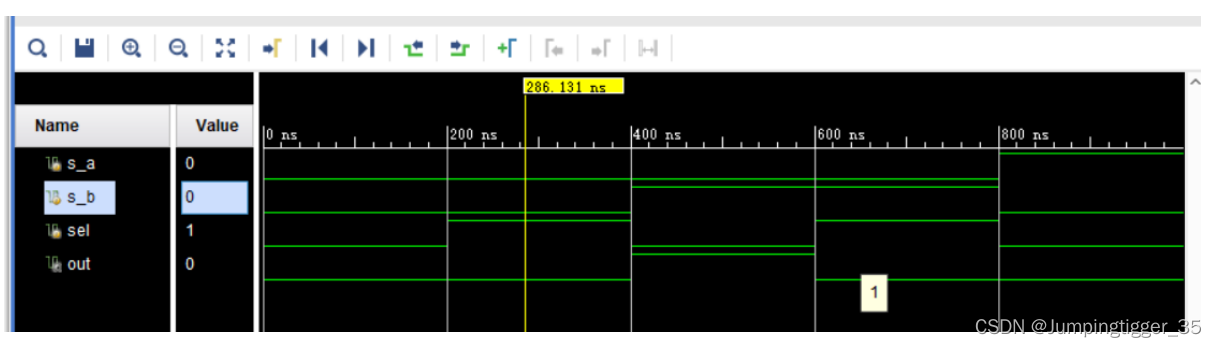

功能仿真

对应真值表,进行检查

布局布线

分配管脚

set_property IOSTANDARD LVCMOS33 [get_ports a]

set_property IOSTANDARD LVCMOS33 [get_ports b]

set_property IOSTANDARD LVCMOS33 [get_ports out]

set_property IOSTANDARD LVCMOS33 [get_ports sel]

set_property PACKAGE_PIN V17 [get_ports a]

set_property PACKAGE_PIN V16 [get_ports b]

set_property PACKAGE_PIN W17 [get_ports sel]

set_property PACKAGE_PIN U16 [get_ports out]