1.5.1 功耗和能耗:系统视角

Q1:处理器需要的最大功耗是多少?

如果处理器的预期功耗大于电源系统能够提供的功耗(试图汲取的电流大于电源系统可以提供的电流),通常会导致电压下降而让器件无法工作。在峰值电流时的功耗变化范围很大,因此提供了电压指数方法让外理器能够减缓速度,在更大幅度内调整电压。显然,这样会降低性能。

Q2:持续功耗是多少?

这个指标通常称为热设计功耗(thermal desien power,TDP)因为它是对系统散热提出的要求。TDP既不是峰值功耗(峰值功耗通堂要高1.5倍),也不是给定计算期间的(可能更低的)实际平均功耗。在为个系统适配电源时,其功耗通常要大于TDP、而冷却系统的散热通常也不小于TDP。如果散热能力不足,处理器中的结点温度可能会超出最大值、导致器件故障,甚至永久损坏。由于最大功耗可能超出TDP指定的长期平均值(从而使热量和温度上升),所以现代处理器提供了两项功能来帮助管理热量一当温度接近结点温度上限时、电路降低时钟频率,从而减小功耗如果这个动作不管用,则启用热过载保护装置,强制芯片断电。

Q3:能耗和能效?

功耗就是单位时间的能耗:1瓦=1焦/秒。能耗更适合用来对比处理器,因为它与特定任务以及该项任务所需要的时间相关联。具体来说,执行一项工作负载的能耗等于平均功耗乘以此项工作负载的执行时间。

因此,如果我们想知道两种处理器中的哪一个对于某一给定任务更为高效,应当对比执行该项任务的能耗,而不是对比功耗。例如,处理器A的平均功耗可能比处理器B高20%,但如果A执行该任务的时间仅为B所需时间的70%,A的能耗就是1.2*0.7=0.84,显然要更低一些。

那功耗什么时候才是一种有用的指标呢?它的主要用途是作为一种约束条件,比如,一个风冷芯片的功耗可能被限定为不得超过100W。如果工作负载是固定的、那就可以用它来进行评价,但在这种情况下,它只不过是平均任务能耗这一真正指标的变体。

1.5.2 微处理器内部的能耗和功耗

对CMOS芯片来说,传统的主要能耗源是开关晶体管,也称为动态能耗(dynamic energy),每个晶体管的能耗跟该晶体管驱动的容性负载与电压平方的乘积成正比:

能耗动态∝容性负载×电压2

这个公式的计算结果就是逻辑转换脉冲0→1→0或1→0→1的能耗。那么一次转换(0→1或1-0的能耗就是:

能耗动态∝1/2×容性负载×电压2

每个晶体管所需要的功耗就是一次转换的能耗与转换频率的乘积:

功耗动态∝1/2×容性负载×电压2×开关频率

对于一项固定任务,降低时钟频率可以降低功耗,但不会降低能耗。

显然,通过降低电压可以大幅降低动态功耗和能耗,所以在20年里,电压已经从5V降低到1v以下。容性负载的大小取决于输出端连接的晶体管数目及所用技术,而该技术决定了连线和晶体管的电容。

当我们从一种制造工艺转向另一种工艺时,晶体管开关次数及其变化频率的增加所产生的影响大于负载电容和电压的隆低,从而导致功耗和能耗的总体上升。第一代微处理器功耗低于1W,第一代32位微处理器(比如Intel80286)功耗大约为2W,而4.0 GHz Intel Core i7-6700K功耗为95W。如果这些热量必须从一个边长大约为1.5cm的芯片上消散出去,那实际已经接近风冷所能达到的极限,而这正是我们近10年来一直停滞不前的地方。

根据上述公式,如果不能降低电压或提高每个芯片的功耗,那么可能就要减缓时钟频率的增长速度。

配电、散热和防热点的难度日益增加。能耗是现在使用晶体管的主要限制因素。因此,现代微处理器提供了许多技术,试图在时钟频率和电源电压保持不变的情况下,提高能效。

(1)以逸待劳。今天的大多数微处理器会关闭非活动模块的时钟,以降低能耗和动态功耗。例如,如果当前没有执行浮点指令,浮点单元的时钟将被禁用如果一些核处于空闲状态,它们的时钟也会被停止。

(2)动态电压-频率调整(dynamic voltage-frequency scaling,DVFS)。第二种技术直接来自上述公式。PMD、笔记本计算机,甚至服务器都会有一些活跃程度较低的时期,在此期间不需要以最高时钟频率和电压运转。现代微处理器通常提供几种能够降低功耗和能耗的工作时钟频率和工作电压。

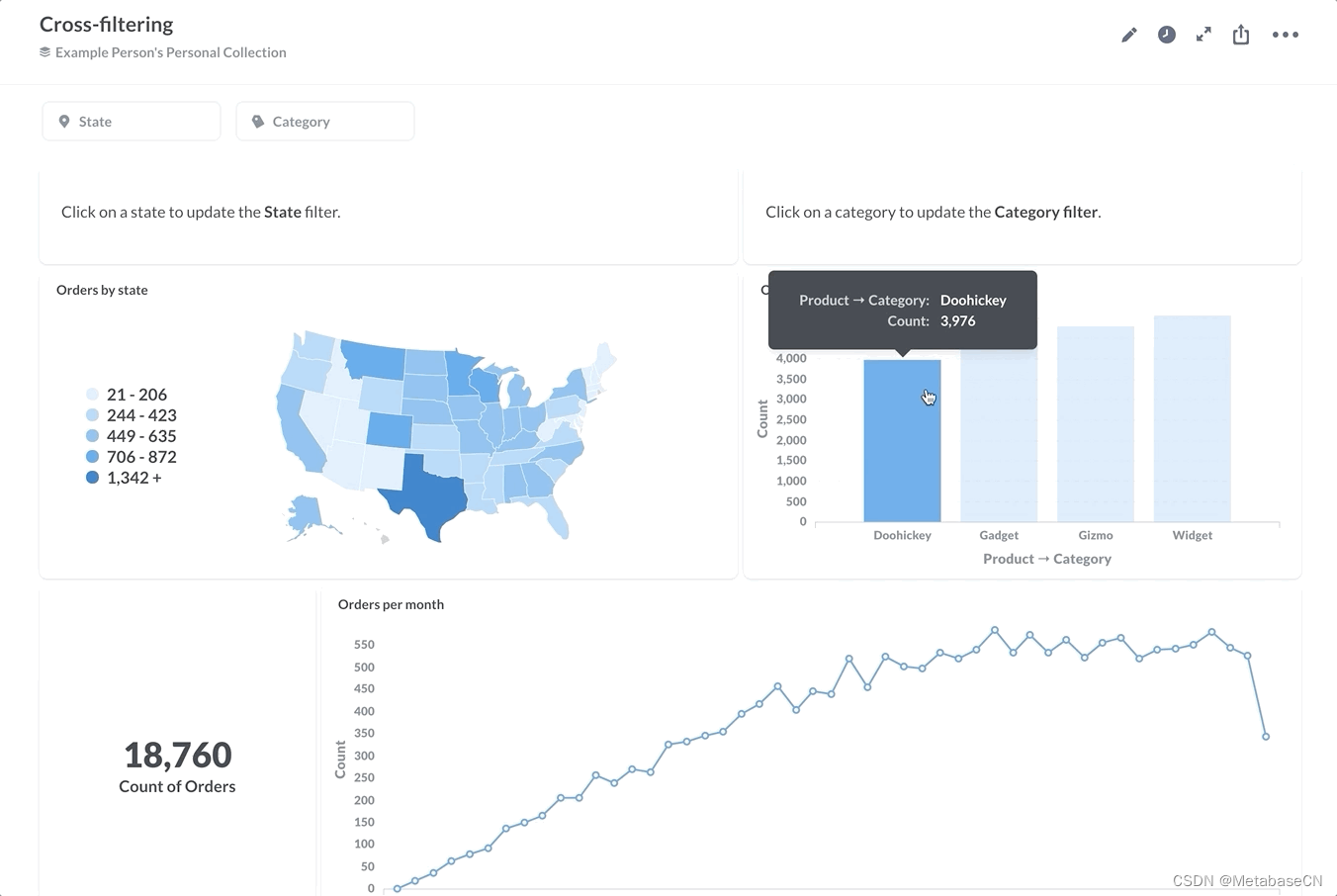

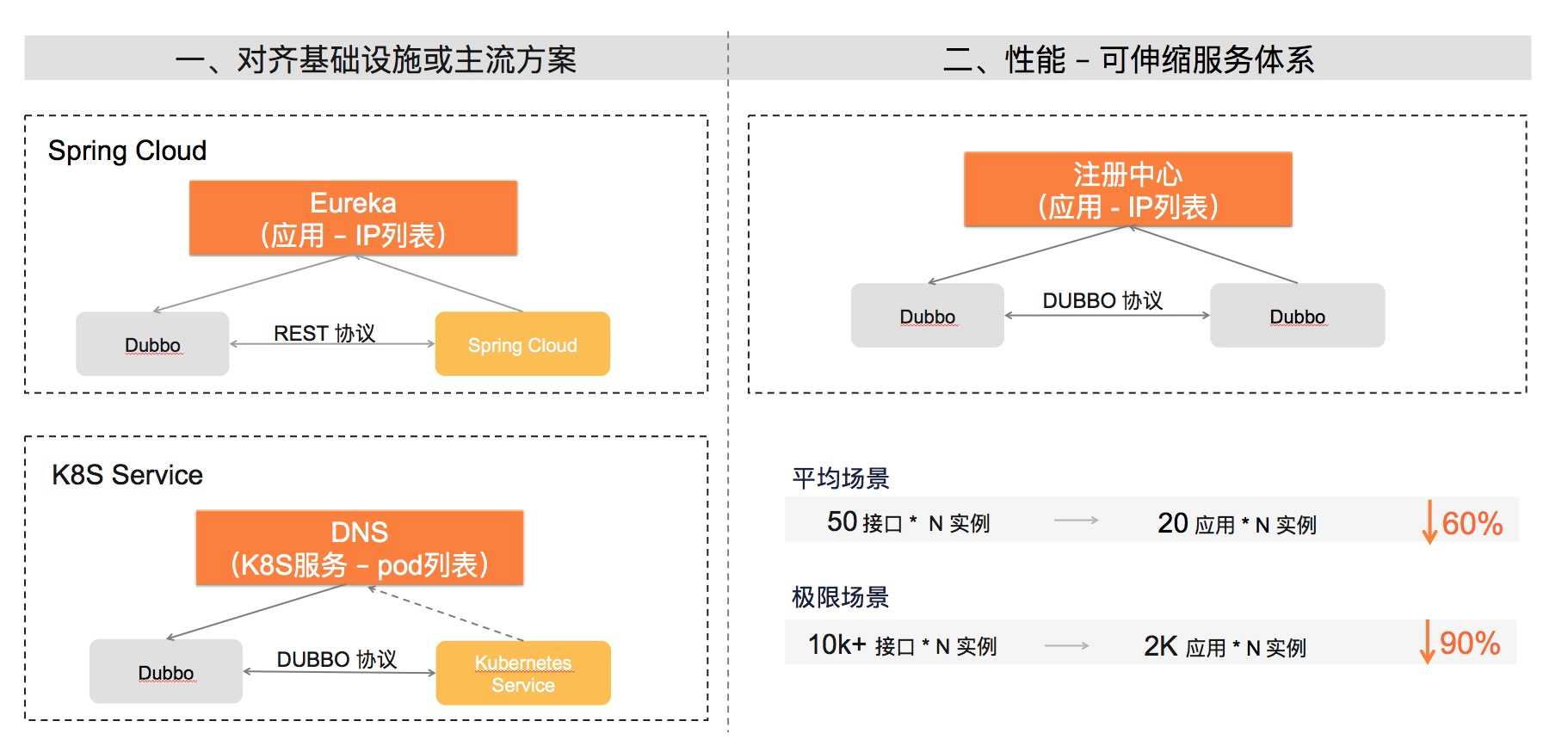

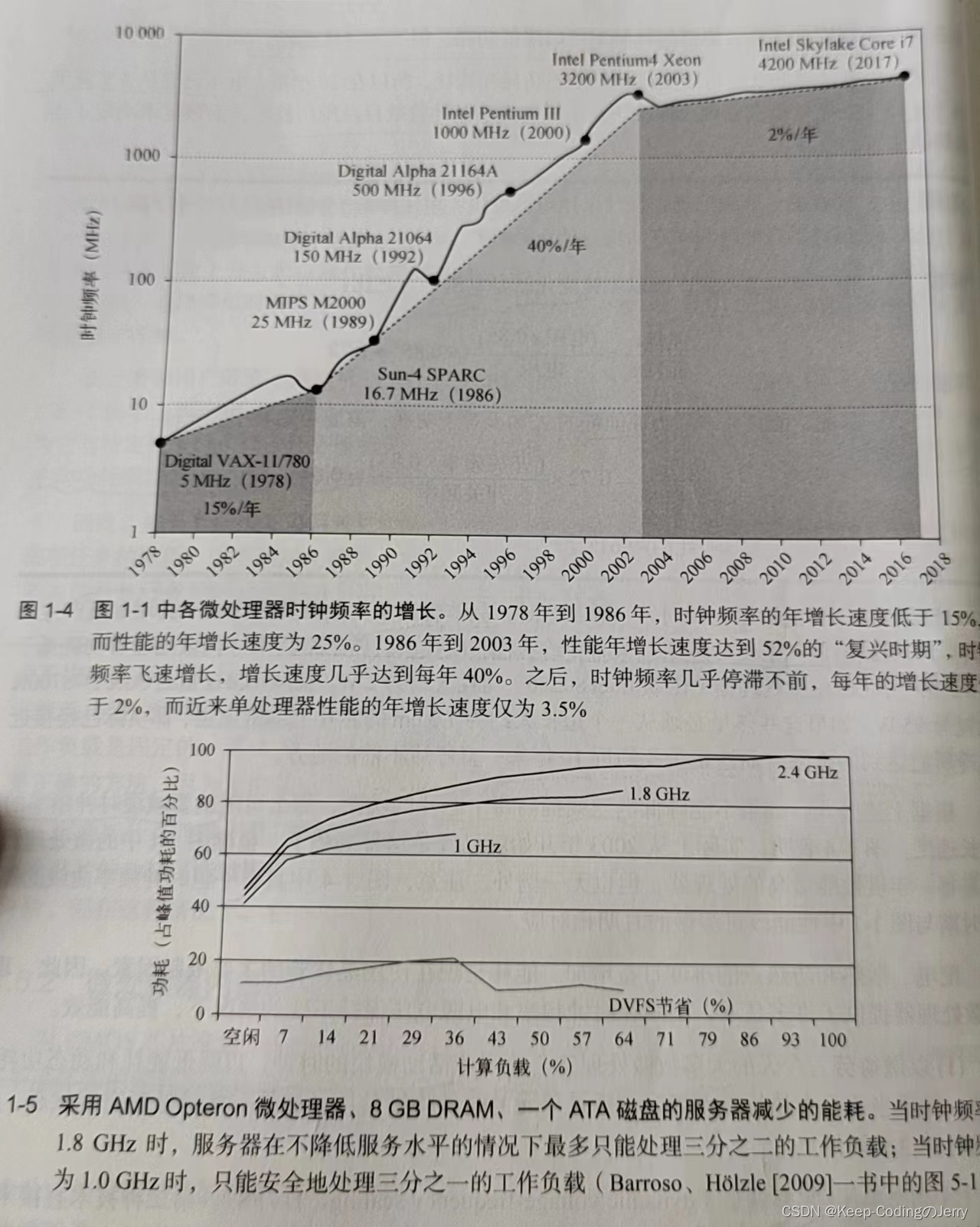

图1-5绘制了当工作负载降低时,服务器通过DVFS可能节省的功耗,3种时钟频率为2.4GH、1.8GHz和1GHz。在这两个步骤中的每一步,服务器可以节省大约10%~15%的总功耗。

(3)针对典型情景的设计。由于PMD和笔记本计算机经常空闲,所以内外存储器都提供了低功耗模式,以减少能耗。例如,DRAM具有一系列功耗逐渐降低的低功耗模式,用于延长PMD和笔记本计算机的电池寿命;同时,针对磁盘也提出了一些建议,即在空闲时使其采用低转速模式,以省电。遗憾的是,在这些模式下,你不能访问DRAM和磁盘,无论访问速度有多低,你都必须返回全速工作模式才能进行读写。前面曾经提到,PC微处理器的设计考虑了一种更典型的情景:在高工作温度下密集使用。这种设计依靠片上温度传感器检测应当在什么时候自动减少。

(4)超频。Intel在2008年开始提供Turbo模式,在这种模式中,芯片可以判定在少数几个核上以较高时钟频率短时运行是安全的,直到温度开始上升为止。例如,3.3 GHz Core i7可以在很短的时间内以3.6GHz的频率运行。在执行单线程代码时,这些微处理器可以仅留下一个核,并使其以更高时钟频率运行,而其他所有核均被关闭。

注意,操作系统可以关闭Turbo模式,而且在启用时也没有通知,所以程序员可能会惊奇地发现,他们的程序可能会因为室温而发生性能变化。

尽管通常认为动态功耗是CMO中功耗的王要来源,但由于即使晶体管处于关闭状态也存在泄漏电流,所以静态功耗也逐渐成为一个重要问题:

功耗静态∝电流静态×电压

也就是说,静态功耗与器件数目成正比。

因此,如果增加晶体管的数目,那么即使它们处于空闲状态也会增加功耗,并且当晶体管的尺寸较小时,处理器中的泄漏电流会增大。所以,功耗极低的系统甚至会关闭非活动模块的电源(电源门控,power gating),以控制由泄漏电流导致的损失。2011年,泄漏目标是总功耗的25%,而高性能设计中的泄漏有时远远超过了这一目标。此类芯片的泄漏可能高达50%,部分原因是大型SRAM缓存需要电力来维持其存储值。(SRAM中的S表示“静态”,即static).停止泄漏的唯一手段就是关闭部分芯片的电源。

最后,由于处理器只是系统整体能耗中的一部分,所以如果使用一个速度较快但能效较低的处理器,使系统的其他部分能够进入睡眠模式,可能有助于降低整体能耗。这种策略被称为竞相暂停(race-to-halt)。

1.5.3 计算机体系结构因为能耗限制而发生的变化

随着晶体管发展速度的减缓,计算机架构师必须寻求其他提高能效的方法。事实上,在给定能耗预算的情况下,今天很容易设计出一种微处理器,其拥有的晶体管数多到不能同时全部开启。这种现象称为暗硅(dark silicon),这是因为在任意时刻,由于热限制,一个芯片的大部分都不能使用(“暗”)。这一观测结果使架构师们重新研究了处理器设计的基本原理,以寻求更高的能效。

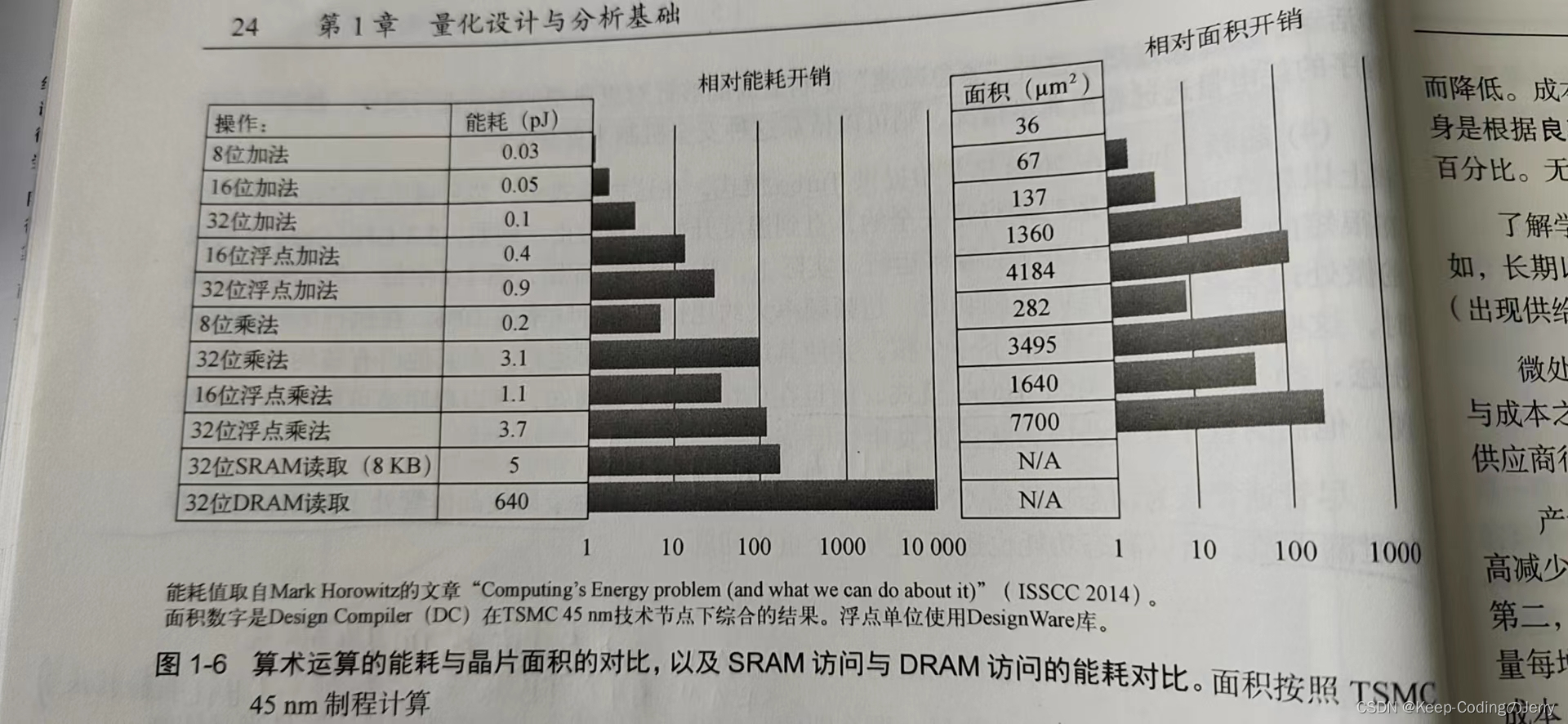

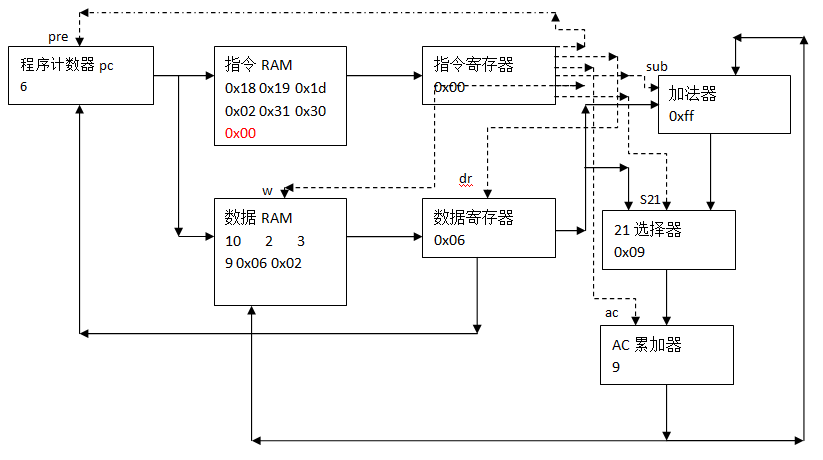

图1-6列出了现代计算机各组成模块的能耗开销和面积开销,它揭示的比率大得惊人。例如,一个32位浮点加法的能耗是一个8位整数加法的30倍。面积开销差异甚至更大,约为116倍。

但是,最大的差异在于存储器:DRAM读/写32比特的能耗是一次8位加法的约21333倍。一个小型SRAM的能效是DRAM的128倍,这充分表明了仔细选用缓存和存储缓冲区的重要性。