多比特信号跨时钟域同步处理

当在时钟域之间传递多比特数据时,普通的同步器并不能保证数据传递的安全性。在多时钟设计中,工程师往往容易犯一个错误,即同一事务处理含有需要从一个时钟域向另一个时钟域传递的多位跨时钟数据,并忽略了同步采样这些跨时钟位的重要性。

跨时钟域传递多比特信号的问题是,在同步多个信号到一个时钟域时将可能偶发数据变化歪斜(Skew),这种数据歪斜最终会在第二个时钟域的不同时钟上升沿上被采集。即便能够完美地控制和匹配这些多比特信号的走线长度,随着芯片衬底工艺不同,上升和下降的时间也会不一样,这些因素都会产生足够的歪斜导致在精心匹配的多条信号上采样失败。

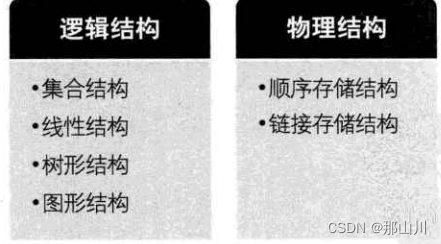

策略总结

为了避免这种多比特跨时钟域信号上的采样歪斜,需要掌握一些不一 样的策略。这些策略大致可以分为三种:

●多比特信号融合策略,即在可能的情况下,将多比特跨时钟域信号融合成单比特跨时钟域信号。

●多周期路径规划策略,即使用同步加载信号来安全地传递多比特跨时钟域信号。

●使用格雷码传递多比特跨时钟域信号。

多比特信号融合

只要有可能,就要将跨时钟域的多比特信号融合到单比特跨时钟域信号。设计中在碰到多比特需要跨时钟域时,可以先考虑是否真的需要多比特来控制逻辑跨越时钟边界?

下面通过一个例子来说明,只是简单地对多比特跨时钟域信号使用同步器并不一-定是足够好的一种解决方案。

如果这些控制信号的顺序或排列对于设计非常重要,那么设计者必须非常小心地将这些信号传递到新的时钟域。这一节给出的所有例子都比较简单,但它们所模仿的都是实际设计中出现的情况。

举例解决问题

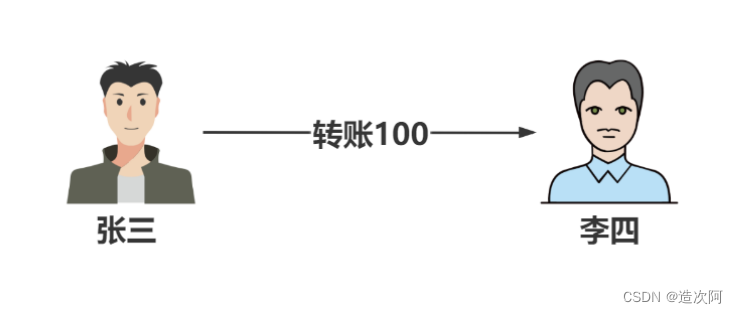

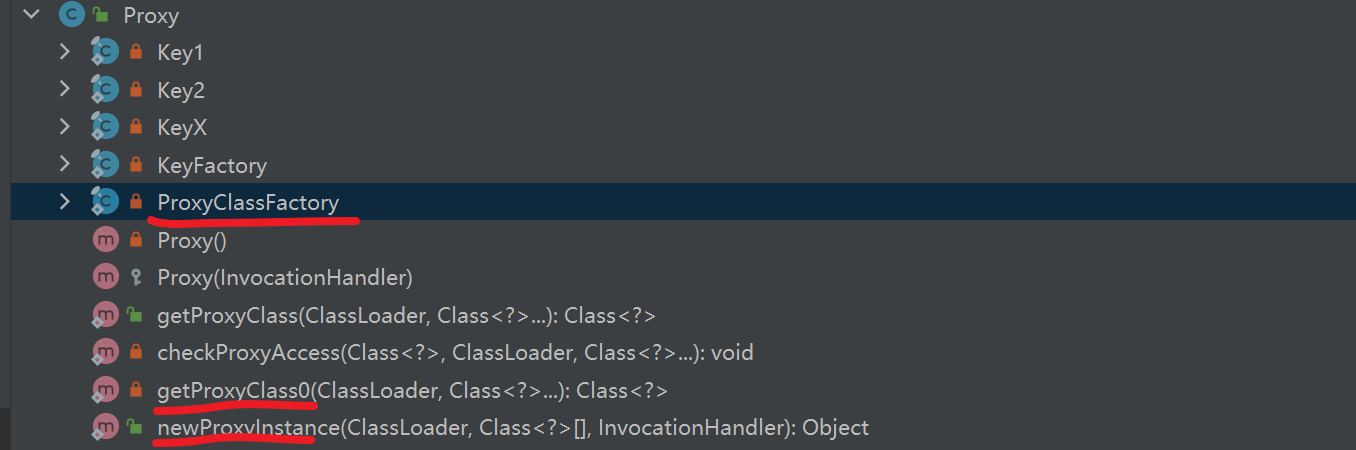

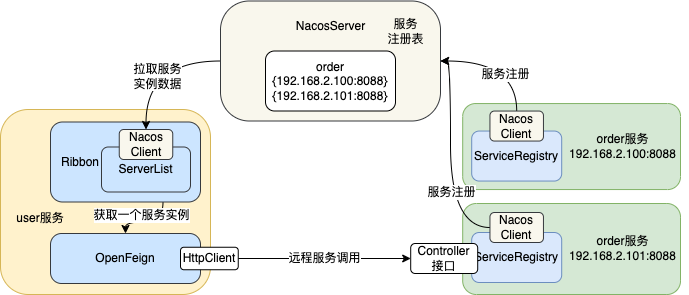

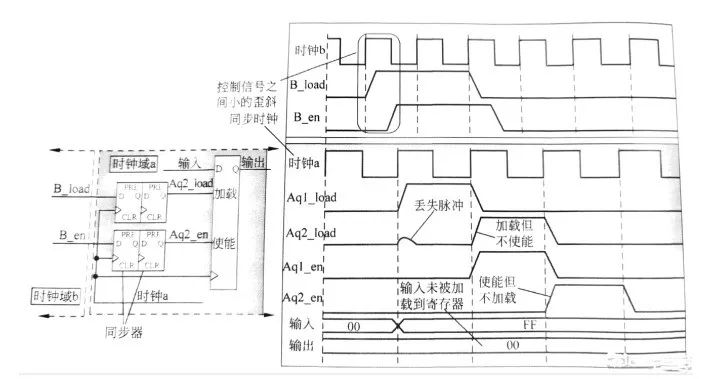

首先来看第一个例子,如图1所示,在接收时钟域有一个寄存器,它需要一个加载(Load)信号和一个使能(Enable)信号来加载一个数值到寄存器。如果加载和使能信号在发送时钟域的同一个时钟沿被驱动有效(即两个控制信号需要同时有效),那么这两个控制信号之间就有可能存在产生个小歪斜的机会,这就可能导致在接收时钟域中这两个信号被同步到不同的时钟周期。在这种情况下,数据是不能被加载到寄存器的。

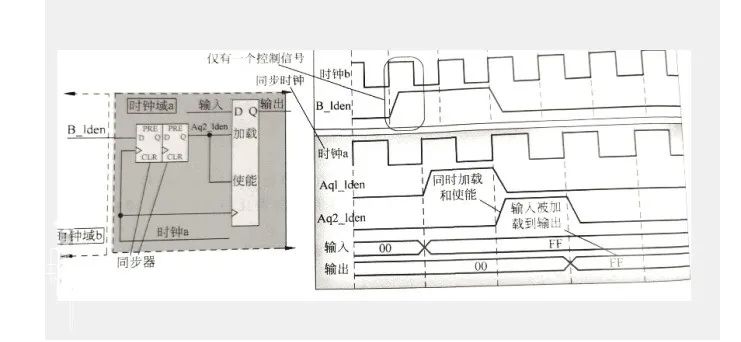

解决图1所示问问题的方法非常简单,就是将加载和使能两个控制信号融合成一个单比特控制信号(这两个控制信号本身相同,且同时有效),如图所示。单比特控制信号同步到接收时钟域后作为-个“加载使能"信号同时驱动寄存器的加载和使能输人端口,如此即可消除图1所示的潜在问题。

图1 多bit控制信号传递出现问题

图2 两个同时有效的控制信号融合成1个

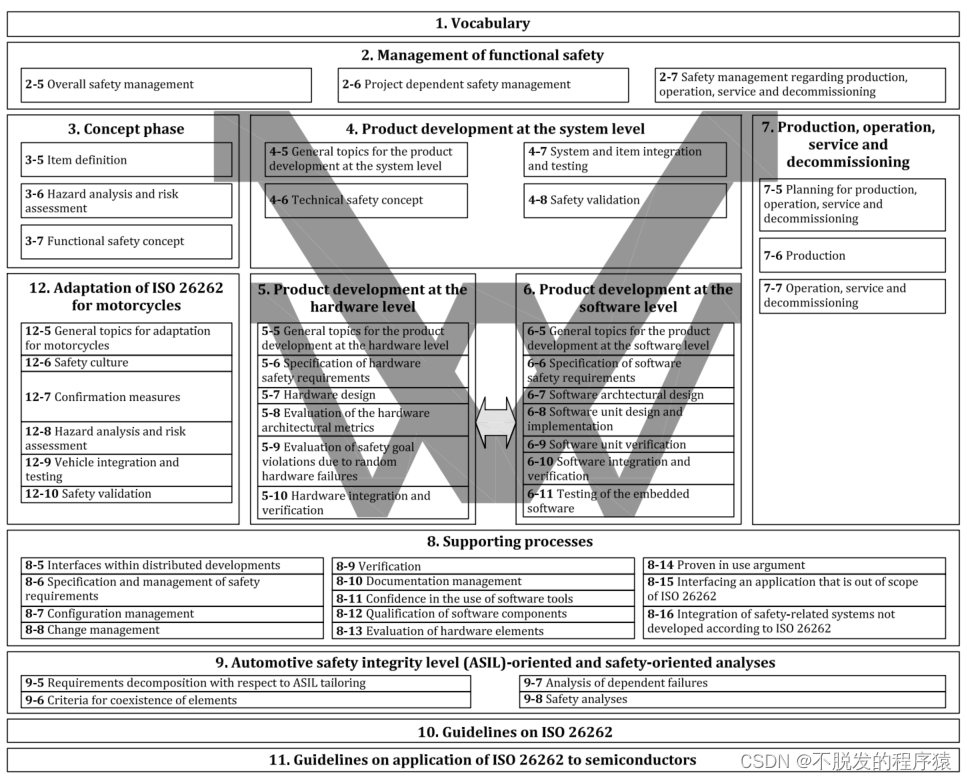

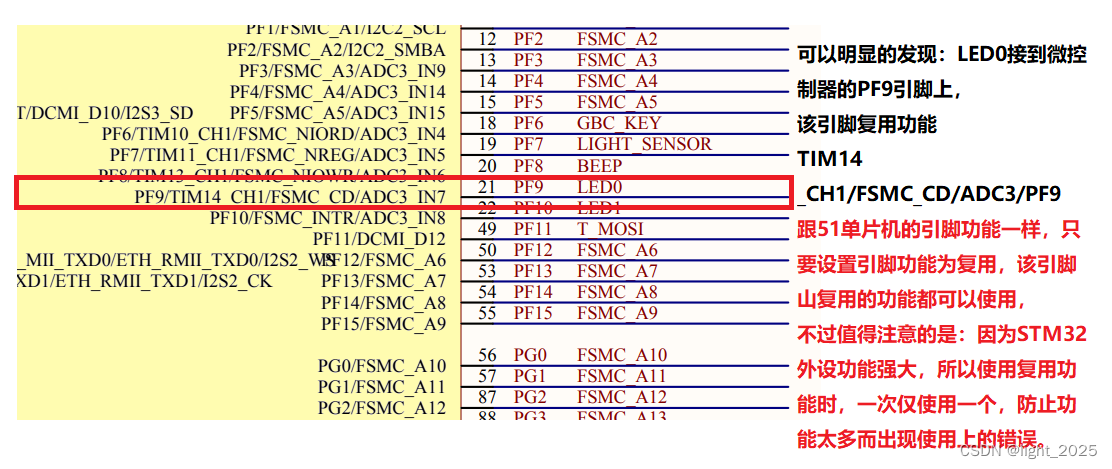

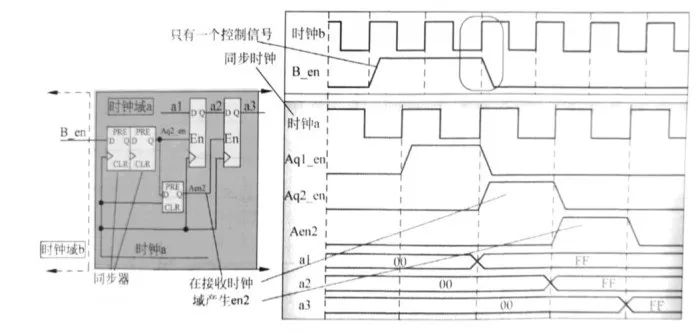

再来看第二个例子,如图3所示,在发送时钟域先后有两个使能信号(注意不同于之前的同时有效),同步到接收时钟域用于控制两级流水寄存器寄存数据。问题是在第一个时钟域中,B_enl控制信号正好稍微在Ben2有效前结束有效,这就导致在接收时钟域时钟上升沿采集Benl和B_en2脉冲时产生--个细微的缝隙。如图3所示,同步后两个使能控制信号间隔了两个时钟周期,而不是一个时钟周期。这样导致数据a2没有及时加载到第二个寄存器。这里需要注意的是,图中数据如果能一直保持有效,那么在间隔一个时钟周期后,数据还是会加载到第二个寄存器,但这里要求的是严丝合缝的流水操作,所以问题就出现了。图中第二个使能信号推迟了一个时钟周期,数据a2如果能够保持有效,应该在第二个使能有效的时候加载进第二个寄存器,图中a3并未显示出来。

图3 时钟域之间传递相继的控制信号问题

解决图3所示的问题,首先是在发送时钟域将两个使能控制信号融合为一个控制信号,其次是要增加一个额外的寄存器将同步后的使能控制信号寄存一拍,这样数据和控制信号形成匹配的流水,如图4所示。这种处理方式在HDL(Hardware Description Languimur硬件描述语言)代码设计时非常简单,就是将同步后的控制信号在同步时钟城寄存一拍来产生第二级寄存器的使能信号。

图4在新时钟域中使用逻辑产生第二级寄存器使能信号