目录

- 一、 任务介绍

- 二、基本原理

- 三、基于FPGA实现BPSK 调制

- 四、源码

一、 任务介绍

BPSK 调制在数字通信系统中是一种极重要的调制方式,它的抗干扰噪声性能及通频带的利用率均优先于 ASK 移幅键控和 FSK 移频键控。因此,PSK 技术在中、高速数据传输中得到了十分广泛的应用。

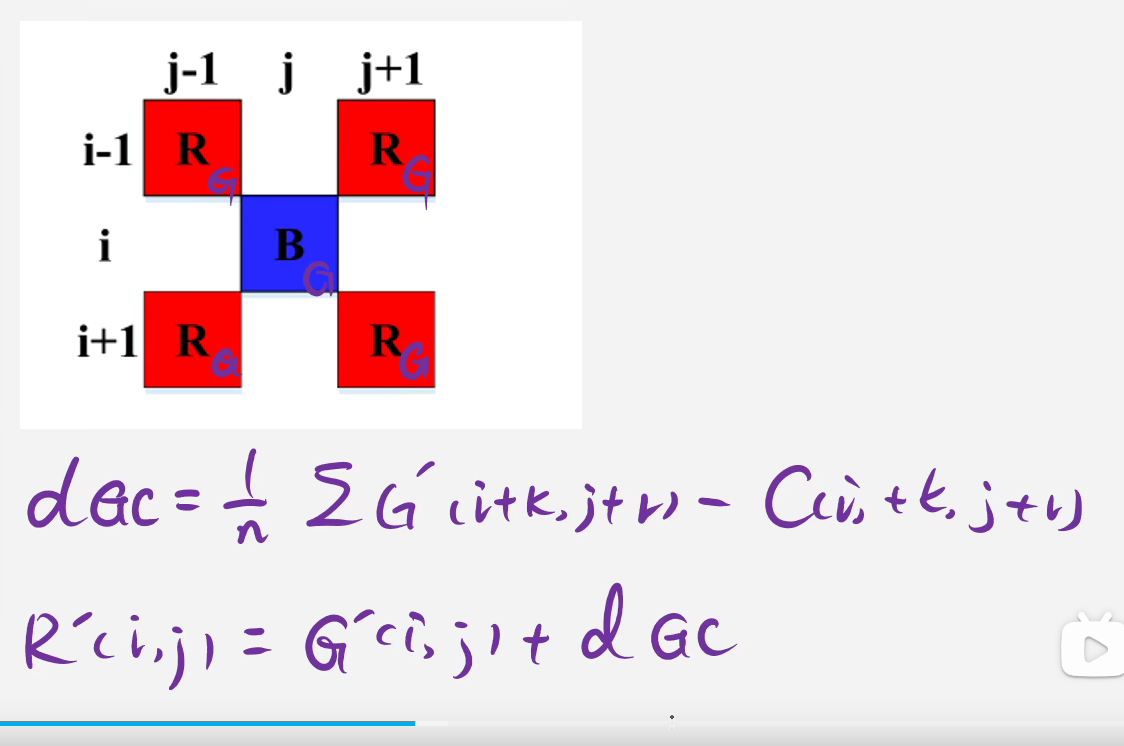

二、基本原理

PSK 信号是用载波相位的变化表征被传输信息状态的,通常规定 0 相位载波和π相位载波分别代表传 1 和传 0,其时域波形示意图如图 2-1 所示。设二进制单极性码为 an,其对应的双极性二进制码为 bn,则 BPSK 信号的一般时域数学表达式为:

由(2-1)式可见,BPSK 信号是一种双边带信号我们知道,BPSK 信号是用载波的不同相位直接去表示相应的数字信号而得出的,在这种绝对移相的方式中,由于发送端是以某一个相位作为基准的,因而在接收系统也必须有这样一个固定基准相位作参考。如果这个参考相位发生变化,则恢复的数字信息就会与发送的数字信息完全相反,从而造成错误的恢复。这种现象常称为 BPSK 的“倒π”现象,因此,实际中一般不采用 BPSK 方式,而采用差分移相(2DPSK)方式。

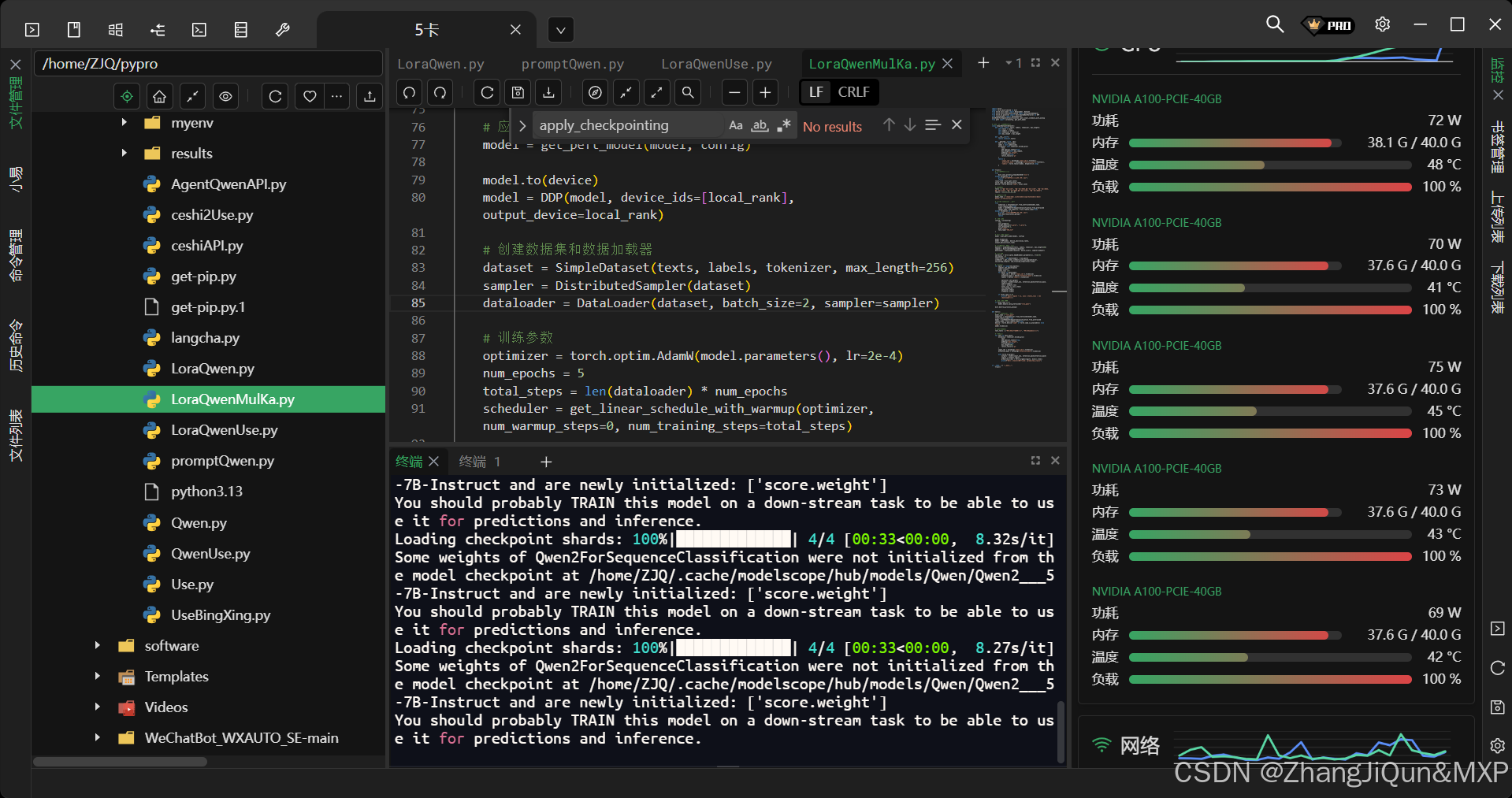

三、基于FPGA实现BPSK 调制

1、 创建工程文件,选择对应 BYS3 的型号;

2、添加一个顶层文件;

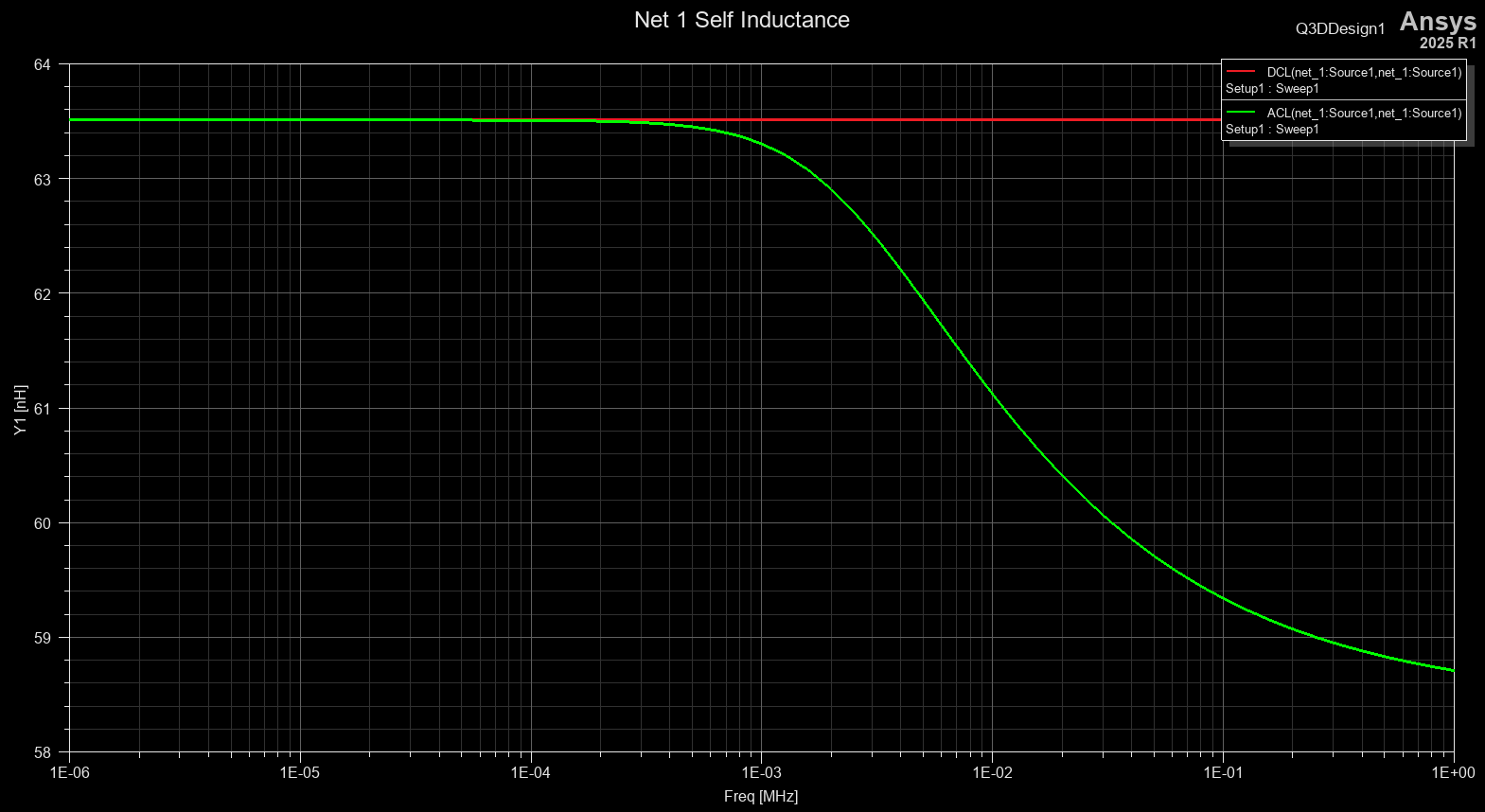

3、 创建一个 RAM IP 核用来存放 DDS 数据,此步骤为 DDS 的使用;

4、添加相应matlab生成的coe 文件;

5、 IP 核创建完成后,进行离线仿真验证 IP 核,创建一个仿真文件:找到 Simulation 目录,右击刚刚创建的仿真文件,选择 Set as Top,找到生成的 IP 核,复制框选的代码,作为例化的模板;将 IP 核例化到仿真文件中,再添加测试的模拟时钟和地址累加,如下图可以看到 douta 的正弦波波形;单载波离线仿真完成。

6、接下来创建约束 XDC 文件,代码在实验代码部分;

7、逻辑分析仪的使用,先点击 run synthesis 结束没有报错后 点开 Open

synthesis 再点击 Set Up DeBug,确认信号线都已添加;

8、添加完成后点击生成 bit,再点击 program devic,选择芯片,最后点击 program;

9、点击 run 出现波形,片上示波器使用步骤完成:

四、源码

veirilog HDL TOP 层代码代码:

module BPSK(

input clk, input reset, output sclk, //AD

output cs_n, //AD

output led, input sdata, //AD

output sinout1,//DA

output sync_n, //DA

output sysclk,//DA

output sinout2

);

reg [7:0]addr;

wire [7:0] sin;

reg clk_10m;

reg [1:0] cont;

wire [7:0] data;

sin sin_rom (

.clka(clk_10m), // input wire clka

.ena(1'b1), // input wire ena

.addra(addr), // input wire [7 : 0] addra

.douta(sin) // output wire [7 : 0] douta

);

always @(negedge clk_10m)

if(~reset)

addr <= 0;

else //if(sync_n==1)

addr <= addr + 1500;

clk_freq clk_freq(

.clk(clk),

.rst_n(reset),

.clk_10m(clk_10m)

);

always @(negedge clk or negedge reset)

begin

if(!reset)

cont <=0;

else

cont <=cont+2'b01;

end

adc_adc081s021 adc_adc081s021(

cs_n,sclk,data, cont[1], reset,sdata

);

DAC_deltasigma DAC_deltasigma

(

.DACout(sinout2),

.DACin(sin), // .DACin(data),

.Clk(clk_10m),

.Reset(reset)

);

DAC_dac081s101 DAC_dac081s101

(

.DACout(sinout1),

.sync_n(sync_n),

.DACin(sin),

.Clk(clk_10m),

.Reset(reset),

.sysclk(sysclk)

);

PN 码

reg [24:0]cnt;

wire pn_clk;

wire pn_out;

always @(negedge clk_10m) //时钟四分频

begin

if(~reset)

cnt<=0;

else

cnt<=cnt+1;

end

assign pn_clk =cnt[1];

code_gen U_code_gen(

.clk(clk_10m),

.grst_n(reset),

.ms_flag(1'b0),

.num(6'b000110),

.pn_clk(pn_clk),

.pn_out(pn_out)

);

reg [7:0] bpsk;

always @(negedge clk_10m)

bpsk<= pn_out?(~sin):sin;

assign led = &(pn_out|bpsk|sin);

endmodule

adc_adc081s021 模块代码:

module adc_adc081s021(

cs_n,sclk, data, clk, reset, sdata

);

output sclk;

output cs_n;

output [7:0] data;

input clk;

input reset;

input sdata;

reg sclk;

reg cs_n;

reg count;

reg [4:0] bits;

reg [7:0] data;

always @(negedge clk or negedge reset)

begin

if(!reset)

begin

count<=0;

end

else

begin

count<=count+1;

end

end

always @(negedge clk or negedge reset)

begin

if(!reset)

begin

sclk<=0;

end

else

begin

if(count==1)

sclk<=~sclk;

end

end

always @(negedge sclk or negedge reset)

begin

if(!reset)

begin

cs_n<=1'b1;

data<=0;

bits<=0;

end

else

case(bits)

5'd0:

begin

if(cs_n)

begin

bits <= 5'd0;

cs_n <=0;

end

else

bits <= 5'd1;

end

5'd1:

begin

bits <= 5'd2;

cs_n<=1'b0;

end

5'd2:

begin

bits <= 5'd3;

cs_n<=1'b0;

end

5'd3:

begin

bits <= 5'd4;

cs_n <= 1'b0;

end

5'd4:

begin

data[7]<= sdata;

bits <= 5'd5;

cs_n<=1'b0;

end

5'd5:

begin

data[6]<= sdata;

bits <= 5'd6;

cs_n<=1'b0;

end

5'd6:

begin

data[5]<= sdata;

bits <= 5'd7;

cs_n <=1'b0;

end

5'd7:

begin

data[4]<= sdata;

bits <= 5'd8;

cs_n <=1'b0;

end

5'd8:

begin

data[3]<= sdata;

bits <= 5'd9;

cs_n <=1'b0;

end

5'd9:

begin

data[2]<= sdata;

bits <= 5'd10;

cs_n <= 1'b0;

end

5'd10:

begin

data[1]<= sdata;

bits <= 5'd11;

cs_n <= 1'b0;

end

5'd11:

begin

data[0]<= sdata;

bits <= 5'd12;

cs_n<=1'b0;

end

5'd12:

begin

bits <= 5'd13;

cs_n<=1'b0;

end

5'd13:

begin

bits <= 5'd14;

cs_n<=1'b0;

end

5'd14:

begin

bits <= 5'd15;

cs_n<=1'b0;

end

5'd15:

begin

bits <= 5'd16;

cs_n<=1'b1;

end

5'd16:

begin

bits <= 5'd17;

cs_n<=1'b1;

end

5'd17:

begin

bits <= 5'd18;

cs_n<=1'b1;

end

5'd18:

begin

bits <= 5'd19;

cs_n<=1'b1;

end

5'd19:

begin

bits <= 5'd0;

cs_n<=1'b1;

end

endcase

end

endmodule

DAC_deltasigma 模块代码:

`define MSBI 7

module DAC_deltasigma(DACout, DACin, Clk, Reset);

output DACout; // This is the average output that feeds low pass filter

reg DACout; // for optimum performance, ensure that this ff is in IOB

input [`MSBI:0] DACin; // DAC input (excess 2**MSBI)

input Clk;

input Reset;

reg [`MSBI+2:0] DeltaAdder; // Output of Delta adder

reg [`MSBI+2:0] SigmaAdder; // Output of Sigma adder

reg [`MSBI+2:0] SigmaLatch; // Latches output of Sigma adder

reg [`MSBI+2:0] DeltaB; // B input of Delta adder

always @(SigmaLatch) DeltaB = {SigmaLatch[`MSBI+2], SigmaLatch[`MSBI+2]} << (`MSBI+1);

always @(DACin or DeltaB) DeltaAdder = DACin + DeltaB;

always @(DeltaAdder or SigmaLatch) SigmaAdder = DeltaAdder + SigmaLatch;

always @(posedge Clk or negedge Reset)

begin

if(!Reset)

begin

SigmaLatch <= 1'b1 << (`MSBI + 1);

DACout <= 1'b0;

end

else

begin

SigmaLatch <= SigmaAdder;

DACout <= SigmaLatch[`MSBI+2];

end

end

endmodule

DAC_dac081s101 模块代码:

module DAC_dac081s101(

DACout, sync_n, DACin,

Clk, Reset, sysclk

);

output DACout; // This is the average output that feeds low pass filter

output sync_n;

reg DACout; // for optimum performance, ensure that this ff is in IOB

reg sync_n;

output sysclk;

input [7:0] DACin;

input Clk;

input Reset;

//reg [15:0] reg1;

reg [3:0] bits;

reg sysclk;

always @(negedge Clk or negedge Reset)

begin

if(~Reset)

begin

sysclk <= 0;

end

else

sysclk<=~sysclk;

end

always @(negedge sysclk or negedge Reset)

begin

if(!Reset)

begin

bits <= 4'b0;

DACout <= 1'b0;

sync_n<=1'b1;

end

else

case(bits)

4'd0:

begin

DACout <= 0;

if(sync_n)

begin

bits <= 4'd0;

sync_n <=0;

end

else

bits <= 4'd1;

end

4'd1:

begin

DACout <= 0;

bits <= 4'd2;

sync_n<=1'b0;

end

4'd2:

begin

DACout <= 0;

bits <= 4'd3;

sync_n<=1'b0;

end

4'd3:

begin

DACout <= DACin[7];

//DACout <= 0;

bits <= 4'd4;

sync_n<=1'b0;

end

4'd4:

begin

DACout <= DACin[6];

// DACout <= 0;

bits <= 4'd5;

sync_n<=1'b0;

end

4'd5:

begin

DACout <= DACin[5];

bits <= 4'd6;

sync_n<=1'b0;

end

4'd6:

begin

DACout <= DACin[4];

bits <= 4'd7;

sync_n<=1'b0;

end

4'd7:

begin

DACout <= DACin[3];

bits <= 4'd8;

sync_n<=1'b0;

end

4'd8:

begin

DACout <= DACin[2];

bits <= 4'd9;

sync_n<=1'b0;

end

4'd9:

begin

DACout <= DACin[1];

bits <= 4'd10;

sync_n<=1'b0;

end

4'd10:

begin

DACout <= DACin[0];

bits <= 4'd11;

sync_n<=1'b0;

end

4'd11:

begin

// DACout <= DACin[0];

DACout <= 0;

bits <= 4'd12;

sync_n<=1'b0;

end

4'd12:

begin

// DACout <= DACin[0];

DACout <= 0;

bits <= 4'd13;

sync_n<=1'b0;

end

4'd13:

begin

DACout <= 0;

bits <= 4'd14;

sync_n<=1'b0;

end

4'd14:

begin

DACout <= 0;

bits <= 4'd15;

sync_n<=1'b0;

end

4'd15:

begin

DACout <= 0;

bits <= 4'd0;

sync_n<=1'b1;

end

endcase

end

endmodul