写在前面

在自己准备写一些简单的verilog教程之前,参考了许多资料----asic-world网站的这套verilog教程即是其一。这套教程写得极好,奈何没有中文,在下只好斗胆翻译过来(加了自己的理解)分享给大家。

这是网站原文:http://asic-world.com/verilog/veritut.html

这是系列导航:Verilog教程系列文章导航

简介

作为 Verilog初学者,您可能想尝试一些例子和新的东西。我列出了可用于实现此目的的工具流程。这个流程我亲自尝试过,它对我来说效果很好。在这里,我只采用了工具流程的前端设计部分和部分 FPGA 设计,这套流程无需在工具上花费大量资金即可完成。

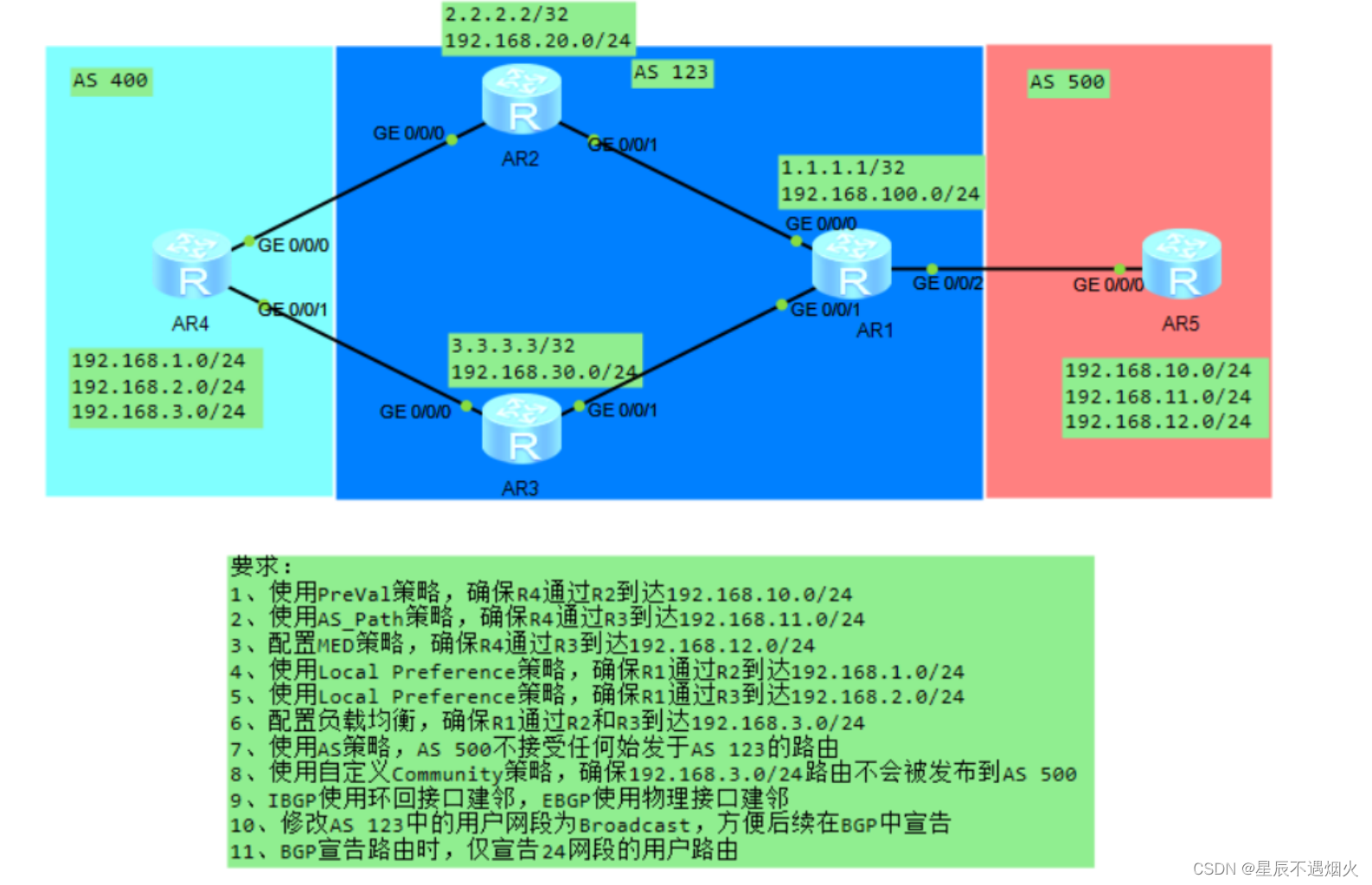

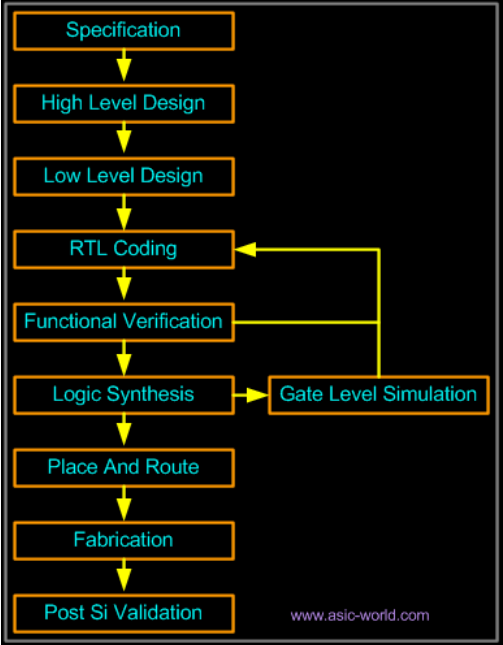

ASIC/FPGA设计的各个阶段

这是各个设计阶段可以使用的工具。

- 规格书(Specification ):文字处理器,如 Word、Kwriter、AbiWord、Open Office。

- 高层级设计(High Level Design):文字处理器,如 Word、Kwriter、AbiWord,用于绘制波形使用工具,如 waveformer 或 testbencher 或 Word,Open Office。

- 低层级设计(Micro Design/Low level design): Word、Kwriter、AbiWord 等字处理器,用于绘制波形使用工具,如 waveformer 或 testbencher 或 Word。

- RTL 编码(RTL Coding): Vim、Emacs、conTEXT、HDL TurboWriter

- 仿真(Simulation ): Modelsim、VCS、Verilog-XL、Veriwell、Finsim、Icarus。

- 综合(Synthesis):设计编译器、FPGA 编译器、Synplify、Leonardo Spectrum。您可以从 Altera 和 Xilinx 等 FPGA 供应商处免费下载。

- 布局布线(Place & Route):对于 FPGA,使用 FPGA 供应商的 P&R 工具。ASIC 工具需要像 Apollo 这样昂贵的 P&R 工具。学生可以使用LASI、Magic。

- 后仿真(Post Si Validation):对于ASIC和FPGA,芯片需要在真实环境中进行测试。电路板设计,设备驱动需要到位。

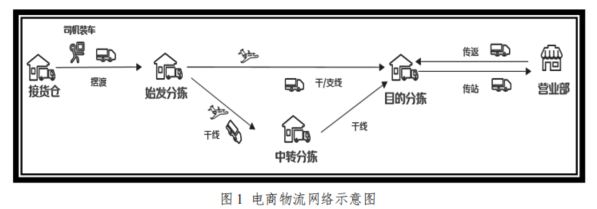

这是一张典型的设计流程图:

规格书

这是定义您预期设计的系统/设计的重要参数的阶段。一个简单的例子是:我想设计一个计数器----它应该是 4 位宽,应该有同步复位,高电平有效使能;当复位激活时,计数器输出应变为“0”。

高层级设计

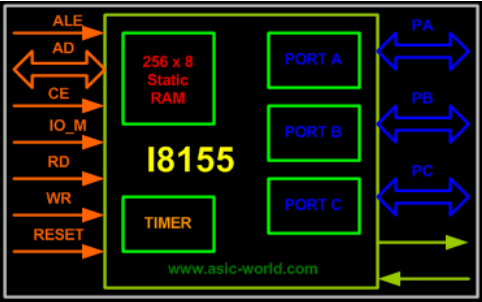

这是您在设计中定义各种子模块以及它们如何通信的阶段。假设我们需要设计一个微处理器:高层级设计意味着根据功能将设计分成多个子模块---寄存器、ALU、指令解码、内存接口等。

低层级设计

低层级设计是设计人员描述如何实现每个子模块的阶段。它包含状态机、计数器、多路复用器、解码器、内部寄存器的详细信息。在各种界面绘制波形是一个好主意。这是个人花费大量时间的阶段。

RTL编码

在 RTL 编码中,使用设计语言的可综合结构将低层级设计转换为 Verilog/VHDL 代码。我们通常喜欢在开始验证或综合之前检查代码。

module addbit (

a , // first input

b , // Second input

ci , // Carry input

sum , // sum output

co // carry output

);

//Input declaration

input a;

input b;

input ci;

//Ouput declaration

output sum;

output co;

//Port Data types

wire a;

wire b;

wire ci;

wire sum;

wire co;

//Code starts here

assign {co,sum} = a + b + ci;

endmodule // End of Module addbit仿真

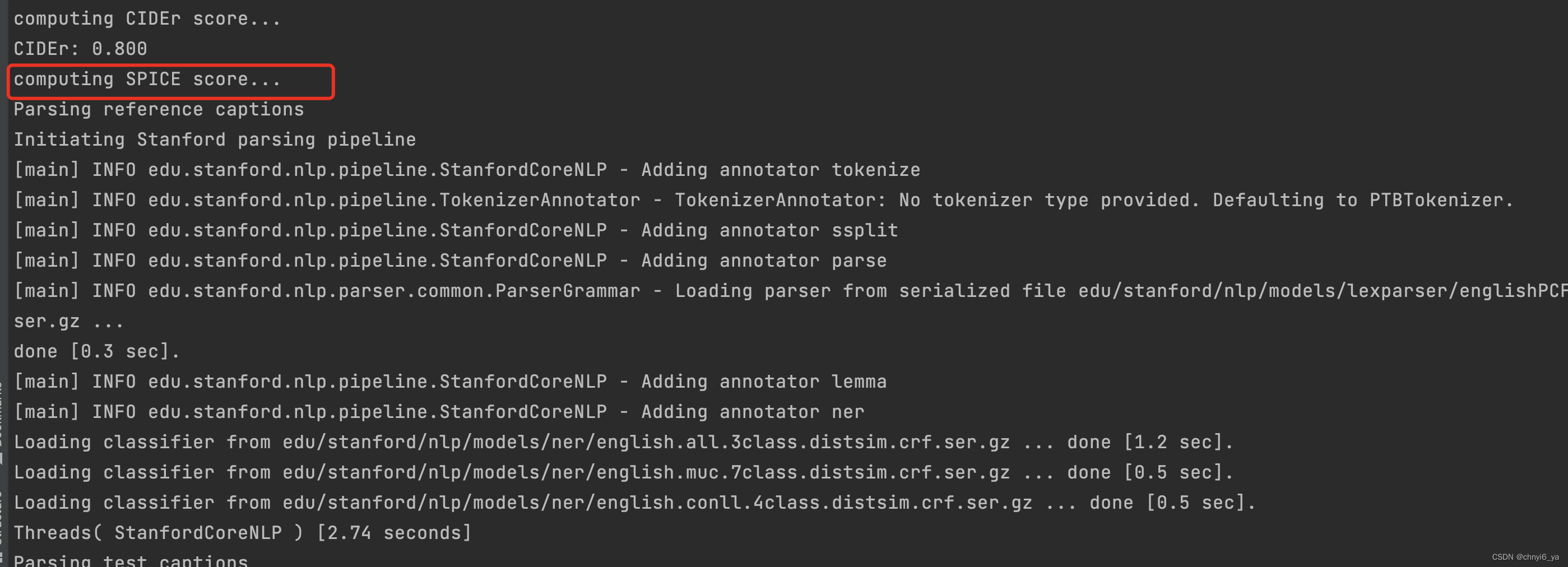

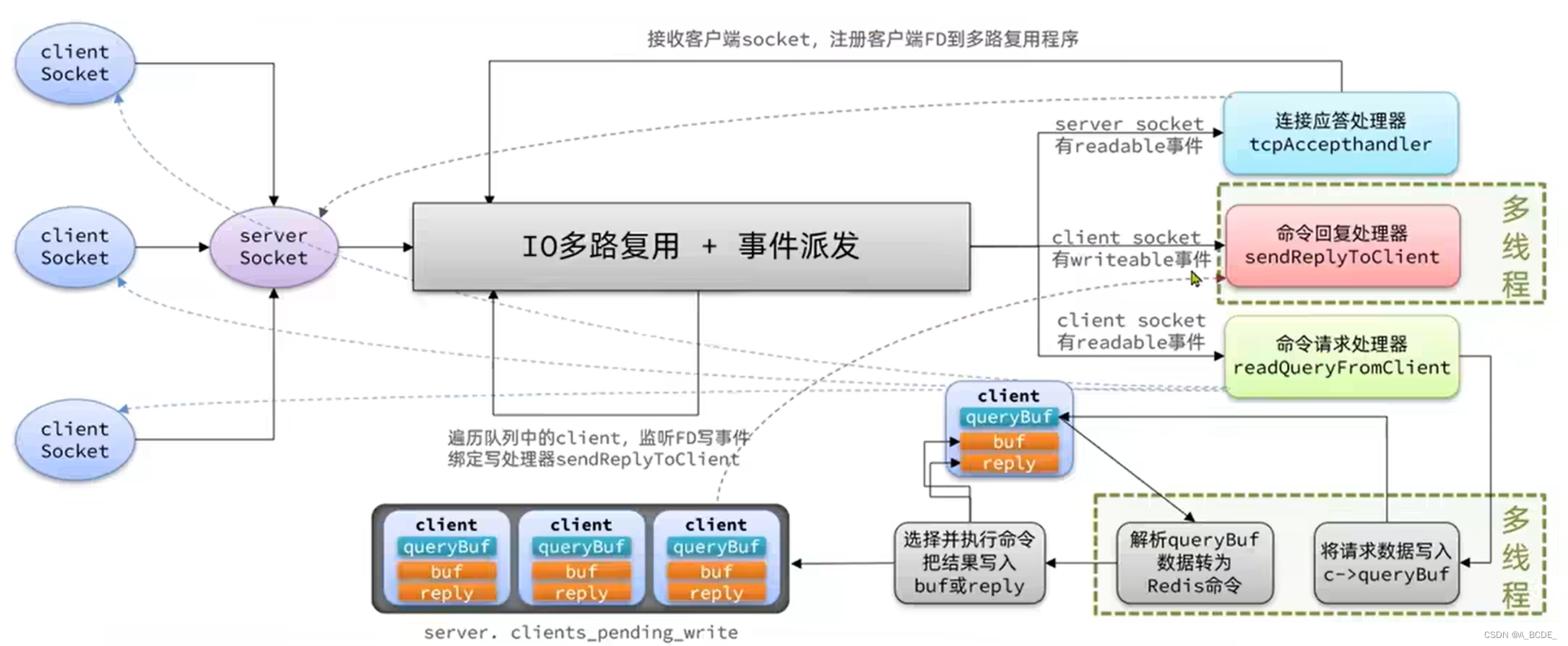

仿真是在任何抽象级别验证模型功能特性的过程。我们使用仿真工具来仿真硬件模型。要测试 RTL 代码是否满足规范的功能要求,我们必须查看所有 RTL 模块是否功能正确。为了实现这一点,我们需要编写一个testbench,它生成时钟、复位和所需的测试向量。计数器的示例testbench如下所示。通常我们将 60-70% 的时间花在设计验证上。

我们使用仿真工具的波形输出来查看 DUT(Device Under Test,被测设备)在功能上是否正确。大多数仿真工具都带有波形查看器。随着设计变得复杂,我们可以编写自检式testbench,自动将 DUT 的输出与预期值进行比较。

还有一种仿真叫做时序仿真,是在综合之后或者布局布线之后进行的。此处包括门延迟和线延迟,以查看 DUT 是否能以额定时钟工作。这也称为SDF(Standard Delay Format,标准延迟格式) 仿真或门级仿真。

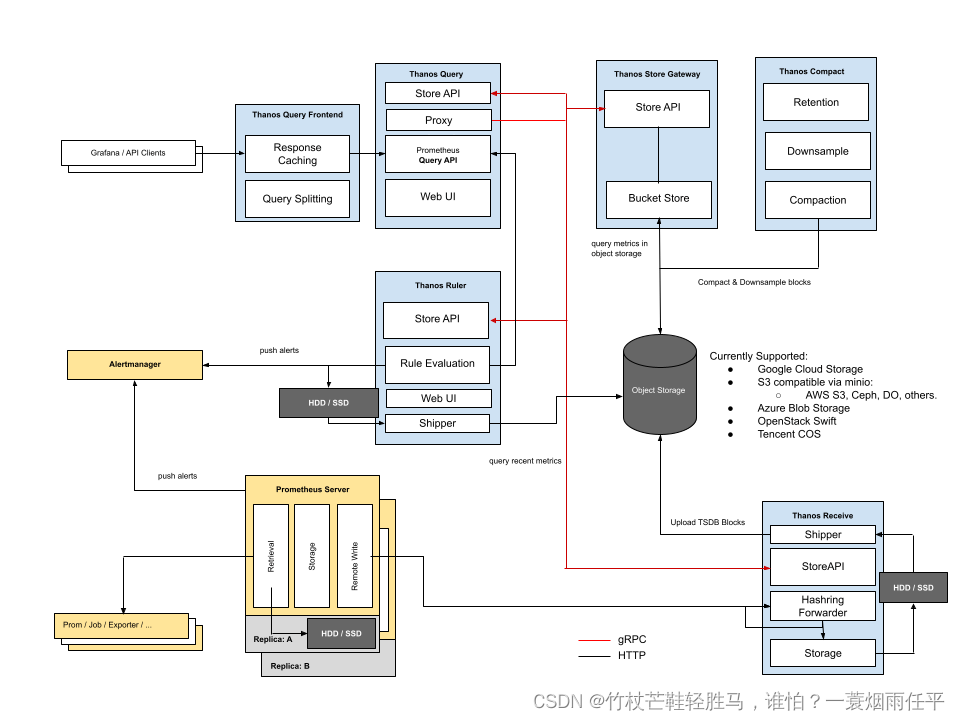

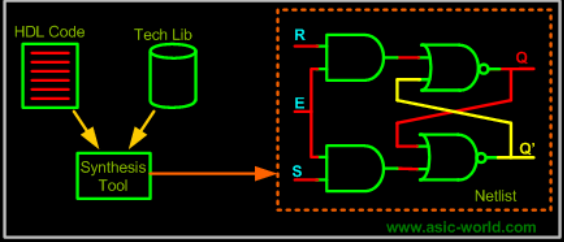

综合

综合是综合工具将 Verilog 或 VHDL 中的 RTL、目标技术和作为输入的约束并将 RTL 映射到目标技术原语的过程。综合工具在将 RTL 映射到门之后,还会进行最少量的时序分析,以查看映射的设计是否满足时序要求。(需要注意的重要一点是,综合工具不知道线延迟,它们只知道门延迟)。

综合之后,在将网表传递到后端(放置和布线)之前通常需要做几件事:

- 形式验证(Formal Verification):检查 RTL 到门的映射是否正确

- 扫描插入(Scan insertion):在ASIC的情况下插入扫描链

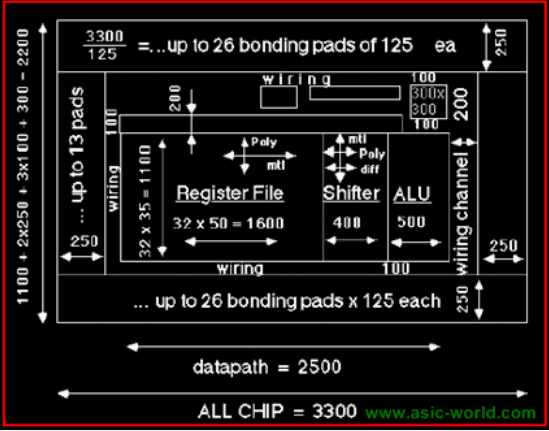

布局布线

来自综合工具的门级网表被提取并以 Verilog 网表格式导入到布局布线工具中。所有的门和触发器会被放置(布局);时钟树被综合和复位被布线。在此之后,每个子模块都被布线。P&R 工具输出是一个 GDS 文件,代工厂使用它来制造 ASIC。后端团队通常将 SPEF(标准寄生交换格式)/RSPF(减少寄生交换格式)/DSPF(详细寄生交换格式)从 ASTRO 等布局工具转储给前端团队,然后前端团队使用 Prime Time 等工具中的 read_parasitic 命令来写出 SDF(标准延迟格式)用于门级仿真目的。

后仿真

芯片(硅)从晶圆厂返回后,需要将其置于真实环境中并进行测试,然后才能投放市场。由于 RTL 的仿真速度(每秒时钟数)非常慢,因此总是有可能在后仿真过程中发现错误。

- 📣您有任何问题,都可以在评论区和我交流📃!

- 📣本文由 孤独的单刀 原创,首发于CSDN平台🐵,博客主页:wuzhikai.blog.csdn.net

- 📣您的支持是我持续创作的最大动力!如果本文对您有帮助,还请多多点赞👍、评论💬和收藏⭐!